# RTE-V850E/MA1-CB

USER'S MANUAL (Rev. 1.05)

# **REVISION HISTORY**

| Date             | Revision | Chapter | Explanation of revision                                  |

|------------------|----------|---------|----------------------------------------------------------|

| May 12, 1999     | 0.50     |         | Preliminary version: Supported by experimental board     |

| July 19, 1999    | 1.00     |         | Official version: Supported by mass-produced model       |

| August 13, 1999  | 1.01     | 11.3    | Addition of resources of RTE-MB-A                        |

| January 17, 2000 | 1.02     | 7.2.1   | Reviced RFS1 Value: 0x0024/0016 -> 0x8024/8016           |

| February 3, 2000 | 1.03     | 7.2.1   | Reviced RFS1 Value: 0x8024/8016 -> 0x8017/800F           |

| Jun 11, 2001     | 1.04     | 7.4.9   | Add Word accessing to G-Bus function                     |

| Oct 25, 2001     | 1.05     | 7.2.1   | Reviced ASC comments: all 0 addr wait -> all 1 addr wait |

# **CONTENTS**

| 1. | INTRO          | DDUCTION                                                                        |     |

|----|----------------|---------------------------------------------------------------------------------|-----|

|    | 1.1.           | NUMERIC NOTATION                                                                | 1   |

| 2. | FUNC           | TIONS                                                                           | 2   |

| 3. | MAJO           | R FEATURES                                                                      | 3   |

| 4. | BASIC          | SPECIFICATIONS                                                                  | 3   |

| 5. | BOAR           | D CONFIGURATION                                                                 |     |

|    | 5.1.           | RESET SWITCH (SW_RESET)                                                         |     |

|    | 5.2.           | POWER CONNECTOR (JPOWER)                                                        |     |

|    | 5.3.           | SWITCH 1 (SW1)                                                                  |     |

|    | 5.4.           | SWITCH 2 (SW2)                                                                  |     |

|    | 5.5.           | SWITCH 3 (SW3)                                                                  |     |

|    | 5.6.           | SWITCH 4 (SW4)                                                                  |     |

|    | 5.7.           | SWITCHES 5 TO 8 (SW5 TO SW8)                                                    |     |

|    | 5.8.           | 7SEG-LED, xxx-LED                                                               |     |

|    | 5.9.           | TEST PINS FOR ROM EMULATOR (JROM-EM1)                                           |     |

|    | 5.10.          | CLOCK SOCKET (OSC1)                                                             |     |

|    | 5.11.          | CRYSTAL SOCKET (JP1)                                                            |     |

|    | 5.12.          | AVDD/AVREF SELECTOR JUMPER (JP2)                                                |     |

|    | 5.13.          | ROM SOCKETS  SELF-WRITING POWER CONNECTOR (JVPP)                                |     |

|    | 5.14.<br>5.15. | FLASH WRITING CONNECTOR (JFLASH) The JFLASH connector is used to write          | 9   |

|    |                | the CPU's internal flash ROM by using a flash programmer device. To use JFLASH, |     |

|    |                | nust be set (see Section 5.6).                                                  | 10  |

|    | 5.16.          | SERIAL CONNECTOR (JSIO1, JSIO2)                                                 |     |

|    | 5.17.          | JGBUS CONNECTOR (JGBUS)                                                         |     |

|    | 5.17.          | CPU CONNECTOR (JCPU1, JCPU2)                                                    |     |

|    |                |                                                                                 |     |

| 6. |                | ECTION WITH THE HOST PC                                                         |     |

|    | 6.1.           | RS-232C CONNECTION                                                              | .14 |

| 7. | HARD           | WARE REFERENCES                                                                 |     |

|    | 7.1.           | MEMORY AND I/O MAP                                                              | .15 |

|    | 7.2.           | RECOMMENDED SETTINGS                                                            |     |

|    |                | 7.2.1. MEMC Registers                                                           |     |

|    | 7.3.           | MEMORY RESOURCES                                                                |     |

|    |                | 7.3.1. SDRAM (CS1: 0800000 to 3FFFFFF)                                          |     |

|    |                | 7.3.2. SRAM (CS2: 0400000 to 07FFFFF)                                           |     |

|    |                | 7.3.3. UV-EPROM (CS0: 00000000 to 03FFFFF)                                      |     |

|    | 7.4.           | I/O MAP                                                                         |     |

|    |                | 7.4.1. I/O List                                                                 |     |

|    |                | 7.4.2. SW1 Read Port (SW1 7800000H [Read Only])                                 |     |

|    |                | 7.4.3. SW2 Read Port (SW2 7801000H [Read Only])                                 | .19 |

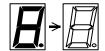

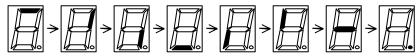

|     |                  | 7.4.4. 7-Segment LED Display Data Output Port (7SEG-LED 7802000H [Write               | Only])20 |

|-----|------------------|---------------------------------------------------------------------------------------|----------|

|     |                  | 7.4.5. Time-Over Ready LED Clear Pulse (TOVRDY_LED_CLRPLS 7803000F                    | -        |

|     |                  | Only])                                                                                |          |

|     |                  | 7.4.6. Interrupt Controller (PIC: 7804000H to 7804020H [Read/Write])                  |          |

|     |                  | 7.4.7. UART (TL16C550C: 7807000H to 7807070H)                                         |          |

|     |                  | 7.4.8. TIC (μPD71054 7808000H to 7808030FH)                                           |          |

|     |                  | 7.4.9. GBUS ACCESS CONTROL (7809000H [Read/Write])                                    | 23       |

| 8.  | SOFT             | WARE                                                                                  | 24       |

|     | 8.1.             | INITIALIZATION                                                                        | 24       |

|     | 8.2.             | SUCCESSIVE ACCESSES TO mPD71054                                                       | 24       |

|     | 8.3.             | LIBRARIES                                                                             |          |

|     | 8.4.             | EXAMPLE OF USING TIMERS                                                               | 25       |

| 9.  | DEVEL            | LOPMENT OF APPLICATIONS USING MASKABLE INTERRUPTS                                     | 26       |

|     | 9.1.             | INTERRUPT VECTOR                                                                      |          |

|     | 9.2.             | GENERAL RESTRICTIONS/NOTES                                                            |          |

|     | 9.3.             | REWRITING THE ALTERNATE VECTOR AREA DURING DOWNLOADING                                |          |

|     | 9.4.             | RESTRICTIONS/NOTES ON BREAKPOINTS                                                     |          |

|     |                  |                                                                                       |          |

| 10. |                  | PIN CONNECTION                                                                        |          |

|     | 10.1.            | PIN CONNECTION LIST                                                                   |          |

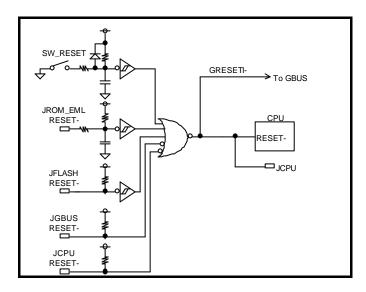

|     | 10.2.            | RESET-                                                                                |          |

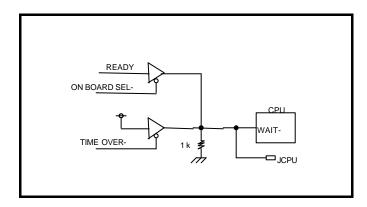

|     | 10.3.            | PCM0/WAIT0                                                                            |          |

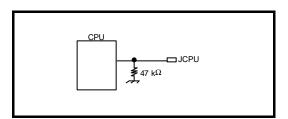

|     | 10.4.            | PCM5/SELFREF                                                                          |          |

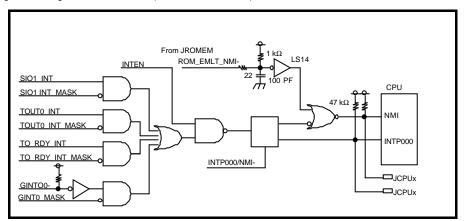

|     | 10.5.            | P20/NMI, P1/INTP000                                                                   |          |

|     | 10.6.<br>10.7.   | P2/INTP001, P11/INTP010, P12/INTP011, P21/INTP020<br>P40/S00/TXD0                     |          |

|     |                  |                                                                                       |          |

|     | 10.8.            | P41/SI0/RXD0                                                                          |          |

|     | 10.9.<br>10.10.  | P42/SCK0-, P43/SO1/TXD1, P44/SI1/TXD0, P45/SCK1<br>P4/INTP100/DMARQ0P7/INTP103/DMARQ3 |          |

|     |                  |                                                                                       |          |

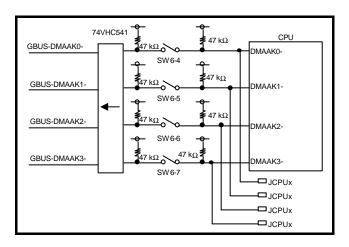

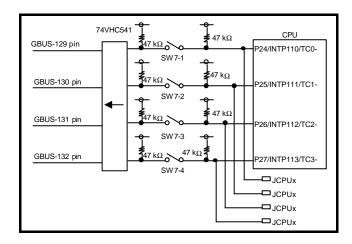

|     | 10.11.<br>10.12. | PBD0/DMAAK0PBD3/DMAAK3<br>P24/INTP110/TC0P27/INTP113/TC3                              |          |

|     | 10.12.           |                                                                                       |          |

|     | 10.10.           | OTTEN OIGHALD                                                                         |          |

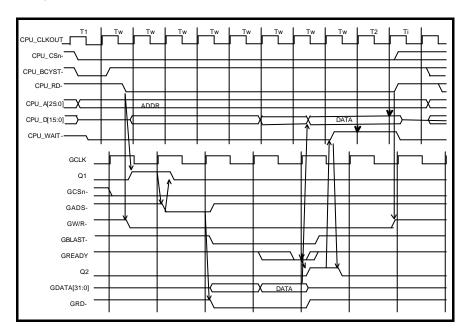

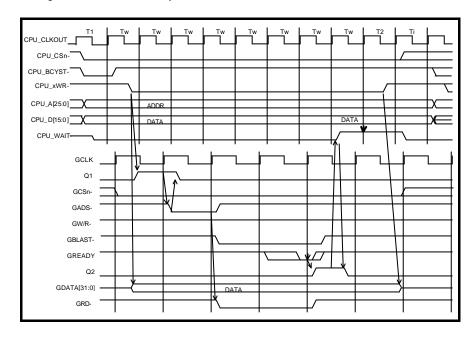

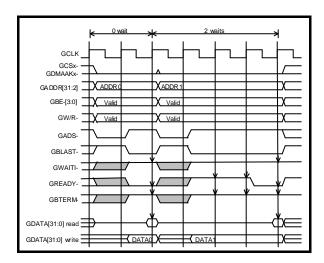

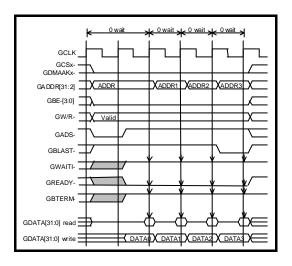

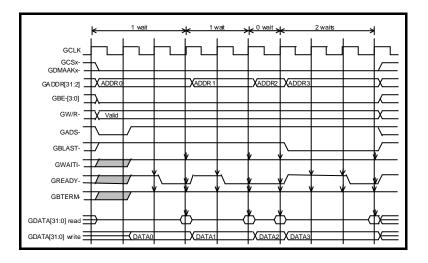

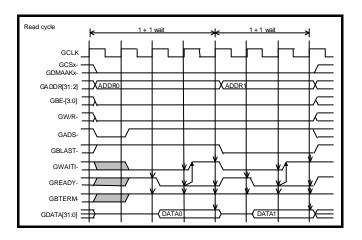

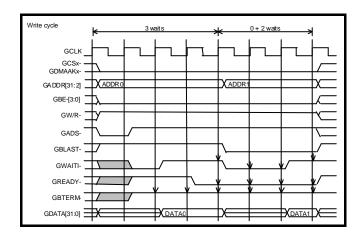

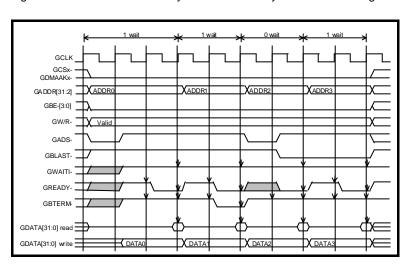

| 11. |                  | IFIC GBUS SPECIFICATIONS                                                              |          |

|     | 11.1.            | GENERAL                                                                               | _        |

|     | 11.2.            | BUS CYCLE                                                                             |          |

|     | 11.3.            | CHIP SELECT                                                                           | 39       |

| 12. | APPEN            | NDIX A MULTI MONITOR                                                                  | 40       |

|     | 12.1.            | BOARD SETTING                                                                         | 40       |

|     |                  | 12.1.1. RTE for Win 32 Installation                                                   | 40       |

|     |                  | 12.1.2. SW1 Setting                                                                   |          |

|     |                  | 12.1.3. Connection of Board                                                           |          |

|     | 12.2.            | Multi MONITOR                                                                         | 41       |

|     |                  | 12.2.1. 7-Segment LED on Startup                                                      | 41       |

|     |                  | 12.2.2. ROM Monitor Work RAM                                                          |          |

|     |                  | 12.2.3. Monitor Interrupt                                                             | 41       |

|     |                  | 12.2.4 INIT SP Setting                                                                | 41       |

|     |       | 12.2.5. Timer Interrupt           | 41 |

|-----|-------|-----------------------------------|----|

|     |       | 12.2.6. Initializing Hardware     | 41 |

|     |       | 12.2.7. Special Instruction       | 42 |

|     | 12.3. | RTE COMMANDS                      | 42 |

|     |       | 12.3.1. HELP(?)                   | 42 |

|     |       | 12.3.2. INIT                      | 42 |

|     |       | 12.3.3. VER                       | 42 |

|     |       | 12.3.4. SFR Command               | 42 |

| 13. | APPEN | IDIX B PARTNER MONITOR            | 43 |

|     | 13.1. | BOARD SETTING                     | 43 |

|     |       | 13.1.1. SW1 Setting               | 43 |

|     |       | 13.1.2. Connection of Board       | 43 |

|     | 13.2. | PARTNER MONITOR                   | 44 |

|     |       | 13.2.1. 7-Segment LED on Startup  | 44 |

|     |       | 13.2.2. ROM Monitor Work RAM      | 44 |

|     |       | 13.2.3. Monitor Interrupt         | 44 |

|     |       | 13.2.4. SP Setting                | 44 |

|     |       | 13.2.5. Initializing Hardware     | 44 |

|     |       | 13.2.6. Special Instruction       | 44 |

| 11  | ADDEN | NDIX C GBUS COMMON SPECIFICATIONS | 45 |

| 14. | 14.1. | TERMINOLOGY                       |    |

|     | 17.1. | 14.1.1. CPU Board and Motherboard |    |

|     |       | 14.1.2. Bus Cycle and Micro Cycle |    |

|     | 14.2. | SIGNALS                           |    |

|     | 14.3. | PIN ASSIGNMENTS                   |    |

|     | 14.4. | PROCESSING OF UNUSED PINS         |    |

|     | 14.5. | ALLOCATING GCS-[7:0]              |    |

|     | 14.6. | BUS CYCLE                         |    |

|     |       | 14.6.1. Single Cycle              |    |

|     |       | 14.6.2. Burst Cycle               |    |

|     |       | 14.6.3. GWAITI                    |    |

|     |       | 14.6.4. GBTERM                    |    |

|     | 14.7. | TIMING55                          |    |

|     |       |                                   |    |

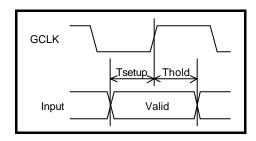

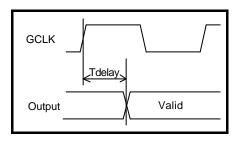

|     |       | 14.7.1. Setup Time                | 55 |

|     |       | 14.7.1. Setup Time                |    |

#### 1. INTRODUCTION

The RTE-V850E/MA1-CB is a CPU board that is designed to evaluate the NEC V850E/MA1 RISC processor.

The board features a V850E/MA1 capable of operating at a maximum speed of 50 MHz, memory, serial interface, and bus connector for expansion. As the memories, a high-speed SRAM and high-capacity SDRAM are provided as standard. The SDRAM is controlled by using the internal memory controller of the V850E/MA1.

These functions enable the RTE-V850E/MA1-CB to be used for a wide variety of applications including processor performance evaluation and application program development at the initial stage, and to also be used as an engine for demonstration and simulation.

The GHS Multi or NEC PARTNER source-level debugger can be used as a development software tool with the RTE-V850E/MA1-CB. The type of monitor to be stored in ROM depends on the debugger type. In ROM, the monitor specified at the time of purchase is stored. Even when neither of the debuggers is purchased together with the RTE-V850E/MA1-CB, they can be purchased at anytime subsequently.

#### 1.1. NUMERIC NOTATION

This manual represents numbers according to the notation described in the following table. Hexadecimal and binary numbers may be hyphenated at every four digits, if they are difficult to read because of many digits being in each number.

| Number                                                 | Notation rule                | Example                                |

|--------------------------------------------------------|------------------------------|----------------------------------------|

| Decimal number                                         | Only numerals are indicated. | "10" represents number 10 in decimal.  |

| Hexadecimal A number is suffixed with letter H. number |                              | "10H" represents number 16 in decimal. |

| Binary number A number is suffixed with letter B.      |                              | "10B" represents number 2 in decimal.  |

**Number Notation Rules**

# 2. FUNCTIONS

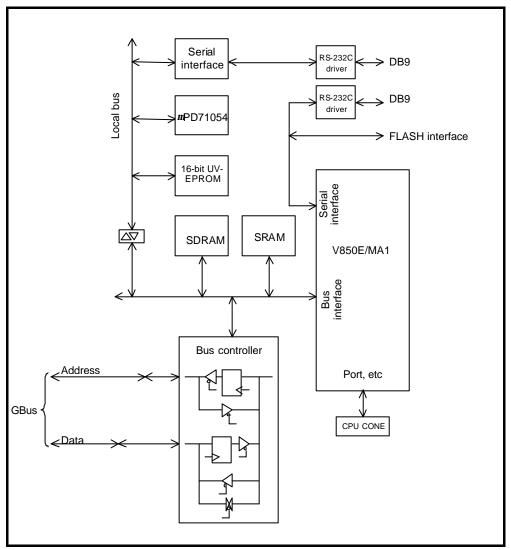

The overview of each function block of the RTE-V850E/MA1-CB is shown below.

RTE-V850E/MA1-CB Block Diagram

"Local bus" is a bus that buffers the CPU bus and is synchronized with the CPU. "Gbus" is independent of the CPU and is fixed at 33 MHz.

## 3. MAJOR FEATURES

- Two types of monitor ROM are provided: one is used for the Green Hills Multi and the other for the NEC PARTNER.

- Real-time execution and evaluation at a high-level language level using Multi or PARTNER.

- A ROM emulator can be connected.

- 1M byte of high-speed SRAM and 32M bytes of SDRAM are provided as standard.

- Two serial interfaces are provided. (One channel uses an external controller and the other channel uses the internal controller of the CPU. The serial channel of an external controller is used as the monitor.)

- Three timer channels are provided. (One channel is used for the monitor.)

# 4. BASIC SPECIFICATIONS

| Processor                                                                 | V850E/MA1                                                                 |  |  |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

| CPU clock                                                                 | 50 MHz                                                                    |  |  |

| Bus clock                                                                 | 50 MHz                                                                    |  |  |

| Power supply                                                              | +5 V, 2 A (max.)                                                          |  |  |

| Memory                                                                    |                                                                           |  |  |

| EPROM                                                                     | 128 KB 64 K × 16 bits (40-pin DIP) × 1 (512K bytes max.)                  |  |  |

| SRAM                                                                      | 1 MB 512 K × 8 bits × 2                                                   |  |  |

| SDRAM                                                                     | 32 MB $4 \text{ M} \times 4 \text{ bits} \times 4 \text{ banks} \times 4$ |  |  |

| I/O                                                                       |                                                                           |  |  |

| Serial (2 ch)                                                             | Internal CPU (UART), DB9 connector                                        |  |  |

|                                                                           | Equivalent to NS16550, DB9 connector                                      |  |  |

| Timer                                                                     | mPD71054, 500-ns resolution                                               |  |  |

| I/O port                                                                  | LED (7-segment) display/switch input                                      |  |  |

| Others                                                                    |                                                                           |  |  |

| CPU connector Connector with all function pins of the V850E/MA1 connected |                                                                           |  |  |

| GBUS connector                                                            | RTE-CB standard 32-bit interface                                          |  |  |

|                                                                           | (4G bytes, 32-bit bus, correspond to DMA)                                 |  |  |

| FLASH interface                                                           | Interface for connecting FLASH Writer                                     |  |  |

| Reset switch                                                              | Push type                                                                 |  |  |

#### 5. BOARD CONFIGURATION

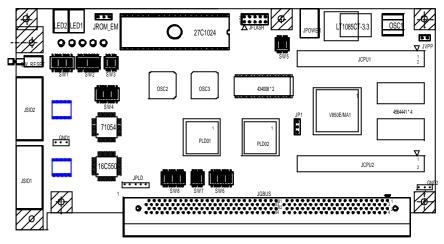

The physical layout of the major components on the RTE-V850E/MA1-CB board is shown below. This chapter explains each component.

RTE-V850E/MA1-CB Components Layout

# 5.1. RESET SWITCH (SW\_RESET)

SW\_RESET is a reset switch for the entire board. Pressing this switch causes all the circuits including the CPU to be reset.

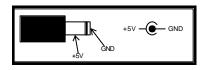

## 5.2. POWER CONNECTOR (JPOWER)

The power supplied to the JPOWER connector should be one rated as listed below.

Voltage: +5 V

Current: Maximum of 2 A

Mating connector: Type A (5.5 mm in diameter)

Polarity:

Note the polarity when attaching the power connector.

To supply power from the JGBUS connector, do not connect a power source to JPOWER.

## 5.3. SWITCH 1 (SW1)

SW1 is a general-purpose input port switch. The setting status can be read from an input port (see Section 7.4.2). When the port is read, a switch being set to OFF represents 1, while its being set to ON represents 0. When the monitor ROM is used, all SW1 switches except some are already set. Set this switch for assignment with the monitor ROM by referring to the following sections and in accordance with your environment:

When using Multi, see Section 12.1.2.

When using PARTNER, see Section 13.1.1.

# 5.4. SWITCH 2 (SW2)

SW2 selects an operation of the board by hardware. The setting of the switch can be read from an input port (see Section 7.4.3).

| No. | Signal name | Factory setting | Function                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FBOOT       | OFF             | Specifies resources to be allocated to the CS0 space.  OFF: The on-board UV-EPROM is allocated to the CS0 space.  ON: GCS1- space of GBUS is allocated to the CS0 space (see Section 7.1).                                                                                                |

| 2   | TEST        | OFF             | Set this signal to OFF.                                                                                                                                                                                                                                                                   |

| 3   | BCLK_LOW    | OFF             | Selects frequency of oscillator mounted on OSC1. Depending on the value set, the monitor ROM changes the number of ROM and SRAM wait cycles. In addition, the number of I/O wait cycles is changed by hardware.  OFF: Bus clock exceeds 33 MHz.  ON: Bus clock is kept at 33 MHz or less. |

| 4   | Not used    | OFF             |                                                                                                                                                                                                                                                                                           |

| 5   | NMI/INT     | OFF             | Specifies interrupt to be used by the monitor.  OFF: NMI0  ON: INTP000                                                                                                                                                                                                                    |

| 6   | Not used    | OFF             | Not used. Must be set to OFF.                                                                                                                                                                                                                                                             |

| 7   | Not used    | OFF             | Not used. Must be set to OFF.                                                                                                                                                                                                                                                             |

| 8   | Not used    | OFF             | Not used. Must be set to OFF.                                                                                                                                                                                                                                                             |

SW2-5 is read only to set the interrupt controller by the monitor.

# 5.5. SWITCH 3 (SW3)

SW3 selects the type of ROM inserted in the ROM socket and performs setting related to banks.

| No. | Signal name | Factory setting | Function                                                                                                                                                                                                                                                |

|-----|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ROM_TYPE0   | OFF             | Selects the type of ROM. [ROM_TYPE1, ROM_TYPE0]                                                                                                                                                                                                         |

|     |             |                 | [ OFF , OFF ]: When monitor ROM is used                                                                                                                                                                                                                 |

| 2   | ROM_TYPE1   | OFF             | [ OFF , ON ]: When 27C4096 is used                                                                                                                                                                                                                      |

|     |             |                 | [ ON , OFF ]: When 27C2048 is used                                                                                                                                                                                                                      |

|     |             |                 | [ ON , ON ]: When 27C1024 is used                                                                                                                                                                                                                       |

| 3   | BANK_DIS    | OFF             | Specifies whether the upper and lower halves (banks) of ROM are separated. Be sure to set this signal to OFF when monitor is used.  OFF: Upper and lower halves of ROM are separated.  ON: Upper and lower halves of ROM are used as a contiguous area. |

| 4   | BANK_LOW    | OFF             | Specifies whether either the upper or lower half of the ROM is valid when the ROM is used in bank mode.  OFF: Selects lower half.  ON: Selects upper half.                                                                                              |

[Caution] To use the monitor ROM, do not change the factory setting.

# 5.6. SWITCH 4 (SW4)

SW4 specifies the mode of a CPU pin. When a signal of this switch is set to OFF, the corresponding CPU pin is 1; when it is set to ON, the pin is 0.

| No. | CPU pin name | Factory setting | Function                                        |

|-----|--------------|-----------------|-------------------------------------------------|

| 1   | MODE0        | ON              | Directly connected to the MODE0 pin of the CPU. |

| 2   | MODE1        | ON              | Directly connected to the MODE1 pin of the CPU. |

| 3   | CKSEL        | ON              | Directly connected to the CKSEL pin of the CPU. |

| 4   | FLASH-       | OFF             | ON when the programmer is connected to JFLASH;  |

|     |              |                 | otherwise, OFF.                                 |

# <<Cautions>>

1. Use MODE[1..0] under the following operating conditions.

| MODE1 | MODE0 | Mode                                                     | Operating conditions                         |

|-------|-------|----------------------------------------------------------|----------------------------------------------|

| ON    | ON    | ROM-less mode 0 (16 bits)                                | Monitor can be used (factory-set condition). |

| ON    | OFF   | ROM-less mode 1 (8 bits)                                 | Setting prohibited                           |

| OFF   | ON    | Single-chip mode 0 (0 address), or FLASH program mode    | Monitor cannot be used.                      |

| OFF   | OFF   | Single-chip mode 1 (1M addresses), or FLASH program mode | Monitor can be used.                         |

2. To set SW4-4 to ON, set SW4-2 to OFF (FLASH program mode).

# 5.7. SWITCHES 5 TO 8 (SW5 TO SW8)

SW5 to SW8 physically cuts the board's signal lines connected to CPU pins. All the switches are factory-set to ON (connected). Set a switch to OFF only when the corresponding signal line is used for an external source, but only if the internally used resources are not necessary.

Remark The following tables show the CPU pins and final internal resource names.

# [SW5]

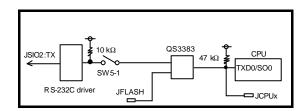

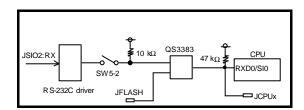

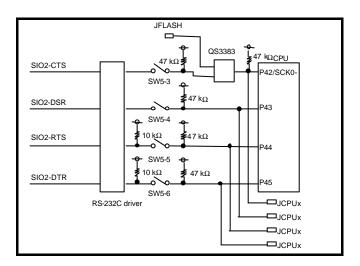

| No. | CPU pin name | Factory setting | Internally used resource |

|-----|--------------|-----------------|--------------------------|

| 1   | P40/SO0/TXD0 | ON              | SIO2-TXD                 |

| 2   | P41/SI0/RXD0 | ON              | SIO2-RXD                 |

| 3   | P42/SCK0-    | ON              | SIO2-RTS-                |

| 4   | P43/SO1/TXD1 | ON              | SIO2-CTS-                |

| 5   | P44/SI0/RXD1 | ON              | SIO2-DSR-                |

| 6   | P45/SCK1-    | ON              | SIO2-DTR-                |

| 7   | Not used     | OFF             |                          |

| 8   | Not used     | OFF             |                          |

# [SW6]

| No. | CPU pin name        | Factory setting | Internally used resource |

|-----|---------------------|-----------------|--------------------------|

| 1   | P04/INTP100/DMARQ0- | ON              | DMARQ0- of GBUS          |

| 2   | P05/INTP101/DMARQ1- | ON              | DMARQ1- of GBUS          |

| 3   | P06/INTP102/DMARQ2- | ON              | DMARQ2- of GBUS          |

| 4   | P07/INTP103/DMARQ3- | ON              | DMARQ3- of GBUS          |

| 5   | PBD0/DMAAK0-        | ON              | DMAAK0- of GBUS          |

| 6   | PBD1/DMAAK1-        | ON              | DMAAK1- of GBUS          |

| 7   | PBD2/DMAAK2-        | ON              | DMAAK2- of GBUS          |

| 8   | PBD3/DMAAK3-        | ON              | DMAAK3- of GBUS          |

# [SW7]

| No. | CPU pin name     | Factory setting | Internally used resource |

|-----|------------------|-----------------|--------------------------|

| 1   | P24/INTP110/TC0- | ON              | Pin 129 of GBUS          |

| 2   | P25/INTP111/TC1- | ON              | Pin 130 of GBUS          |

| 3   | P26/INTP112/TC2- | ON              | Pin 131 of GBUS          |

| 4   | P27/INTP113/TC3- | ON              | Pin 132 of GBUS          |

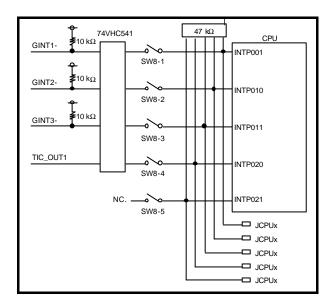

# [SW8]

| L | No. | CPU pin name      | Factory setting | Internally used resource |

|---|-----|-------------------|-----------------|--------------------------|

|   | 1   | P02/INTP001/TI001 | ON              | GINT1- of GBUS           |

|   | 2   | P11/INTP010/TI010 | ON              | GINT2- of GBUS           |

|   | 3   | P12/INTP011/TI011 | ON              | GINT3- of GBUS           |

|   | 4   | P21/INTP020/TI020 | ON              | OUT1- of TIC             |

|   | 5-8 | Not used          | OFF             | Not used                 |

#### 5.8. 7SEG-LED, xxx-LED

The LEDs are used to indicate statuses, as listed below. The two 7-segment LEDs are used by the monitor at startup. After that, they can be used for any user application.

| LED    | Description                                                                                            |

|--------|--------------------------------------------------------------------------------------------------------|

| POWER  | Lights when power is supplied to the RTE-V850E/MA1-CB board.                                           |

| TOVRDY | Lights when time-over ready occurs, and does not go off until cleared by software (see Section 7.4.5). |

|        |                                                                                                        |

| CS0    | Lights when CS0 space is accessed.                                                                     |

| CS1    | Lights when CS1 space is accessed.                                                                     |

| CS2    | Lights when CS2 space is accessed.                                                                     |

| CS3    | Lights when CS3 space is accessed.                                                                     |

**Board LED Status**

## 5.9. TEST PINS FOR ROM EMULATOR (JROM-EM1)

Test pins (JROM-EM1s) are used to connect a ROM emulator. They accept control signals listed below. The following table lists the signal names and functions.

| Signal name   | Input/<br>output | Function                                                                                                                                                                                                                     |  |

|---------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET-<br>(1) | Input            | When a low level is supplied to this test pin, the CPU is reset.  A reset request signal from the ROM emulator is connected to the test pin.                                                                                 |  |

|               |                  | The test pin is pulled up with 1 k $\Omega$ .                                                                                                                                                                                |  |

| NMI-<br>(2)   | Input            | When a low level is supplied to this test pin, an NMI signal is given to the CPU. (See Section 10.5.) An NMI request signal from the ROM emulator is connected to the test pin. The test pin is pulled up with 1 $k\Omega$ . |  |

| GND<br>(3)    |                  | This test pin is at a ground level. The ground level of the ROM emulator is connected to the test pin.                                                                                                                       |  |

JROM-EM1 Pin Functions

# 5.10. CLOCK SOCKET (OSC1)

An oscillator for generating the clock signal to be supplied to the CPU is mounted in the OSC1 socket. OSC1 is converted to the 3.3-V level, and is connected to the CPUCLK pin of the CPU. Accepts DIP 8-pin (half-type) oscillators.

When you have to cut an oscillator pin for convenience, be careful not to cut it too short, or otherwise the frame (housing) of the oscillator may touch a pin in the socket, resulting in a short-circuit occurring.

#### 5.11. CRYSTAL SOCKET (JP1)

JP1 has two functions: it is used to select the clock supplied to the CPU and it also acts as the connector for the crystal oscillator.

To use OSC1 as CPU clock

Short-circuit JP1 pins 1 and 2. In this case, do not mount the crystal.

To mount crystal on JP1 and use the CPU oscillation circuit

Mount the crystal between pins 1 and 3 on JP1. Do not short-circuit pins 1 and 2.

## 5.12. AVDD/AVREF SELECTOR JUMPER (JP2)

The JP2 jumper is used to select the voltage for AD (AVDD/AVREF) to be supplied to the CPU.

To supply voltage from board: Factory-set condition

Jumper pins 1 and 2 of JP1. +3.3 V will be supplied.

To supply voltage from external source (JCPU)

Jumper pins 2 and 3 of JP1. Supply the voltage from pin JCPU2-78.

# 5.13. ROM SOCKETS

The RTE-V850E/MA1-CB has ROM sockets to hold 40-pin ROM chips to provide standard 128K bytes  $(64K \times 16 \text{ bits})$ . When the ROM chips used here are to be replaced, their type should be 27C1024, 27C2048, or 27C4096, and the access time should be 120 ns or less.

## 5.14. SELF-WRITING POWER CONNECTOR (JVPP)

To execute self-writing of the CPU's internal flash ROM, a power supply capable of supplying 7.8 V is necessary. The JVPP connector is used to connect such a power supply.

To execute self-writing, connect a 10 to 12 V power supply to this connector and output a low level to pin P22 of the CPU. This supplies 7.8 V to the VPP pin of the CPU, thus enabling self-writing.

The pin configuration of JVPP is as shown below.

| JVPP pin No. | Name   | Input/output | Function                       |  |

|--------------|--------|--------------|--------------------------------|--|

| 1            | 10-12V | Input        | Inputs voltage of 10 to 12 V.  |  |

| 2            | GND    | Input        | Connected to power supply GND. |  |

# 5.15. FLASH WRITING CONNECTOR (JFLASH)

The JFLASH connector is used to write data to the CPU's internal flash ROM by using a flash programmer device.

To use JFLASH, SW4 must be set (see Section 5.6).

JFLASH Pin Arrangement

| JFLASH pin No. | Signal name | Input/output | Remark                                      |  |

|----------------|-------------|--------------|---------------------------------------------|--|

| 1              | SO0         | Output       | Synchronous serial data output (CMOS level) |  |

| 2              | SI0         | Input        | Synchronous serial data input (CMOS level)  |  |

| 3              | SCK0-       | Input        | Synchronous serial clock input (CMOS level) |  |

| 4              | RESET-      | Input        | Reset input                                 |  |

| 5              | VPP         | Input        | VPP input                                   |  |

| 6              | +3.3V       | Output       | CPU core power level output                 |  |

| 7              | +3.3V       | Output       | CPU-I/O power level output                  |  |

| 8              | GND         | -            | Ground                                      |  |

| 9              | NC          | -            | No connection                               |  |

| (10)           | NC          | _            | No connection (without pin)                 |  |

JFLASH Connector Signals

## 5.16. SERIAL CONNECTOR (JSIO1, JSIO2)

The JSIO1 connector is used for the RS-232C interface that is controlled by the serial controller (TL16C550CPT) on the board.

The JSIO2 connector is used for the RS-232C interface that is controlled by the built-in serial controller of the CPU.

JSIO1 and JSIO2 are 9-pin D-SUB RS-232C connectors (male) like that commonly used on the PC/AT. All signals on both of these connectors are converted to the RS-232C level. The figure and table below indicate the pin and signal arrangement of these connectors.

For the signals to be connected to the host, the table indicates two modes of wiring on the host: one for a 9-pin D-SUB connector, and the other for a 25-pin D-SUB connector. (Regular cross-cable wiring is used for these connections.)

Pin Arrangement of JSIO1 and JSIO2 (Male)

| JSIO1   | Signal name   | Input/ | Connector pin number on the host side |         |  |

|---------|---------------|--------|---------------------------------------|---------|--|

| pin No. | Signal Harrie | output | D-SUB9                                | D-SUB25 |  |

| 1       | DCD           | Input  |                                       |         |  |

| 2       | RxD(RD)       | Input  | 3                                     | 2       |  |

| 3       | TxD(SD)       | Output | 2                                     | 3       |  |

| 4       | DTR(DR)       | Output | 1, 6                                  | 6, 8    |  |

| 5       | GND           |        | 5                                     | 7       |  |

| 6       | DSR(ER)       | Input  | 4                                     | 20      |  |

| 7       | RTS(RS)       | Output | 8                                     | 5       |  |

| 8       | CTS(CS)       | Input  | 7                                     | 4       |  |

| 9       | RI            | Input  |                                       |         |  |

JSIO1 Connector Signals

| JSIO2             | CPU pin | Signal name | Input/ | Connector pin number on the host side |         |  |

|-------------------|---------|-------------|--------|---------------------------------------|---------|--|

| pin No.           | 01 0 p  |             | output | D-SUB9                                | D-SUB25 |  |

| 1 Note            |         | DCD         | Input  |                                       |         |  |

| 2                 | P41     | RxD (RD)    | Input  | 3                                     | 2       |  |

| 3                 | P40     | TxD (SD)    | Output | 2                                     | 3       |  |

| 4                 | P45     | DTR (DR)    | Output | 1, 6                                  | 6, 8    |  |

| 5                 |         | GND         |        | 5                                     | 7       |  |

| 6                 | P44     | DSR (ER)    | Input  | 4                                     | 20      |  |

| 7                 | P42     | RTS (RS)    | Output | 8                                     | 5       |  |

| 8                 | P43     | CTS (CS)    | Input  | 7                                     | 4       |  |

| 9 <sup>Note</sup> |         | RI          | Input  |                                       |         |  |

JSIO2 Connector Signals

Note JSIO2 pins 1 and 9 are not used on board.

# 5.17. JGBUS CONNECTOR (JGBUS)

This is a 32-bit bus connector for expansion. For details, see Chapters 11 and 14.

# 5.18. CPU CONNECTOR (JCPU1, JCPU2)

The CPU connector signals are connected directly to the V850E/MA1. Many signals are used on the board. So, be careful when extracting signals from the JCPU.

| JCPU pin No. | Signal name         | JCPU pin No. | Signal name         |

|--------------|---------------------|--------------|---------------------|

| 1            | +3.3V               | 2            | GND                 |

| 3            | PDL15/D15           | 4            | PDL14/D14           |

| 5            | PDL13/D13           | 6            | PDL12/D12           |

| 7            | PDL11/D11           | 8            | PDL10/D10           |

| 9            | PDL9/D9             | 10           | PDL8/D8             |

| 11           | PDL7/D7             | 12           | PDL6/D6             |

| 13           | PDL5/D5             | 14           | PDL4/D4             |

| 15           | PDL3/D3             | 16           | PDL2/D2             |

| 17           | PDL1/D1             | 18           | PDL0/D0             |

| 19           | NC.                 | 20           | NC.                 |

| 21           | +3.3V               | 22           | GND                 |

| 23           | P07/INTP103/DMARQ3- | 24           | P06/INTP102/DMARQ2- |

| 25           | P05/INTP101/DMARQ1- | 26           | P04/INTP100/DMARQ0- |

| 27           | P03/TO00            | 28           | P02/INTP001/TI001   |

| 29           | P01/INTP000/TI000   | 30           | P00/PWM0            |

| 31           | PBD3/DMAAK3-        | 32           | PBD2/DMAAK2-        |

| 33           | PBD1/DMAAK1-        | 34           | PBD0/DMAAK0-        |

| 35           | P13/TO01            | 36           | P12/INTP011/TI011   |

| 37           | P11/INTP010/TI010   | 38           | P10/PWM1            |

| 39           | NC.                 | 40           | NC.                 |

| 41           | +3.3V               | 42           | GND                 |

| 43           | P27/INTP113/TC3-    | 44           | P26/INTP112/TC2-    |

| 45           | P25/INTP111/TC1-    | 46           | P24/INTP110/TC0-    |

| 47           | P23/TO02            | 48           | P22/INTP021/TI021   |

| 49           | P21/INTP020/TI020   | 50           | P20/NMI             |

| 51           | P37/INTP123/ADTRG   | 52           | P36/INTP122         |

| 53           | P35/INTP121         | 54           | P34/INTP120/RXD2    |

| 55           | P33/INTP133/TXD2    | 56           | P32/INTP132/SCK2-   |

| 57           | P31/INTP131/SI2     | 58           | P30/INTP130/SO2     |

| 59           | NC.                 | 60           | NC.                 |

| 61           | +5V                 | 62           | GND                 |

| 63           | RESET-              | 64           | NC.                 |

| 65           | P45/SCK1-           | 66           | P44/SI1/RXD1        |

| 67           | P43/SO1/TXD1        | 68           | P42/SCK0-           |

| 69           | P41/SI0/RXD0        | 70           | P40/SO0/TXD0        |

| 71           | NC.                 | 72           | NC.                 |

| 73           | NC.                 | 74           | NC.                 |

| 75           | NC.                 | 76           | NC.                 |

| 77           | NC.                 | 78           | RESET_REQ-Note      |

| 79           | +5V                 | 80           | GND                 |

|              |                     |              | -                   |

JCPU1 Connector

**Note** RESET\_REQ is a reset request signal line from JCPC (low-active).

| JCPU pin No. | Signal name          | JCPU pin No. | Signal name          |

|--------------|----------------------|--------------|----------------------|

| 1            | +3.3V                | 2            | GND                  |

| 3            | PAL0/A0              | 4            | PAL1/A1              |

| 5            | PAL2/A2              | 6            | PAL3/A3              |

| 7            | PAL4/A4              | 8            | PAL5/A5              |

| 9            | PAL6/A6              | 10           | PAL7/A7              |

| 11           | PAL8/A8              | 12           | PAL9/A9              |

| 13           | PAL10/A10            | 14           | PAL11/A11            |

| 15           | PAL12/A12            | 16           | PAL13/A13            |

| 17           | PAL14/A14            | 18           | PAL15/A15            |

| 19           | PAH0/A16             | 20           | PAH1/A17             |

| 21           | +3.3V                | 22           | GND                  |

| 23           | PAH2/A18             | 24           | PAH3/A19             |

| 25           | PAH4/A20             | 26           | PAH5/A21             |

| 27           | PAH6/A22             | 28           | PAH7/A23             |

| 29           | PAH8/A24             | 30           | PAH9/A25             |

| 31           | NC.                  | 32           | NC.                  |

| 33           | NC.                  | 34           | NC.                  |

| 35           | PCD0/SDCKE           | 36           | PCD1/SDCLK           |

| 37           | PCD2/LBE-/SDCAS-     | 38           | PCD3/UBE-/SDRAS-     |

| 39           | PCS0/CS0-            | 40           | PCS1/CS1-/RAS1-      |

| 41           | +3.3V                | 42           | GND                  |

| 43           | PCS2/CS2-/IOWR-      | 44           | PCS3/CS3-/RAS1-      |

| 45           | PCS4/CS4-/RAS4-      | 46           | PCS5/CS5-/IORD-      |

| 47           | PCS6/CS6-/RAS6-      | 48           | PCS7/CS7-            |

| 49           | PCT0/LCAS-/LWR-/LDQM | 50           | PCT1/UCAS-/UWR-/UDQM |

| 51           | PCT4/RD-             | 52           | PCT5/WE-             |

| 53           | PCT6/OE-             | 54           | PCT7/BCYST-          |

| 55           | PCM0/WAIT-           | 56           | PCM1/CLKOUT/BUSCLK   |

| 57           | PCM2/HLDAK-          | 58           | PCM3/HLDRQ-          |

| 59           | PCM4/REFRQ-          | 60           | PCM5/SELFREF         |

| 61           | +5V                  | 62           | GND                  |

| 63           | NC.                  | 64           | NC.                  |

| 65           | NC.                  | 66           | P50/TI030/INTP030    |

| 67           | P51/TI031/INTP031    | 68           | P52/TO03             |

| 69           | P70/ANI0             | 70           | P71/ANI1             |

| 71           | P72/ANI2             | 72           | P73/ANI3             |

| 73           | P74/ANI4             | 74           | P75/ANI5             |

| 75           | P76/ANI6             | 76           | P77/ANI7             |

| 77           | AVSS (GND)           | 78           | AVDD/AVREF (+3.3V)   |

| 79           | +5V                  | 80           | GND                  |

JCPU2 Connector

#### 6. CONNECTION WITH THE HOST PC

## 6.1. RS-232C CONNECTION

Serially connect the host machine using the monitor ROM by means of the following procedure:

- <1> Get an optional RS-232C cable and a power supply.

- Set and check the setting of the switches on the board. Specify a baud rate by using SW1 (see Sections 12.1.2 and 13.1.1).

- <3> Connect the JSIO1 connector and host machine with the RS-232C cable, and supply power to the JPOWER connector. Confirm that the POWER-LED on the board lights and that the 7-segment LED indicating that the monitor has started lights.

If the LED does not light, turn off the power immediately, and check the connection.

<4> Start the debugger on the host machine, and connect it via the RS-232C interface. If an error occurs, confirm the connection of the serial cable and the setting of the switches (especially, baud rate). For the method and procedure of starting the debugger, see the debugger manual.

Place the board on an insulating material. If a conductive material touches the board while power is supplied to the board, the board may malfunction.

# 7. HARDWARE REFERENCES

This chapter describes the hardware of the RTE-V850E/MA1-CB.

# 7.1. MEMORY AND I/O MAP

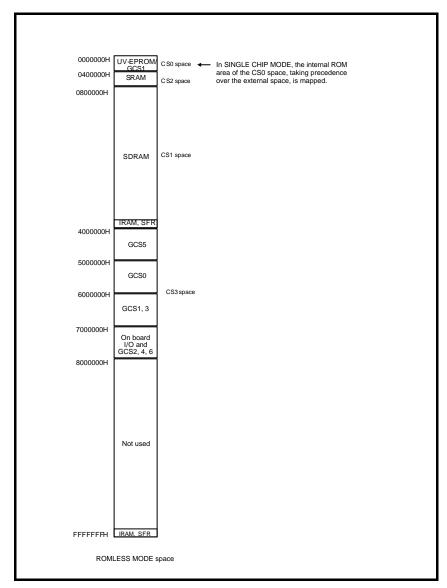

The figure below shows the memory and I/O mapping on the board.

Memory I/O Map

#### CS0 space (UV-EPROM, GCS1-): 0000000 to 03FFFFF (4M bytes)

UV-EPROM is allocated to the CS0 space, or the CS0 space is reserved as a space for GCS-1 of GBUS. On-board UV-EPROM is allocated to the space when SW2-1 (FBOOT) is OFF. When SW2-1 (FBOOT) is ON, it is reserved as a space for GCS1- of GBUS.

The GCS1 space can be accessed from the CS3:6000000 to 6FFFFFF spaces. By locating a flash ROM in the GCS1 space of GBUS, therefore, the flash ROM can be rewritten by using the monitor ROM of UV-EPROM. Thereafter, a program can be booted from the flash ROM.

For GBUS, see Chapters 11 and 14.

In single-chip mode, the internal ROM space cannot be accessed from an external source.

## CS2 space (SRAM): 0400000 to 07FFFFF (4M bytes)

SRAM is allocated to the CS2 space. The actual capacity is 1M byte. An image is generated every 1M byte within this space. When the monitor is used, part of this space is reserved for the monitor work area (see Sections 12.2.2 and 13.2.2).

# CS1 space (SDRAM): 0800000 to 3FFFFFF (56M bytes)

SDRAM is allocated to the CS1 space. The actual capacity is 32M bytes. An image is generated every 32M bytes within this space. Access to the internal resources for an internal RAM or SFR area takes precedence over access to SDRAM.

# CS3 space (GCS5-): 4000000 to 4FFFFFF (16M bytes)

The CS3 space is reserved as a space for GCS5- of GBUS. For GBUS, see Chapters 11 and 14.

## CS3 space (GCS0-): 5000000 to 5FFFFFF (16M bytes)

The CS3 space is reserved as a space for GCS0- of GBUS. For GBUS, see Chapters 11 and 14.

# CS3 space (GCS1-, GCS3-): 6000000 to 6FFFFFF (16M bytes)

The CS3 space is reserved as an area for GCS1- and GCS3- of GBUS. For GBUS, see Chapters 11 and 14.

# CS3 space (I/O, GCS2-, GCS4-, GCS6-): 7000000 to 7FFFFFF (16M bytes)

The CS3 space is used as an I/O space. There are reserved spaces for the board's I/O and GCS2-, GCS4-, and GCS6- of GBUS. For the I/O map, see Section 7.4.1. For GBUS, see Chapters 11 and 14.

## CS4 to CS7 spaces (not used): 8000000 to FFFFFFF (128M bytes)

The CS4 to CS7 spaces are not used on the board.

## 7.2. RECOMMENDED SETTINGS

This section explains the recommended setting values of each register related to memory and I/O resource access.

# 7.2.1. MEMC Registers

Make the following register settings for the system bus. Note that the setting for some registers differs depending on the setting of SW2-3 (BCLK\_LOW).

| Register name         | Address   | Setting | Remarks                                          |  |

|-----------------------|-----------|---------|--------------------------------------------------|--|

| CKC                   | 0xFFFF822 | 0x07    | DCLK: 00, TBCS: 00, CESEL: 00, CKDIV: 111        |  |

| BCT0                  | 0xFFFF480 | 0x88B8  | CS0, 2, 3: SRAM/IO, CS1: SDARM                   |  |

| BCT1                  | 0xFFFF482 | 0x8888  | Same as the CPU initial value                    |  |

| DWC0 (BCLK_LOW = OFF) | 0xFFFF484 | 0x1111  | CS0-3: 1 wait                                    |  |

| DWC0 (BCLK_LOW = ON)  |           | 0x0000  | CS0-3: 0 wait                                    |  |

| DWC1                  | 0xFFFF486 | 0x7777  | CS4-7,: 7 waits: Same as the CPU initial value   |  |

| VSWC (BCLK_LOW = OFF) | 0xFFFF06E | 0x14    | VPB: BCLK >= 33 MHz = 0x14                       |  |

| VSWC (BCLK_LOW = ON)  |           | 0x12    | < 33 MHz = 0x12                                  |  |

| BCC                   | 0xFFFF488 | 0xFFC0  | CS0-2: 0 clk, CS3-7: 3clks                       |  |

| ASC                   | 0xFFFF48A | 0x5555  | All 1 addr wait                                  |  |

| BCP                   | 0xFFFF48C | 0x00    | Normal bus cycle                                 |  |

| CSC0                  | 0xFFFF060 | 0xFCF3  | (Chip Select Control Register0)                  |  |

| CSC1                  | 0xFFFF062 | 0x2C11  | (Chip Select Control Register1): Same as the CPU |  |

|                       |           |         | initial value                                    |  |

| BSC                   | 0xFFFF066 | 0x5555  | All 16-bit: Same as the CPU initial value        |  |

| BEC                   | 0xFFFF068 | 0x0000  | All little endian: Same as the CPU initial value |  |

| SCR1                  | 0xFFFF4A4 | 0x2096  | SDRAM (LTM = 2, BCW = 2, SSO = 16, RAW = 12      |  |

|                       |           |         | SAW = 10)                                        |  |

| RFS1 (BCLK_LOW = OFF) | 0xFFFF4A6 | 0x8017  | 50 MHz: 15.4 <b>m</b> s                          |  |

| RFS1 (BCLK_LOW = ON)  |           | 0x800F  | 33 MHz: 15.5 <b>ms</b>                           |  |

**[Caution]** For the setting procedure of SDRAM-related registers (SCR1 and SFR1), refer to the CPU manual.

#### 7.3. MEMORY RESOURCES

RTE-V850E/MA1-CB has SDRAM, SRAM, and UV-EPROM as on-board memory resources. As part of the memory space, the GBUS chip select space is reserved.

This section explains these resources and memory devices.

#### 7.3.1. SDRAM (CS1: 0800000 to 3FFFFFF)

Four SDRAM devices (mPD4564441G5), each consisting of 4M words  $\times$  4 bits  $\times$  4 banks, are provided as SDRAM. The total capacity is 32M bytes.

# 7.3.2. SRAM (CS2: 0400000 to 07FFFFF)

Two high-speed SRAM devices, each having a capacity of 512K words × 8 bits and a speed of 15 ns, are provided as SRAM. The total SRAM capacity, therefore, is 1M byte. If the bus clock exceeds 33 MHz, insert one wait cycle by using the wait controller of the CPU. At a clock frequency up to 33 MHz, it can be accessed without a wait cycle. Because the high-order bits of the address lines are not decoded, an image appears every 1M byte. The second-half 32 KB of the SRAM is used by the monitor as a work area, and cannot be used by a user program (see Sections 12.2.2 and 13.2.2).

# 7.3.3. UV-EPROM (CS0: 0000000 to 03FFFFF)

A ROM of 128K bytes (64K words  $\times$  16 bits), 256K bytes (128K words  $\times$  16 bits), or 512K bytes (256K words  $\times$  16 bits) with an access time of 120 ns or less can be mounted as UV-EPROM. The type of ROM to be mounted and conditions are specified with SW3 (see Section 5.5). Because the high-order bits of the address lines are not decoded, an image appears for each ROM capacity.

Depending on the setting of SW2-3 (BCLK\_LOW), the number of ROM wait cycles is changed forcibly by hardware as shown below.

SW2-3 (BCLK\_LOW): OFF = 7 wait cycles SW2-3 (BCLK\_LOW): ON = 5 wait cycles

#### 7.4. I/O MAP

On-board I/O for the RTE-V850E/MA1-CB includes a serial controller (TL16C550CPT), timer (mPD71054), LEDs, and switches. Also the chip select space of GBUS is reserved as part of the I/O space.

This section explains mapping of the on-board I/O and I/O devices.

## 7.4.1. I/O List

The table below lists the I/O areas and functions. The number of wait cycles changes depending on the setting of SW2-3 (BCLK\_LOW).

|                    |                          | Number of wait cycles |                |  |

|--------------------|--------------------------|-----------------------|----------------|--|

| Address            | Use                      | BCLK_LOW<br>OFF       | BCLK_LOW<br>ON |  |

| 7800000            | SW1                      | 10                    | 7              |  |

| 7801000            | SW2                      | 10                    | 7              |  |

| 7802000            | 7SEGLED                  | 10                    | 7              |  |

| 7803000            | TOVRDY_LED_CLRPLS        | 10                    | 7              |  |

| 7804000 to 7804020 | PIC                      | 10                    | 7              |  |

| 7807000 to 7807070 | UART (TL16C550C)         | 10                    | 7              |  |

| 7808000 to 7808030 | TIC (mPD71054)           | 10                    | 7              |  |

| 7809000            | GBUS BYTE ACCESS CONTROL | 10                    | 7              |  |

# 7.4.2. SW1 Read Port (SW1 7800000H [Read Only])

This port is used to read the status of SW1. The table below indicates the data format.

| Physical address  |     |     |     | Data | bus |     |     |     | Setting |

|-------------------|-----|-----|-----|------|-----|-----|-----|-----|---------|

| 1 Hysical address | D7  | D6  | D5  | D4   | D3  | D2  | D1  | D0  | Setting |

| 7800000H          | SW1 | SW1 | SW1 | SW1  | SW1 | SW1 | SW1 | SW1 | 0 = ON  |

| input             | -8  | -7  | -6  | -5   | -4  | -3  | -2  | -1  | 1 = OFF |

SW1-1 corresponds to switch 1 of SW1, while SW1-8 corresponds to switch 8 of SW1. When a bit of the corresponding switch is set to ON, 0 is read. When it is set to OFF, 1 is read. SW1 is used to set the operation of the monitor. For how to set this switch, see Sections 12.1.2 and 13.1.1.

# 7.4.3. SW2 Read Port (SW2 7801000H [Read Only])

This port is used to read the status of SW2. The data format of this port is shown in the table below.

| Physical address  |     |     |     | Data | bus |     |     |     | Sotting |

|-------------------|-----|-----|-----|------|-----|-----|-----|-----|---------|

| Friysical address | D7  | D6  | D5  | D4   | D3  | D2  | D1  | D0  | Setting |

| 7801000H          | SW2 | SW2 | SW2 | SW2  | SW2 | SW2 | SW2 | SW2 | 0 = ON  |

| input             | -8  | -7  | -6  | -5   | -4  | -3  | -2  | -1  | 1 = OFF |

SW2-1 corresponds to bit 1 of SW2, and SW2-8 corresponds to bit 8 of SW2. When a bit of the corresponding switch is set to ON, 0 is read; when it is set to OFF, 1 is read. SW2 is used to switch the hardware operation. For the function of each switch, see Section 5.4.

# 7.4.4. 7-Segment LED Display Data Output Port (7SEG-LED 7802000H [Write Only])

This port sets the data to be displayed on the four 7-segment LED. The table below indicates the data format. When a bit is set to 0, the corresponding segment is turned on.

| Logical  |        | Data bus |        |        |        |        |       |       |                |

|----------|--------|----------|--------|--------|--------|--------|-------|-------|----------------|

| address  | D7/D15 | D6/D14   | D5/D13 | D4/D12 | D3/D11 | D2/D10 | D1/D9 | D0/D8 | Setting        |

| 7802000H | LED1   | LED1     | LED1   | LED1   | LED1   | LED1   | LED1  | LED1  |                |

| output   | -DP    | -G       | -F     | -E     | -D     | -C     | -B    | -A    | 0 = Turned on  |

| 7802001H | LED2   | LED2     | LED2   | LED2   | LED2   | LED2   | LED2  | LED2  | 1 = Turned off |

| output   | -DP    | -G       | -F     | -E     | -D     | -C     | -B    | -A    |                |

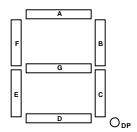

The figure below illustrates the correspondence between the bits and the segments of the 7-segment LED.

# 7.4.5. Time-Over Ready LED Clear Pulse (TOVRDY\_LED\_CLRPLS 7803000H [Write Only])

If data is written to the port, the TOV\_RDY LED, which lights when time-over ready occurs on the board, goes off, and the written data is ignored. Once the TOV\_RDY LED is on, it does not go off until data is written to the port or the board is reset.

#### 7.4.6. Interrupt Controller (PIC: 7804000H to 7804020H [Read/Write])

The PIC supports the Multi and PARTNER interrupts necessary for monitor program execution. The interrupts that can be connected are as follows:

- 1) Communication interrupt from RS-232C devices (UART, TL16C550C)

- 2) Timer interrupt request of TOUT0 of the timer (TIC, mPD71054)

- 3) Occurrence of time-over ready

- 4) GINT0 interrupt

| Logical address | Register       | Data bus |    |    |    |     |     |      |     |

|-----------------|----------------|----------|----|----|----|-----|-----|------|-----|

| Logical address | rvegister      | D7       | D6 | D5 | D4 | D3  | D2  | D1   | D0  |

| 7804000H        | PIC INT-MASK   | Х        | Х  | Х  | Х  | IM3 | IM2 | IM1  | IMO |

| 7804010H        | PIC INT-STATUS | Х        | Х  | Х  | х  | IR3 | IR2 | IR1  | IR0 |

| 7804020H        | PIC INTEN      | х        | Х  | х  | х  | 0   | 0   | INTP | INT |

|                 |                |          |    |    |    |     |     | 000  | EN  |

The INT-MASK register masks interrupts applied to its bits. When an INT\_MASK bit is set to 1, the interrupt is enabled. When multiple bits are selected, each OR value activates an interrupt.

The INTR register is an interrupt status register, for which 1 is read whenever there is an interrupt request. This does not depend on the state of masking. To clear an edge interrupt request, the corresponding bit of this register must be set to 1.

The table below indicates the interrupt source assigned to each bit of IM[0..3] and IR[0..3].

| PIC INT-MASK[], | Interrupt source | Request level |

|-----------------|------------------|---------------|

| STATUS[]        |                  |               |

| 0               | Timer 0 (mode 2) | Edge (rising) |

| 1               | Serial 0         | Level (high)  |

| 2               | Time-over        | Level (high)  |

| 3               | GINT0-           | Level (low)   |

The INTEN register enables or disables all interrupts.

INTEN: Disables the interrupt to be used by the monitor by hardware. At this time, the interrupt request pin is low.

|   | INTEN | NMI0/INTP000         |               |

|---|-------|----------------------|---------------|

| I | 0     | Sets a mask.         | (Reset value) |

| ſ | 1     | Does not set a mask. |               |

INTP000: Selects the interrupt to be used by the monitor.

| INT0/NMI- | Interrupt for monitor       |

|-----------|-----------------------------|

| 0         | NMI0 is used. (Reset value) |

| 1         | INTP000 is used.            |

INTEN is used to create an edge for an interrupt request signal to the CPU each time an interrupt has been serviced when more than one interrupt occurs. If the CPU detects an interrupt reception using the edge, execute the processing that first sets the INTEN bit to 1 and then clears it to 0 at the last step of the interrupt handler. This allows a pending interrupt to be acknowledged.

[Caution] Do not change the contents of the PIC while the monitor is being used.

## 7.4.7. UART (TL16C550C: 7807000H to 7807070H)

The Texas Instruments TL16C550C LSI is used as the UART controller. The TL16C550C has an UART channel. It also has a 16-character FIFO buffer in the transmission/reception block of the UART, and a function for automatically controlling RTS/CTS flow. Therefore, an overrun error of communication can be suppressed by the minimum interrupt.

Each register of the TL16C550C is assigned as listed below. For an explanation of the function of each register, refer to the manual provided with the TL16C550C. (The manual for the TL16C550C is available from the TI&ME of the Texas Instruments home page (http://www.ti.com/).)

| Address  | Read    | Write   |

|----------|---------|---------|

| 7807000H | RBR/DLL | THR/DLL |

| 7807010H | IER/DLM | IER/DLM |

| 7807020H | IIR     | FCR     |

| 7807030H | LCR     | LCR     |

| 7807040H | MCR     | MCR     |

| 7807050H | LSR     | LSR     |

| 7807060H | MSR     | MSR     |

| 7807070H | SCR     | SCR     |

TL16C550C Register Arrangement

The XIN input of the TL16C550C is connected to the 16-MHz clock.

The UART interrupt can be input to NMI1 of the CPU via PIC of the CPU.

The UART is connected to the JSIO1 connector of the board. The UART is used to communicate with the host when the remote debugger is used.

TL16C550C is reset when the system is reset.

[Caution] Do not change the contents of the UART while the monitor is being used.

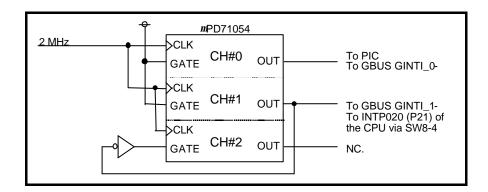

# 7.4.8. TIC (mPD71054 7808000H to 7808030FH)

The NEC mPD71054 is installed as a TIC. The mPD71054 is compatible with the Intel i8254. It has three timers/counters. These timers/counters are used to generate monitor timer interrupts. Each register of the TIC is assigned as listed below.

| Address  | Read      | Write        |

|----------|-----------|--------------|

| 7808000H | COUNTER#0 | COUNTER#0    |

| 7808010H | COUNTER#1 | COUNTER#1    |

| 7808020H | COUNTER#2 | COUNTER#2    |

| 7808030H |           | Control Word |

**TIC Register Arrangement**

The channels of the TIC are connected as shown in the figure below.

Channel 0 is used as the interval timer for the Multi ROM monitor program.

Channels 1 and 2 can be used by a user program as necessary.

Channel 2 is connected to channel 1 by means of a cascade connection.

#### Examples of modes

CH#0: Mode 2 (rate generator) CH#1: Mode 2 (rate generator) CH#2: Mode 0 (down counter)

[Caution] Do not change the contents of the CH0 while the monitor is being accessed.

## 7.4.9. GBUS ACCESS CONTROL (7809000H [Read/Write])

This register is used when accessing in access sizes other than half WORD (16-Bit) to GBUS.

| Logical address | Register  | Data bus  D7 D6 D5 D4 D3  x x x x x x x | bus |    |    |    |    |      |      |

|-----------------|-----------|-----------------------------------------|-----|----|----|----|----|------|------|

| Logical address | rregister | D7                                      | D6  | D5 | D4 | D3 | D2 | D1   | D0   |

| 7809000H        | GBUS ACC  | Х                                       | Х   | Х  | х  | Х  | Х  | Word | Byte |

Byte: Set this bit to 1 to read GBUS in byte units. Usually, keep this bit set to 0. This is used to access GBUS in byte units. The read cycle of the V850E/MA1 is executed in half-word units, regardless of the access size of an instruction. Depending on the resources on the GBUS, however, some devices request an access only in byte units. At the time of access to such a device, please set this bit 1 and access in byte size from CPU.

Word: Set this bit to 1 to access GBUS in word(32-Bit) units. Usually, keep this bit set to 0. This is used to access GBUS in word units. The external bus of V850E/MA1 is 16-Bit. However, depending on the resources on the GBUS, some devices request an access only in word units. At the time of access to such a device, please set this bit 1 and access in word size from CPU.

## [Caution]

Please do not set 1 as Bit of both Byte and Word.

After setting change should surely do IOWAIT() (dummy read of ROM area).

The function of Word-Bit is applied to what has the version of a board newer than 2.2.

#### 8. SOFTWARE

This chapter describes the initialization of the hardware of the RTE-V850E/MA1-CB board, and explains how to use peripheral devices.

#### 8.1. INITIALIZATION

To write a program that is booted from ROM without using the monitor, initialize the internal bus controller of the V850E/MA1 in the first routine of the program. For the values to be set for initialization, see Section 7.2.

#### 8.2. SUCCESSIVE ACCESSES TO mPD71054

To successively access the *m*PD71054, access other spaces at least once between the first and second accesses to the *m*PD71054. These accesses ensure the recovery time of the *m*PD71054.

Recovery time is also assured by a dummy read of a resource (such as ROM) other than the mPD71054.

#### 8.3. LIBRARIES

Libraries are required for programming using the C compiler for I/O accesses and other purposes. However, the methods of writing these libraries and passing their parameters are specific to the GHS. So, modifications may be required, for example, when another compiler is used.

```

/* I/O library */

/* GHS V800 compiler parameter passing */

/* arg0:r6, arg1:r7, arg2:r8, return:r10 */

inb(int addr)

/* Byte (8 bits) input */

_asm(" ld.b 0[r6], r10");

inh(int addr)

/* Half-word (16 bits) input */

_asm(" ld.h 0[r6], r10");

inw(int addr)

/* Word (32 bits) input */

_asm(" ld.w 0[r6], r10");

outb(int addr, int data)

/* Byte (8 bits) output */

_asm(" st.b r7, 0[r6]");

outh(int addr, int data)

/* Half-word (16 bits) output */

_asm(" st.h r7, 0[r6]");

outw(int addr, int data)

/* Word (32 bits) output */

_asm(" st.w r7, 0[r6]");

```

#### 8.4. EXAMPLE OF USING TIMERS

A sample time measurement is indicated below which uses timer 1 and timer 2 cascaded with each other by an external timer (mPD71054) on the board. Timer 1 is initialized as an interval counter (mode 2), and timer 2 is initialized as a down counter (mode 0). By determining the counter values before and after a routine whose execution time is to be measured, the execution time can be calculated. Note that both timers function as down counters. Note also that command recovery (ROM area dummy read) is required for successive accesses to the external timer.

```

/* Sample execution time measurement using timers */

#define TIMERCLK 2000000 /* 2 MHz */

#define INTERVAL (TIMERCLK * 10 / 1000) /* 10 ms (1/100) */

#define IOWAIT() (*(char *) 0x3D80050) /* For I/O command recovery */

InitTimer() /* Timer initialization */

outb(0x7808030, 0x74); IOWAIT(); /* Timer 1 set to mode 2 */

outb(0x7808010, INTERVAL); IOWAIT(); /* Lower-digit count of timer 1 */

outb(0x7808010, INTERVAL /256); IOWAIT(); /* Higher-digit count of timer 1 */

outb(0x7808030, 0xB0); IOWAIT(); /* Timer 2 set to mode 0 */

outb(0x7808020, 0xFF); IOWAIT(); /* Lower-digit count of timer 2 */

outb(0x7808020, 0xFF); IOWAIT(); /* Higher-digit count of timer 2 */

return 0;

/* Count latch */

LatchTimer()

int count1, count2, counts;

counts = INTERVAL * (0xFFFF - count2)

+ (INTERVAL - count1);

return counts;

double total time;

main()

int start_count, stop_count;

TnitTimer();

stop_count = LatchTimer();

/* Stop count value */

total_time = (double)(stop_count-start count)

/ (double)TIMERCLK; /* Seconds */

return 0;

#include <time.h>

func()

/* Time measurement routine */

{

. . . .

```

#### 9. DEVELOPMENT OF APPLICATIONS USING MASKABLE INTERRUPTS

This chapter describes the methods of developing an application on the RTE-V850E/MA1-CB by using a maskable interrupt, and related restrictions.

#### 9.1. INTERRUPT VECTOR

The V850E/MA1 interrupt vector area of addresses 000000H to 0007FFH is fixed in the ROM, and cannot be rewritten. So, for the monitor, the following two vector areas are allocated in the SRAM:

This vector area can be rewritten by the user program. It is used if a relative jump can be executed from the interrupt vector area. The branch instruction for the relative jump is placed in the vector area in this case.

Relay vector area:

Alternate vector area:

This vector area is used by the monitor if a relative jump from the interrupt vector area cannot be executed. In this case, an instruction that saves the registers and a branch instruction for an absolute jump are placed in the interrupt vector area, and an instruction that restores the registers and a branch instruction for a relative jump to the alternate area are placed in this area.

Because the monitor can execute a relative jump from the interrupt vector area (addresses 0000000H to 00007FFH) to the alternate vector area, it branches to the alternate vector area via relay vector area.

| Alternate vector area | Relay vector area  |

|-----------------------|--------------------|

| 4F8000H to 4F87FFH    | 4F8800H to 4F8 FFH |

If, for example, an interrupt with exception code 0080H is generated, the CPU interrupt function causes a branch to address 000080H, where an instruction for causing a branch to 0080H (the offset of alternate vector area) is placed. It branches to offset address 0080H of the alternate vector area via that vector. By rewriting the alternate vector area in the destination, a branch to the user program interrupt handling routine can be caused when an interrupt is generated.

If an exception code 0080H interrupt occurs, therefore, write an instruction that branches execution to the specified interrupt processing at address 4F8080H.

The difference from an ordinary V850E/MA1 program is that a vector area is fixed in ROM, and no setting (rewriting) by a program is required. However, a program using the monitor on the RTE-V850E/MA1-CB must rewrite the vector area by the program to enable an interrupt.

A sample program for alternate vector rewriting is given below (when the relative address from the interrupt handling routine to an alternate vector area is within 22 bits).

#### 9.2. GENERAL RESTRICTIONS/NOTES

This section describes restrictions and notes relating to the debugging of an application using a maskable interrupt.

- If an interrupt is generated before alternate vector setting, or if an interrupt is generated with other

than a valid alternate vector set, a break occurs at the point where the interrupt is generated. This is

because the initial value of the alternate vector is an instruction for causing a branch to the break

handling routine of the monitor.

- 2) If the relative address from an alternate vector area to the interrupt handling routine exceeds 22 bits, the contents of at least one register must be destroyed, or a branch relay point must be created, to cause a branch to the interrupt handling routine.

- 3) The alternate vector area can be rewritten by the program or when the program is downloaded (see Section 9.3). To rewrite these areas when the program is downloaded, however, <u>rewrite only the</u> <u>interrupts that are used</u>.

- 4) All peripherals, including interrupt-related peripherals, can be initialized only with the reset switch on the board. This means that if, after a program is executed, another program is loaded, the peripherals will still be in the statuses set by the previous program. So, use the procedure below when, for a program that uses a peripheral, another program is to be loaded and executed.

- (1) Disconnect the monitor.

- (2) For resetting the board, press the reset switch of the RTE-V850E/MA1-CB.

- (3) Connect the monitor.