## RTE-VR5432-CB

### USER'S MANUAL (Rev. 2.01)

Midas lab

| Date               | Revision | Explanation of revision                                                                                                                                                                                                                                                                                            |  |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| August 15, 1999    | 1.00     | Official 1st edition                                                                                                                                                                                                                                                                                               |  |

| September 15, 1999 | 1.01     | Modification of current consumption from 2.5A (max.) to 2.0A (max.)                                                                                                                                                                                                                                                |  |

| December 29,1999   | 2.00     | <ul> <li>Change accompanied by specification change (specification change of the bus in Big Endian) for H/W version Rev.2.00</li> <li>The chapter and section which were changed are as follows.</li> <li>The description part concerning BigEndian to each.</li> <li>7.3 Address Map 9 ROM Programming</li> </ul> |  |

| April 12,2000      | 2.01     | Clerical error correction<br>5.16 CPU Connectors (JCP1, 2)<br>The maker of a connector is corrected to hirose from KEL.<br>10.3 Chip Select<br>Logical address range value is corrected.                                                                                                                           |  |

|                    |          |                                                                                                                                                                                                                                                                                                                    |  |

#### **REVISION HISTORY**

#### Notes

The specification in the case of using RTE-VR5432-CB by Big Endian in H/W Rev.2 was changed. H/W Rev.1:Byte-Swap is implemented.

H/W Rev.2:Byte Swap is not implemented.

Therefore, how to write in access to I/O space and ROM is changed.

About this point, it is not compatible.

#### **CONTENTS**

| 1. | INTRO | DUCTION                                                                       | 1  |

|----|-------|-------------------------------------------------------------------------------|----|

|    | 1.1.  | NUMERIC NOTATION                                                              | 1  |

|    |       |                                                                               |    |

| 2. | FUNC  | FIONS                                                                         | 2  |

| 3. | MA.IO | R FEATURES                                                                    | 3  |

| 0. |       |                                                                               |    |

| 4. | BASIC | SPECIFICATIONS                                                                | 3  |

| 5. | BOAR  | D CONFIGURATION                                                               | 4  |

| 0. | 5.1.  | RESET SWITCH (SW_RESET)                                                       |    |

|    | 5.2.  | POWER CONNECTOR (JPOWER)                                                      |    |

|    | 5.3.  | SWITCH 1 (SW1)                                                                |    |

|    | 5.4.  | SWITCH 2 (SW2)                                                                |    |

|    | 5.5.  | SWITCH 3 (SW3)                                                                |    |

|    | 5.6.  | SWITCH 4 (SW4)                                                                |    |

|    | 5.7.  | SWITCH 5 (SW5)                                                                |    |

|    | 5.8.  | 7SEG-LED, XXX-LED                                                             |    |

|    | 5.9.  | CLOCK SOCKET (OSC1)                                                           |    |

|    | 5.10. | ROM SOCKETS                                                                   |    |

|    | 5.11. | SERIAL CONNECTOR (JSIO1, JSIO2)                                               |    |

|    | 5.12. | PARALLEL CONNECTOR (JPRT)                                                     |    |

|    | 5.13. | ROM EMULATOR TEST PIN (JROM-EML)                                              |    |

|    | 5.14. | ICE CONNECTOR (JDCU)                                                          |    |

|    | 5.15. | JGBUS CONNECTOR (JGBUS)                                                       |    |

|    | 5.16. | CPU CONNECTORS (JCP1, 2)                                                      |    |

| ~  | CONN  | ECTION WITH THE HOST PC                                                       |    |

| 6. |       | RS-232C CONNECTION                                                            |    |

|    | 6.1.  | RS-232C CONNECTION                                                            | 11 |

| 7. | HARD  | WARE REFERENCES                                                               | 12 |

| •• | 7.1.  | RESET 12                                                                      |    |

|    | 7.2.  | INTERRUPTS                                                                    | 12 |

|    | 7.3.  | ADDRESS MAP                                                                   |    |

|    |       | 7.3.1. SRAM Space (0000-0000H to 07FF-FFFFH)                                  |    |

|    |       | 7.3.2. DRAM Space (0800-0000H to 0FFF-FFFH)                                   |    |

|    |       | 7.3.3. GBUS Space (1000-0000H to 17FF-FFFFH)                                  |    |

|    |       | 7.3.4. I/O Space (1800-0000H to 1EFF-FFFFH)                                   |    |

|    |       | 7.3.5. ROM Space (1F00-0000H to 1FFF-FFFFH)                                   |    |

|    | 7.4.  | I/O DETAILS                                                                   |    |

|    |       | 7.4.1. SRAM Controller (SRAMC B800-6000[Read/Write])                          |    |

|    |       | 7.4.2. DRAM Controller (DRAMC B800-5000[Read/Write])                          |    |

|    |       | 7.4.3. DRAM Initialization Port (DRAM_INIT B800-4000H[Write Only])            |    |

|    |       | 7.4.4. SW1 Read Port (SW1 B800-0000H [Read Only])                             |    |

|    |       | 7.4.5. SW2 Read Port (SW2 B800-1000H [Read Only])                             |    |

|    |       | 7.4.6. 7-Segment LED Display Data Output Port (7SEG-LED B800-2000 [Write Only |    |

|     |       | 19                                                                         |    |

|-----|-------|----------------------------------------------------------------------------|----|

|     |       | 7.4.7. Serial/parallel I/O (SCC0/1 LPT B900-1000 to B900-4000[Read/Write]) | 20 |

|     |       | 7.4.8. Timer (Timer B900-5000[Read/Write])                                 | 21 |

|     |       | 7.4.9. Interrupt Controller (PIC B900-0000[Read/Write])                    | 22 |

|     |       | 7.4.10. DMA Controller                                                     | 23 |

|     |       |                                                                            |    |

| 8.  |       | YCLE TIMING                                                                |    |

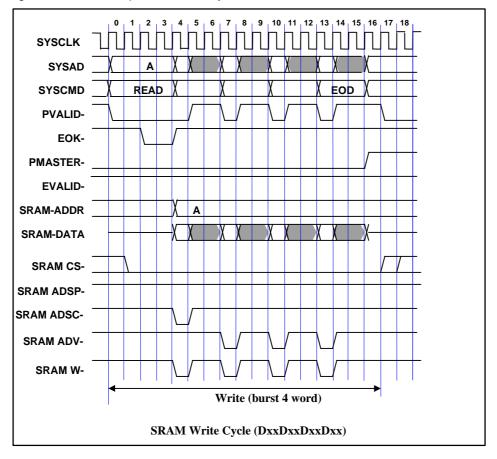

|     | 8.1.  | SRAM ACCESS                                                                |    |

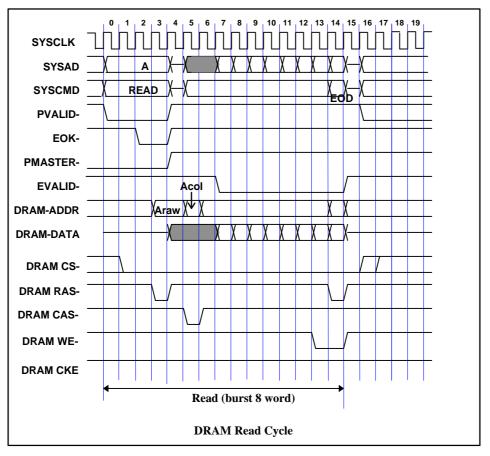

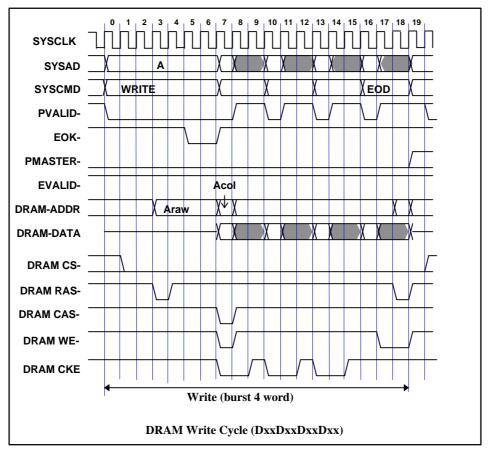

|     | 8.2   | DRAM ACCESS                                                                |    |

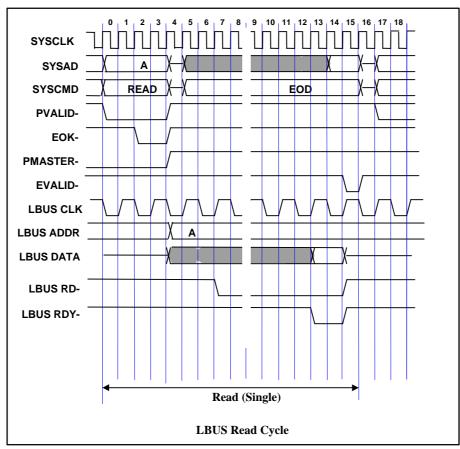

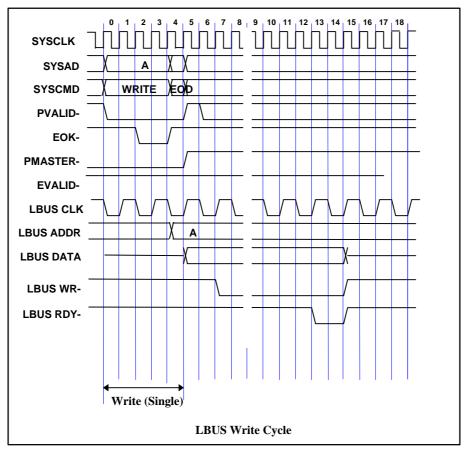

|     | 8.3.  | LOCAL BUS ACCESS                                                           |    |

|     | 8.4.  | LIST OF REQUIRED CLOCKS                                                    |    |

|     |       | 8.4.1. SRAM Access                                                         |    |

|     |       | 8.4.2. SDRAM Access                                                        | 34 |

| 9.  |       | PROGRAMMING                                                                | 35 |

| 5.  | 9.1   |                                                                            |    |

|     | 9.2   | ROM DATA ASSIGNMENT                                                        |    |

|     | 9.2   |                                                                            | 55 |

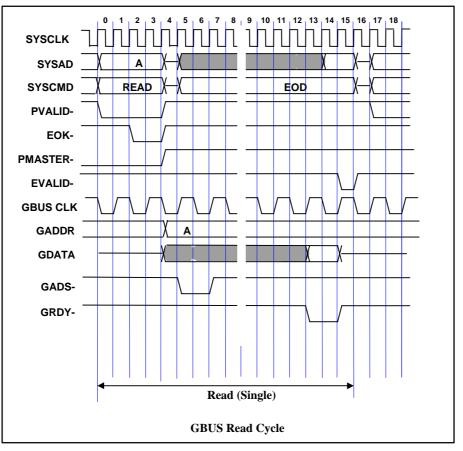

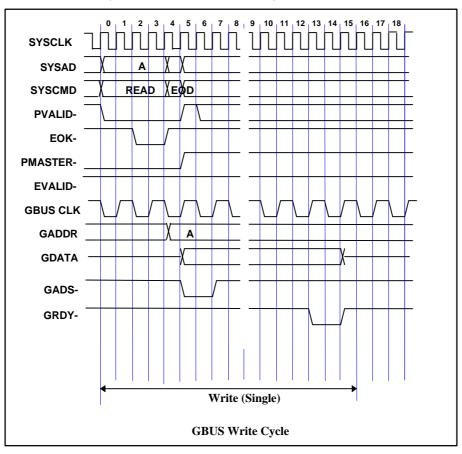

| 10. | SPECI | FIC GBUS SPECIFICATIONS                                                    | 36 |

|     | 10.1  | OVERVIEW                                                                   | 36 |

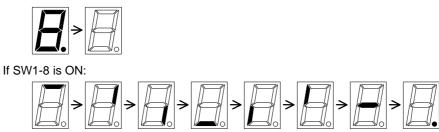

|     | 10.2  | BUS CYCLE                                                                  | 37 |

|     | 10.3  | CHIP SELECT                                                                | 38 |

|     |       |                                                                            |    |

| 11. |       |                                                                            |    |

|     | 11.1. | BOARD SETTING                                                              |    |

|     |       | 11.1.1. RTE for Win 32 Installation                                        |    |

|     |       | 11.1.2. SW1 Setting                                                        |    |

|     |       | 11.1.3. Connection of Board                                                |    |

|     | 11.2. | MULTI MONITOR                                                              |    |

|     |       | 11.2.1. 7-Segment LED on Startup                                           |    |

|     |       | 11.2.2. Monitor Work RAM                                                   |    |

|     |       | 11.2.3. Interrupt                                                          |    |

|     |       | 11.2.4INIT_SP Setting                                                      |    |

|     |       | 11.2.5. Timer Interrupt                                                    |    |

|     |       | 11.2.6. Initializing Hardware                                              |    |

|     |       | 11.2.7. Special Instruction                                                |    |

|     | 11.3. | RTE COMMANDS                                                               |    |

|     |       | 11.3.1. HELP(?)                                                            |    |

|     |       | 11.3.2. INIT                                                               |    |

|     |       | 11.3.3. VER                                                                |    |

|     |       | 11.3.4 CACHEFLUSH                                                          |    |

|     |       | 11.3.5 SHOWTLB                                                             |    |

|     |       | 11.3.6 IOREAD                                                              |    |

|     |       | 11.3.7 IOWRITE                                                             | 42 |

| 12  |       | NDIX B PARTNER MONITOR                                                     | 12 |

|     | 12.1. | BOARD SETTING                                                              |    |

|     | 12.1. | 12.1.1. SW1 Setting                                                        |    |

|     |       | 12.1.2. Connection of Board                                                |    |

|     | 12.2  | PARTNER MONITOR                                                            |    |

|     | 12.2  |                                                                            | ++ |

|     | 12                                                                                                                                                                        | 2.2.1. 7-Segment LED on Startup                                                                                                                                                                                                                                                                    | . 44                                                                        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|     |                                                                                                                                                                           | 2.2.2. ROM Monitor Work RAM                                                                                                                                                                                                                                                                        |                                                                             |

|     | 12                                                                                                                                                                        | 2.2.3. Interrupt                                                                                                                                                                                                                                                                                   | . 44                                                                        |

|     |                                                                                                                                                                           | 2.2.4. INIT_SP Setting                                                                                                                                                                                                                                                                             |                                                                             |

|     | 12                                                                                                                                                                        | 2.2.5. Remote Connection                                                                                                                                                                                                                                                                           | . 44                                                                        |

|     | 12                                                                                                                                                                        | 2.2.6. Initializing Hardware                                                                                                                                                                                                                                                                       | . 45                                                                        |

|     | 12                                                                                                                                                                        | 2.2.7. Special Instruction                                                                                                                                                                                                                                                                         | . 45                                                                        |

| 12  |                                                                                                                                                                           | X C INTERRUPT PROGRAMMING                                                                                                                                                                                                                                                                          | 16                                                                          |

| 15. |                                                                                                                                                                           | TERRUPT LIBRARY                                                                                                                                                                                                                                                                                    |                                                                             |

|     |                                                                                                                                                                           | 3.1.1. int InitlrgVect(void)                                                                                                                                                                                                                                                                       |                                                                             |

|     |                                                                                                                                                                           | 3.1.2. int TermIrqVect(void)                                                                                                                                                                                                                                                                       |                                                                             |

|     |                                                                                                                                                                           | 3.1.3. int SetIrqVect(int no, int func)                                                                                                                                                                                                                                                            |                                                                             |

|     |                                                                                                                                                                           | 3.1.4. int GetirqVect(int no)                                                                                                                                                                                                                                                                      |                                                                             |

|     |                                                                                                                                                                           | 3.1.5. void SetIPnBit(int IPn)                                                                                                                                                                                                                                                                     |                                                                             |

|     |                                                                                                                                                                           | 3.1.6. void ResIPnBit(int IPn)                                                                                                                                                                                                                                                                     |                                                                             |

|     |                                                                                                                                                                           | 3.1.7. void ei(void)                                                                                                                                                                                                                                                                               |                                                                             |

|     |                                                                                                                                                                           | 3.1.8. void di(void)                                                                                                                                                                                                                                                                               |                                                                             |

|     |                                                                                                                                                                           | ITERRUPT ROUTINE                                                                                                                                                                                                                                                                                   |                                                                             |

|     | 10.2                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                    |                                                                             |

|     | 13.3. S/                                                                                                                                                                  | AMPLE PROGRAM                                                                                                                                                                                                                                                                                      | . 47                                                                        |

|     | 13.3. S/                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                    | . 47                                                                        |

| 14. | APPENDI                                                                                                                                                                   | AMPLE PROGRAM                                                                                                                                                                                                                                                                                      | .48                                                                         |

| 14. | <b>APPENDI</b><br>14.1. TE                                                                                                                                                | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS<br>ERMINOLOGY                                                                                                                                                                                                                                      | <b>. 48</b><br>. 48                                                         |

| 14. | <b>APPENDI</b><br>14.1. TE<br><i>1</i> 2                                                                                                                                  | AMPLE PROGRAM                                                                                                                                                                                                                                                                                      | <b>48</b><br>48<br>48                                                       |

| 14. | <b>APPENDI</b><br>14.1. TE<br>14<br>14                                                                                                                                    | AMPLE PROGRAM<br><b>X C GBUS COMMON SPECIFICATIONS</b><br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle                                                                                                                                                       | <b>. 48</b><br>. 48<br>. 48<br>. 48                                         |

| 14. | <b>APPENDI</b><br>14.1. TE<br>12<br>14.2. SI                                                                                                                              | AMPLE PROGRAM<br><b>X C GBUS COMMON SPECIFICATIONS</b><br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS                                                                                                                                              | <b>. 48</b><br>. 48<br>. 48<br>. 48<br>. 48<br>. 48                         |

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.3. PI                                                                                                                         | AMPLE PROGRAM<br><b>X C GBUS COMMON SPECIFICATIONS</b><br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS                                                                                                                             | . <b>48</b><br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 53                 |

| 14. | APPENDI<br>14.1. TE<br>14<br>14<br>14.2. SI<br>14.3. PI<br>14.4. PF                                                                                                       | AMPLE PROGRAM<br><b>X C GBUS COMMON SPECIFICATIONS</b><br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS.                                                                                                | <b>. 48</b><br>. 48<br>. 48<br>. 48<br>. 48<br>. 53<br>. 54                 |

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.2. SI<br>14.3. PI<br>14.4. PF<br>14.5. AI                                                                                     | AMPLE PROGRAM<br><b>X C GBUS COMMON SPECIFICATIONS</b><br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0].                                                                          | . 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 53<br>. 54<br>. 54                |

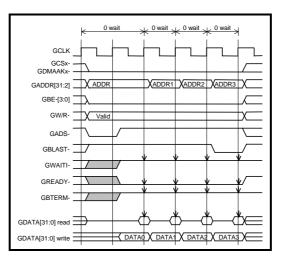

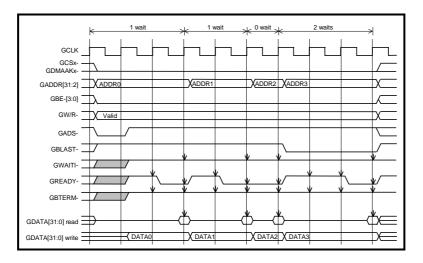

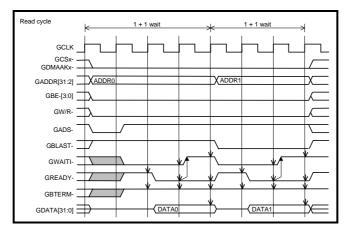

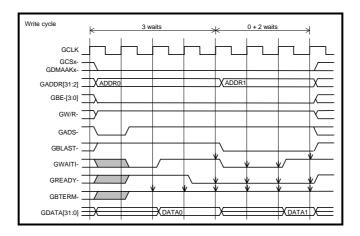

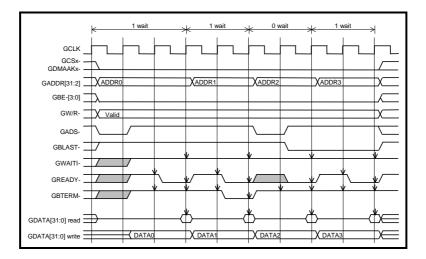

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.2. SI<br>14.3. PI<br>14.4. PI<br>14.5. AI<br>14.6. BI                                                                         | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS.<br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS.<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0]<br>JS CYCLE                                                                    | . <b>48</b><br>. 48<br>. 48<br>. 48<br>. 53<br>. 54<br>. 54<br>. 55         |

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.2. SI<br>14.3. PI<br>14.4. PF<br>14.5. AI<br>14.6. BI<br>14.6. BI                                                             | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS<br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0]<br>JS CYCLE<br>4.6.1. Single Cycle                                               | . <b>48</b><br>. 48<br>. 48<br>. 48<br>. 53<br>. 54<br>. 54<br>. 55<br>. 55 |

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.2. SI<br>14.3. PI<br>14.4. PF<br>14.5. AI<br>14.6. BI<br>14.6. BI<br>12<br>12                                                 | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS<br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle.<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0].<br>JS CYCLE<br>4.6.1. Single Cycle.<br>4.6.2. Burst Cycle                      | .48<br>.48<br>.48<br>.48<br>.53<br>.54<br>.55<br>.55<br>.55                 |

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.3. PI<br>14.4. PF<br>14.5. AI<br>14.6. BI<br>12<br>12<br>12                                                                   | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS.<br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0].<br>JS CYCLE<br>4.6.1. Single Cycle<br>4.6.2. Burst Cycle<br>4.6.3. GWAITI      | .48<br>.48<br>.48<br>.48<br>.53<br>.54<br>.55<br>.55<br>.55<br>.55          |

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.3. PI<br>14.4. PF<br>14.5. AI<br>14.6. BI<br>14.6. BI<br>12<br>12<br>12                                                       | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS<br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0]<br>JS CYCLE<br>4.6.1. Single Cycle<br>4.6.3. GWAITI-<br>4.6.4. GBTERM-           | .48<br>.48<br>.48<br>.48<br>.53<br>.54<br>.55<br>.55<br>.55<br>.55          |

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.2. SI<br>14.3. PI<br>14.4. PF<br>14.5. AI<br>14.6. BI<br>14.6. BI<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14 | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS<br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0]<br>JS CYCLE<br>4.6.1. Single Cycle<br>4.6.3. GWAITI-<br>4.6.4. GBTERM-<br>MING58 | .48<br>.48<br>.48<br>.53<br>.54<br>.55<br>.55<br>.55<br>.55<br>.55          |

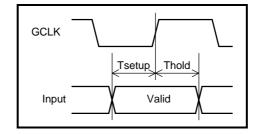

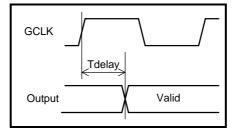

| 14. | APPENDI<br>14.1. TE<br>12<br>14.2. SI<br>14.3. PI<br>14.4. PF<br>14.5. AL<br>14.6. BU<br>12<br>14<br>14.7. TI<br>14.7. TI<br>14                                           | AMPLE PROGRAM<br>X C GBUS COMMON SPECIFICATIONS<br>ERMINOLOGY<br>4.1.1. CPU Board and Motherboard<br>4.1.2. Bus Cycle and Micro Cycle<br>GNALS<br>N ASSIGNMENTS<br>ROCESSING OF UNUSED PINS<br>LOCATING GCS-[7:0]<br>JS CYCLE<br>4.6.1. Single Cycle<br>4.6.3. GWAITI-<br>4.6.4. GBTERM-           | .48<br>.48<br>.48<br>.53<br>.54<br>.55<br>.55<br>.55<br>.55<br>.55<br>.55   |

#### 1. INTRODUCTION

The RTE-VR5432-CB is a CPU board that is designed to evaluate the NEC RISC processor.

The board features a VR5432 CPU capable of operating at a maximum speed of 167 MHz, memory, serial/parallel interface, and bus connector for expansion. As the memories, a high-speed PB-SRAM and high-capacity SDRAM are provided as standard.

These functions enable the RTE-VR5432-CB to be used for a wide variety of applications including processor performance evaluation and application program development at the initial stage, and to also be used as an engine for demonstration and simulation.

The GHS Multi or NEC PARTNER source-level debugger can be used as a development software tool with the RTE-VR5432-CB. The type of monitor to be stored in ROM depends on the debugger type. In ROM, the monitor specified at the time of purchase is stored. Even when neither of the debuggers is purchased together with the RTE-VR5432-CB, they can be purchased at anytime subsequently.

#### 1.1. NUMERIC NOTATION

This manual represents numbers according to the notation described in the following table. Hexadecimal and binary numbers may be hyphenated at every four digits, if they are difficult to read because of many digits being in each number.

| Number                | Notation rule                       | Example                                |

|-----------------------|-------------------------------------|----------------------------------------|

| Decimal number        | Only numerals are indicated.        | "10" represents number 10 in decimal.  |

| Hexadecimal<br>number | A number is suffixed with letter H. | "10H" represents number 16 in decimal. |

| Binary number         | A number is suffixed with letter B. | "10B" represents number 2 in decimal.  |

Number Notation Rules

Multi is a trademark of Green Hills Software, Inc. in the US.

#### 2. FUNCTIONS

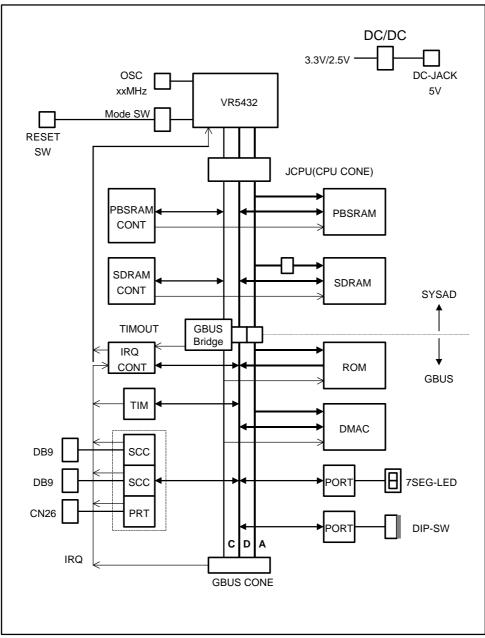

The overview of each function block of the RTE-VR5432-CB is shown below.

RTE-VR5432-CB Block Diagram

#### 3. MAJOR FEATURES

- Two types of monitor ROM are provided: one is used for the GreenHills Multi and the other for the NEC PARTNER.

- Real-time execution and evaluation at a high-level language level are possible.

- 256 Kbytes of PB-SRAM and 64 Mbytes of SDRAM are provided as standard.

- Two interfaces are provided: Serial (2 channels) and parallel (IEE1284).

- A ROM emulator and N-Wire tool can be connected.

#### 4. BASIC SPECIFICATIONS

| Processor          | VR5432                                                                  |  |

|--------------------|-------------------------------------------------------------------------|--|

| CPU clock          | 150 MHz (167 MHz max.)                                                  |  |

| Bus clock          | 60 MHz (max.)                                                           |  |

| Power supply       | +5 V, 2.0 A (max.)                                                      |  |

| Memory             |                                                                         |  |

| EPROM              | 256 KB 128 K $\times$ 16 bits (40-pin DIP) $\times$ 1 (512 Kbytes max.) |  |

| PB-SRAM            | 256 KB 32 K × 32 bits × 2                                               |  |

| SDRAM              | 64 MB 4 M $\times$ 4 bits $\times$ 4 banks $\times$ 8                   |  |

| I/O                |                                                                         |  |

| Serial interface   | Equivalent to NS16550, DB9 connector $	imes$ 2 channels                 |  |

| Parallel interface | IEEE1284 compatible, CON26 connector                                    |  |

| Timer              | mPD71054, 500-ns resolution                                             |  |

| I/O port           | LED (7 segment) display/switch input                                    |  |

| Others             |                                                                         |  |

| CPU connector      | Connector connecting all VR5432 pins                                    |  |

| GBUS connector     | RTE-CB compliant 32-bit I/F (4-GB, 32-bit bus, supporting DMA)          |  |

| Reset switch       | Push type                                                               |  |

|                    |                                                                         |  |

#### 5. BOARD CONFIGURATION

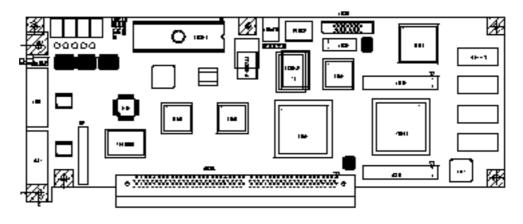

The physical layout of the major components on the RTE-VR5432-CB board is shown below. This chapter explains each component.

#### 5.1. RESET SWITCH (SW\_RESET)

SW\_RESET is a reset switch for the entire board. Pressing this switch causes all the circuits including the CPU to be reset.

#### 5.2. POWER CONNECTOR (JPOWER)

The power supplied to the JPOWER connector should be one rated as listed below.

| Voltage:          | +5 V                        |

|-------------------|-----------------------------|

| Current:          | Maximum of 2.0 A            |

| Mating connector: | Type A (5.5 mm in diameter) |

|                   |                             |

Polarity:

Note the polarity when attaching the power connector. To supply power from the JGBUS connector, do not connect a power source to JPOWER.

#### 5.3. SWITCH 1 (SW1)

SW1 is a general-purpose input port switch. The setting status can be read from an input port (see **7.4.4 SW1 Read Port (SW1 B800-0000H [Read Only])**). When the port is read, a switch being set to OFF represents 1, while its being set to ON represents 0. When the monitor ROM is used, all SW1 switches except some are already set. Set this switch for assignment with the monitor ROM by referring to the following sections and in accordance with your environment:

When using Multi, see 11.1.2 SW1 Setting.

When using PARTNER, see 12.1.1 SW1 Setting.

#### 5.4. SWITCH 2 (SW2)

SW2 selects an operation of the board by hardware. The setting of the switch can be read from an input port (see **7.4.5 SW2 Read Port (SW2 B800 to 1000H [Read Only])**).

| No. | Signal name | Factory setting | Function                                                                                                                                                                                                                                                                                               |

|-----|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FBOOT       | OFF             | Specifies resources to be allocated to the CS0 space.<br>OFF: The on-board UV-EPROM is allocated to the CS0 space.<br>ON: GCS1- space of GBUS is allocated to the CS0 space (see<br><b>10.3 CHIP SELECT</b> ).                                                                                         |

| 2   | TEST1       | OFF             | Set this signal to OFF.                                                                                                                                                                                                                                                                                |

| 3   | BCLK_LOW    | OFF             | Selects frequency of oscillator mounted on OSC1. Depending on<br>the value set, the monitor ROM changes the number of ROM and<br>SRAM wait cycles. In addition, the number of I/O wait cycles is<br>changed by hardware.<br>OFF: Bus clock exceeds 33 MHz.<br>ON: Bus clock is kept at 33 MHz or less. |

| 4   | DDDD        | OFF             | Specifies the write data rate. The Config register of the VR5432<br>must be set according to the value set here.<br>OFF: DxxDxxDxxDxx<br>ON: DDDD                                                                                                                                                      |

| 5   | TESET2      | OFF             | Must be set to OFF.                                                                                                                                                                                                                                                                                    |

| 6   | Not used    | OFF             | Must be set to OFF.                                                                                                                                                                                                                                                                                    |

| 7   | Not used    | OFF             | Must be set to OFF.                                                                                                                                                                                                                                                                                    |

| 8   | GCLK LOW    | OFF             | Must be set to OFF.                                                                                                                                                                                                                                                                                    |

#### 5.5. SWITCH 3 (SW3)

SW3 selects the type of ROM inserted in the ROM socket and performs setting related to banks.

| No. | Signal name | Factory setting | Function                                                                                                                                                                                                                                                             |  |

|-----|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | ROM_TYPE0   | OFF             | Selects the type of ROM.<br>[ROM_TYPE1, ROM_TYPE0]<br>[ OFF , OFF ]: When monitor ROM is used                                                                                                                                                                        |  |

| 2   | ROM_TYPE1   | OFF             | [ OFF , ON ]: When 27C4096 is used<br>[ ON , OFF ]: When 27C2048 is used<br>[ ON , ON ]: When 27C1024 is used                                                                                                                                                        |  |

| 3   | BANK_DIS    | OFF             | Specifies whether the upper and lower halves (banks) of ROM<br>are separated. Be sure to set this signal to OFF when monitor is<br>used.<br>OFF: Upper and lower halves of ROM are separated.<br>ON: Upper and lower halves of ROM are used as a contiguous<br>area. |  |

| 4   | Not used    | OFF             | Must be set to OFF.                                                                                                                                                                                                                                                  |  |

| 5   | Not used    | OFF             | Must be set to OFF.                                                                                                                                                                                                                                                  |  |

| 6   | Not used    | OFF             | Must be set to OFF.                                                                                                                                                                                                                                                  |  |

| 7   | MON64       | OFF             | Specifies the monitor type.<br>OFF: 32-bit mode<br>ON: 64-bit mode                                                                                                                                                                                                   |  |

| 8   | LITTLE      | OFF             | Specifies the endian.<br>OFF: Big endian<br>ON: Little endian                                                                                                                                                                                                        |  |

**Remark** If connecting a ROM emulator, set BANK\_DIS to ON, and perform the setting to use the ROMs as a continuous ROM space. (See **9.2 ROM DATA ASSIGNMENT**)

#### 5.6. SWITCH 4 (SW4)

SW4 specifies the mode of a CPU pin. When a signal of this switch is set to OFF, the corresponding CPU pin is 1; when it is set to ON, the pin is 0.

| SW4 DivMode [10] Ratio |     | DivMode [10] Ratio | Remark (* indicates factory-setting) |

|------------------------|-----|--------------------|--------------------------------------|

| 1                      | 2   |                    |                                      |

| ON                     | ON  | 0: 2:1             |                                      |

| OFF                    | ON  | 1:2.5:1            | *                                    |

| ON                     | OFF | 2: 3:1             |                                      |

| OFF                    | OFF | 3: 4:1             |                                      |

SW 4-3 is always fixed to OFF.

SW 4-4 is for testing. Always fix it to OFF.

#### 5.7. SWITCH 5 (SW5)

SW5 physically cuts the board's signal lines connected to CPU pins. All the switches are factory-set to ON (connected). The factory setting should be used in normal cases.

| No. | CPU pin name | Factory setting | Internally used resource |

|-----|--------------|-----------------|--------------------------|

| 1   | Not used     | OFF             |                          |

| 2   | INT2-        | ON              | GINT1- of GBUS           |

| 3   | INT3-        | ON              | GINT2- of GBUS           |

| 4   | INT4-        | ON              | GINT3- of GBUS           |

#### 5.8. 7SEG-LED, XXX-LED

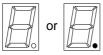

The LEDs are used to indicate statuses, as listed below. The four 7-segment LEDs are used by the monitor at startup. After that, they can be used for any user application.

| Name  | Description                                 |

|-------|---------------------------------------------|

| POWER | Lights when power is supplied to the port.  |

| SRAM  | Lights during access to the PB-SDRAM space. |

| DRAM  | Lights during access to the SDARM space.    |

| LOCAL | Lights during access to the LOCAL space.    |

| GBUS  | Lights during access to the GBUS space.     |

#### **Board LED Status**

#### 5.9. CLOCK SOCKET (OSC1)

An oscillator for generating the clock signal to be supplied to the CPU is mounted in the OSC1 socket. OSC1 is converted to the 3.3-V level, and is connected to the CPUCLK pin of the CPU. Accepts DIP 8-pin (half-type) oscillators.

When you have to cut an oscillator pin for convenience, be careful not to cut it too short, or otherwise the frame (housing) of the oscillator may touch a pin in the socket, resulting in a short-circuit occurring.

#### 5.10. ROM SOCKETS

The RTE-VR5432-CB has ROM sockets to hold 40-pin ROM chips to provide standard 128 Kbytes (64K  $\times$  16 bits). When the ROM chips used here are to be replaced, their type should be 27C1024, 27C2048, or 27C4096, and the access time should be 120 ns or less. The SW3 switch must be set again when the type of ROM is changed or a ROM emulator is connected. (See **5.5 SWITCH3 (SW3)**)

#### 5.11. SERIAL CONNECTOR (JSIO1, JSIO2)

The JSIO1 and JSIO2 connectors are used for the RS-232C interface that is controlled by the serial controller (TL16C550CPT) on the board.

JSIO1 and JSIO2 are 9-pin D-SUB RS-232C connectors (male) like that commonly used on the PC/AT. All signals on both of these connectors are converted to the RS-232C level. The figure and table below indicate the pin and signal arrangement of these connectors.

For the signals to be connected to the host, the table indicates two modes of wiring on the host: one for a 9-pin D-SUB connector, and the other for a 25-pin D-SUB connector. (Regular cross-cable wiring is used for these connections.)

|           |             |        | ut/ Connector pin number on the host sid |         |  |

|-----------|-------------|--------|------------------------------------------|---------|--|

| JSIOx pin | Signal name | output | D-SUB9                                   | D-SUB25 |  |

| 1         | DCD         | Input  |                                          |         |  |

| 2         | RxD(RD)     | Input  | 3                                        | 2       |  |

| 3         | TxD(SD)     | Output | 2                                        | 3       |  |

| 4         | DTR(DR)     | Output | 1, 6                                     | 6, 8    |  |

| 5         | GND         |        | 5                                        | 7       |  |

| 6         | DSR(ER)     | Input  | 4                                        | 20      |  |

| 7         | RTS(RS)     | Output | 8                                        | 5       |  |

| 8         | CTS(CS)     | Input  | 7                                        | 4       |  |

| 9         | RI          | Input  |                                          |         |  |

Pin Arrangement of JSIO1 and JSIO2

Connector Signals of JSIO1 and JSIO2

#### 5.12. PARALLEL CONNECTOR (JPRT)

The JPRT connector is a printer connector controlled by the serial/parallel controller (TL16PIR552). Since the connector consists of 26 header pins, a conversion cable is required to use this connector as a normal printer connector. The numbers of the connector pins and their functions are described below.

| JPRT pin                    | Signal name | Input/output | Remark        |

|-----------------------------|-------------|--------------|---------------|

| 1                           | STB-        | Output       | 10-KΩ pull-up |

| 2                           | AUTO_FD-    | Output       | 10-KΩ pull-up |

| 3                           | D0          | Output       | 10-KΩ pull-up |

| 4                           | ERROR-      | Input        | 10-KΩ pull-up |

| 5                           | D1          | Output       | 10-KΩ pull-up |

| 6                           | INIT-       | Output       | 10-KΩ pull-up |

| 7                           | D2          | Output       | 10-KΩ pull-up |

| 8                           | SELECT_IN-  | Output       | 10-KΩ pull-up |

| 9                           | D3          | Output       | 10-KΩ pull-up |

| 11                          | D4          | Output       | 10-KΩ pull-up |

| 13                          | D5          | Output       | 10-KΩ pull-up |

| 15                          | D6          | Output       | 10-KΩ pull-up |

| 17                          | D7          | Output       | 10-KΩ pull-up |

| 19                          | ACK-        | Input        | 10-KΩ pull-up |

| 21                          | BUSY        | Input        | 10-KΩ pull-up |

| 23                          | PE          | Input        | 10-KΩ pull-up |

| 25                          | SELECT      | Input        | 10-KΩ pull-up |

| 26                          | NC          |              | Not used      |

| 10,12,14,16,<br>18,20,22,24 | GND         |              |               |

JPRT Pin Arrangement

JPRT Connector Signal Table

#### 5.13. ROM EMULATOR TEST PIN (JROM-EML)

JROM-EML is a test pin used when a ROM emulator is connected. The following control signals can be input.

| Signal name   | Input/<br>output | Function                                                                                                                                          |

|---------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET-<br>(1) | Input            | All the ports are reset by inputting a low level.<br>Connect reset request signals from the ROM emulator.<br>Pulled up with $1-K\Omega$ resistor. |

| NMI-<br>(2)   | Input            | NMI is input to the CPU by inputting a low level.<br>Connect NMI request signals from the ROM emulator.<br>Pulled up with $1-K\Omega$ resistor.   |

| GND(3)        |                  | GND. Connect to GND of ROM emulator.                                                                                                              |

JROM\_EM Pin Functions

#### 5.14. ICE CONNECTOR (JDCU)

This connector is used to connect an in-circuit emulator (ICE). It enables connection of an RTE-TP type ICE. The following signals are connected.

| Pin No. | Signal name | Pin No. | Signal name |

|---------|-------------|---------|-------------|

| A1      | TRCCLK      | B1      | GND         |

| A2      | TRCDATA0    | B2      | GND         |

| A3      | TRCDATA1    | B3      | GND         |

| A4      | TRCDATA2    | B4      | GND         |

| A5      | TRCDATA3    | B5      | GND         |

| A6      | TRCEND      | B6      | GND         |

| A7      | DDI         | B7      | GND         |

| A8      | DCK         | B8      | GND         |

| A9      | DMS         | B9      | GND         |

| A10     | DDO         | B10     | GND         |

| A11     | /DRST       | B11     | NC.         |

| A12     | /BKTGIO     | B12     | NC.         |

| A13     | NC.         | B13     | +3.3V       |

JDCU2 Connector Signals

Board-side connector: KEL 8830E-026-170S

#### 5.15. JGBUS CONNECTOR (JGBUS)

This is a 32-bit data width bus connector for expansion purposes. For details, see **10 SPECIFIC GBUS SPECIFICATIONS** and **14 APPENDIX C GBUS COMMON SPECIFICATIONS**.

#### 5.16. CPU CONNECTORS (JCP1, 2)

The CPU connector signals are directly linked to the VR5432. Since these signals are used in the board, caution is required when pulling out signals from JCPU.

| JCPU pin<br>No. | Signal name | JCPU pin<br>No. | Signal name |

|-----------------|-------------|-----------------|-------------|

| 1               | +5V         | 2               | GND         |

| 3               | SYSAD31     | 4               | SYSAD30     |

| 5               | SYSAD29     | 6               | SYSAD28     |

| 7               | SYSAD27     | 8               | SYSAD26     |

| 9               | SYSAD25     | 10              | SYSAD24     |

| 11              | +5V         | 12              | GND         |

| 13              | SYSAD23     | 14              | SYSAD22     |

| 15              | SYSAD21     | 16              | SYSAD20     |

| 17              | SYSAD19     | 18              | SYSAD18     |

| 19              | SYSAD17     | 20              | SYSAD16     |

| 21              | +3.3V       | 22              | GND         |

| 23              | SYSAD15     | 24              | SYSAD14     |

| 25              | SYSAD13     | 26              | SYSAD12     |

| 27              | SYSAD11     | 28              | SYSAD10     |

| 29              | SYSAD9      | 30              | SYSAD8      |

| 31              | +3.3V       | 32              | GND         |

| 33              | SYSAD7      | 34              | SYSAD6      |

| 35              | SYSAD5      | 36              | SYSAD4      |

| 37              | SYSAD3      | 38              | SYSAD2      |

| 39              | SYSAD1      | 40              | SYSAD0      |

| 41              | +2.7V       | 42              | GND         |

| 43              | /NMI        | 44              | /INT0       |

| 45              | /INT1       | 46              | /INT2       |

| 47              | /INT3       | 48              | /INT4       |

| 49              | +2.7V       | 50              | GND         |

| 51              | no use      | 52              | no use      |

#### JCPU1 Connector

| JCPU pin<br>No. | Signal name | JCPU pin<br>No. | Signal name |

|-----------------|-------------|-----------------|-------------|

| 1               | +5V         | 2               | GND         |

| 3               | SYSCMD4     | 4               | SYSCMD3     |

| 5               | SYSCMD2     | 6               | SYSCMD1     |

| 7               | SYSCMD0     | 8               | no use      |

| 9               | no use      | 10              | no use      |

| 11              | +5V         | 12              | GND         |

| 13              | /EVALID     | 14              | /SYSRESET   |

| 15              | /EREQ       | 16              | /PMASTER    |

| 17              | /EOK        | 18              | /PVALID     |

| 19              | /PREQ       | 20              | no use      |

| 21              | +3.3V       | 22              | GND         |

| 23              | SYSADC3     | 24              | SYSAD2      |

| 25              | SYSADC1     | 26              | SYSADC0     |

| 27              | SYSCLK2     | 28              | no use      |

| 29              | +3.3V       | 30              | GND         |

| 31              | JTDO        | 32              | JTDI        |

| 33              | JTCK        | 34              | JTMS        |

| 35              | TRISTATE    | 36              | /COLDRESET  |

| 37              | ENDIAN      | 38              | no use      |

| 39              | +2.7V       | 40              | GND         |

| 41              | DIVMODE0    | 42              | DIVMODE1    |

| 43              | TRCEND      | 44              | TRCDATA3    |

| 45              | TRCDATA2    | 46              | TRCDATA1    |

| 47              | TRCDATA0    | 48              | /BKTGIO     |

| 49              | +2.7V       | 50              | TRCCLK      |

| 51              | no use      | 52              | no use      |

JCPU2

Connector: Hirose, board side: FX2-52P-1.27SV, other side: FX2-52S-1.27SV

#### 6. CONNECTION WITH THE HOST PC

#### 6.1. RS-232C CONNECTION

RS-232C connect the host machine using the monitor ROM by means of the following procedure:

- <1> Get an optional RS-232C cable and a power supply.

- <2> Set and check the setting of the switches on the board. Specify a baud rate by using SW1 (see 11.1.2 SW1 Setting and 12.1.1 SW1 Setting).

- <3> Connect the JSIO1 connector and host machine with the RS-232C cable, and supply power to the JPOWER connector. Confirm that the POWER-LED on the board lights and that the 7segment LED indicating that the monitor has started lights.

If the LED does not light, turn off the power immediately, and check the connection.

<4> Start the debugger on the host machine, and connect it via the RS-232C interface. If an error occurs, confirm the connection of the serial cable and the setting of the switches (especially, baud rate). For the method and procedure of starting the debugger, see the debugger manual.

Place the board on an insulating material. If a conductive material touches the board while power is supplied to the board, the board may malfunction.

#### 7. HARDWARE REFERENCES

This chapter describes the hardware of the RTE-VR5432-CB.

#### 7.1. RESET

Resets are effected by the causes listed below. They are handled as cold reset of the CPU, and result in system reset of the control circuits on the board.

- Power-on reset: Triggered at power-on of the board.

- Reset switch: Triggered by Reset switch (SW RST) provided on the board.

- GBUS reset: Reset request from the JGBUS connector.

- JROM\_reset: Input from Pin No. 1 (RESET-) of the JROM\_EML connector. (See 5.13 ROM EMULATOR TEST PIN (JROM-EML).)

- DCU reset: Reset request from the in-circuit emulator. (See 5.13 ROM EMULATOR TEST PIN (JROM-EML).)

#### 7.2. INTERRUPTS

Interrupts sources from CPU external are as follows.

| Interrupt | Source          | Reference |

|-----------|-----------------|-----------|

| NMI-      | JROM_EML (NMI-) | 5.13      |

| INT0-     | PIC INTOM       | 7.4.9     |

| INT1-     | PIC INT1M       | 7.4.9     |

| INT2-     | GBUS_INT1-      |           |

| INT3-     | GBUS_INT2-      |           |

| INT4-     | GBUS_INT3-      |           |

**Memo** For the programming method using interrupts in the monitor environment, see **13 APPENDIX C INTERRUPT PROGRAMMING**.

#### 7.3. ADDRESS MAP

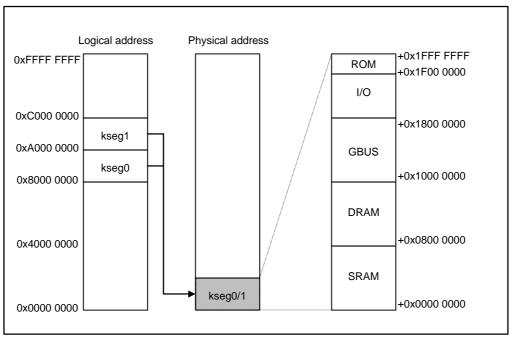

The board's address allocation is as follows.

#### Address Map

When a program is executed using a remote monitor, this is done using the kernel space 8000-0000H to BFFF-FFFFH without using TLB mapping. The physical address is determined by adding 8000-0000H when using a cache, or adding A000-0000H when not using a cache.

#### 7.3.1. SRAM Space (0000-0000H to 07FF-FFFFH)

Two PB-SRAM devices, each consisting of 32 Kbytes  $\times$  32 bits, are provided as SRAM. The total capacity is therefore 256 Kbytes. Access with 0 waits is possible up to the maximum bus clock, but wait emulation inserting 0 to 3 clocks of wait is also possible. (See **7.4.1 SRAM Controller (SRAMC B800-6000[Read/Write])**).

Since the high-order bits of the address lines are not decoded, an image appears every 256 Kbytes. Access can be performed to both cached and non-cached space.

#### 7.3.2. DRAM Space (0800-0000H to 0FFF-FFFH)

Eight SDRAM devices, each consist of 4 Mbytes  $\times$  4 bits  $\times$  4 banks are provided as DRAM. The total capacity is therefore 64 Mbytes. SDRAM settings must be performed prior to SRAM use. (See **7.4.2 DRAM Controller (DRAMC B800-5000[Read/Write])**). Since the high-order bits of the address lines are not decoded, an image appears every 64 Mbytes. Access can be performed to both cached and non-cached space.

#### 7.3.3. GBUS Space (1000-0000H to 17FF-FFFH)

Regarding the GBUS area, the access space is mapped to GBUS. For details, see **10 SPECIFIC GBUS SPECIFICATIONS**. Access to both cached and non-cached space is possible from the board, but allocate use according to the resources of the access destination.

#### 7.3.4. I/O Space (1800-0000H to 1EFF-FFFFH)

This space (memory mapped I/O) is allocated by the I/O device for controlling the functions of the board. For details on the I/O map, etc., see **7.4 I/O DETAILS**. Access is performed to non-cached space.

#### 7.3.5. ROM Space (1F00-0000H to 1FFF-FFFFH)

Regarding the ROM space, either 128 Kbytes (64 K words  $\times$  16 bits), 256 Kbytes (128 K words  $\times$  16 bits), or 512 Kbytes (256 K words  $\times$  16 bits) of UV-EPROM with an access time of 120 ns or less can be mounted. The type of ROM and the usage method are set with SW3. (See **5.5 SWITCH 3 (SW3)**.) Since the high-order bits of the address lines are not decoded, an image appears for each ROM capacity.

The number of ROM waits varies depending on the SW2-3 (BCLK\_LOW) settings, but an access time of 120 ns or more is secured for the maximum frequency.

Access can be performed from both cached and non-cached spaces.

#### 7.4. I/O DETAILS

A memory access controller, DUART/LPT, timer, and interrupt controller are among the I/O devices mapped in the memory space. The various I/O allocations are as follows.

I/O Map

Since kernel non-cached space access is assumed for these I/Os, logical addresses are used in the following explanation.

#### 7.4.1. SRAM Controller (SRAMC B800-6000[Read/Write])

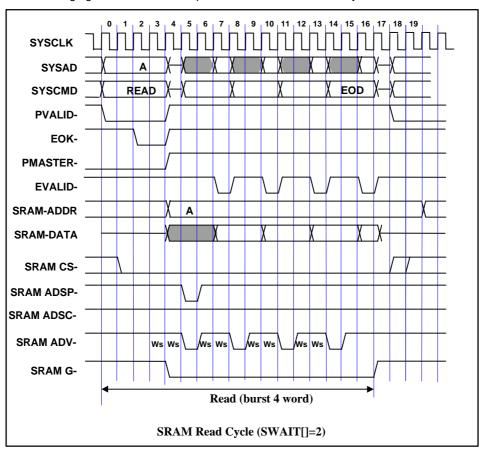

The SWAIT register performs wait control for the SRAM space. 0 to 3 waits can be set for the read cycle using this register. The register allocation is as follows.

|                    | Deviator    | Data bus |    |        |        |

|--------------------|-------------|----------|----|--------|--------|

| Logical address    | Register    | D3       | D2 | D1     | D0     |

| <b>B800</b> -6000H | SRAMC SWAIT | 0        | 0  | SWAIT1 | SWAIT0 |

SWAIT[1..0]: Sets the number of waits during SRAM read.

| SW | AIT | Number of CDAM read write |                   |  |

|----|-----|---------------------------|-------------------|--|

| 1  | 0   | Number of SRAM read waits |                   |  |

| 0  | 0   | 0                         | Recommended value |  |

| 0  | 1   | 1                         |                   |  |

| 1  | 0   | 2                         |                   |  |

| 1  | 1   | 3                         | (Reset value)     |  |

#### 7.4.2. DRAM Controller (DRAMC B800-5000[Read/Write])

DRAMC sets the access conditions. The register allocation is as follows.

|                    |           | Data bus |      |      |      |

|--------------------|-----------|----------|------|------|------|

| Logical address    | Register  | D3       | D2   | D1   | D0   |

| <b>B800</b> -5000H | DRAMC RCD | 0        | 0    | RCD1 | RCD0 |

| -5010H             | DRAMC RP  | 0        | 0    | RP1  | RP0  |

| -5020H             | DRAMC RC  | 0        | RC2  | RC1  | RC0  |

| -5030H             | DRAMC RRC | 0        | RRC2 | RRC1 | RRC0 |

| -5040H             | DRAMC RAS | 0        | RAS2 | RAS1 | RAS0 |

| -5050H             | DRAMC LAT | 0        | 0    | LAT1 | LAT0 |

| -5060H             | DRAMC RSC | 0        | 0    | RSC1 | RSC0 |

| -5070H             | DRAMC AP  | 0        | 0    | 0    | AP   |

RCD[1..0]: Sets SDRAM parameter tRCD (Delay ACT to read/write).

| R | CD | 4D.C.D.  | Demer             |  |

|---|----|----------|-------------------|--|

| 1 | 0  | tRCD     | Remark            |  |

| 0 | 0  |          |                   |  |

| 0 | 1  |          |                   |  |

| 1 | 0  | 2 SYSCLK | Recommended value |  |

| 1 | 1  | 3 SYSCLK | (Reset value)     |  |

**Memo** Use the recommended value. The operation is not guaranteed if a value other than the recommended value is used.

RP[1..0]: Sets SDRAM parameter tRP (PRE to ACT/REF).

| R | P |          | Demed             |

|---|---|----------|-------------------|

| 1 | 0 | tRP      | Remark            |

| 0 | 0 |          |                   |

| 0 | 1 | -        |                   |

| 1 | 0 | 2 SYSCLK | Recommended value |

| 1 | 1 | 3 SYSCLK | (Reset value)     |

**Memo** Use the recommended value. The operation is not guaranteed if a value other than the recommended value is used.

|   | RC |   | 120      | Deved             |

|---|----|---|----------|-------------------|

| 2 | 1  | 0 | tRC      | Remark            |

| 0 | 0  | 0 |          |                   |

| 0 | 0  | 1 |          |                   |

| 0 | 1  | 0 |          |                   |

| 0 | 1  | 1 |          |                   |

| 1 | 0  | 0 |          |                   |

| 1 | 0  | 1 | 5 SYSCLK | Recommended value |

| 1 | 1  | 0 | 6 SYSCLK |                   |

| 1 | 1  | 1 | 7 SYSCLK | (Reset value)     |

RC[2..0]: Sets SDRAM parameter tRC (ACT to REF/ACT).

**Memo** Use the recommended value. The operation is not guaranteed if a value other than the recommended value is used.

RRC[2..0]: Sets SDRAM parameter tRRC (REF to REF/ACT).

|   | RRC |   | 1000     | Demerk            |

|---|-----|---|----------|-------------------|

| 2 | 1   | 0 | tRRC     | Remark            |

| 0 | 0   | 0 |          |                   |

| 0 | 0   | 1 |          |                   |

| 0 | 1   | 0 |          |                   |

| 0 | 1   | 1 |          |                   |

| 1 | 0   | 0 |          |                   |

| 1 | 0   | 1 |          |                   |

| 1 | 1   | 0 | 6 SYSCLK | Recommended value |

| 1 | 1   | 1 | 7 SYSCLK | (Reset value)     |

**Memo** Use the recommended value. The operation is not guaranteed if a value other than the recommended value is used.

RAS[2..0]: Sets SDRAM parameter tRC (ACT to PRE).

|   | RAS |   | 4D A C   | Demorte           |

|---|-----|---|----------|-------------------|

| 2 | 1   | 0 | tRAS     | Remark            |

| 0 | 0   | 0 |          |                   |

| 0 | 0   | 1 |          |                   |

| 0 | 1   | 0 |          |                   |

| 0 | 1   | 1 |          |                   |

| 1 | 0   | 0 | 4SYSCLK  | Recommended value |

| 1 | 0   | 1 |          |                   |

| 1 | 1   | 0 |          |                   |

| 1 | 1   | 1 | 7 SYSCLK | (Reset value)     |

**Memo** Use the recommended value. The operation is not guaranteed if a value other than the recommended value is used.

LAT[1..0]: Sets SDRAM parameter tLAT (/CAS latency).

| LA | ٩T | 4 AT     | Demort            |

|----|----|----------|-------------------|

| 1  | 0  | tLAT     | Remark            |

| 0  | 0  |          |                   |

| 0  | 1  |          |                   |

| 1  | 0  | 2 SYSCLK | Recommended value |

| 1  | 1  | 3 SYSCLK | (Reset value)     |

**Memo** Use the recommended value. The operation is not guaranteed if a value other than the recommended value is used.

RSC[1..0]: Sets SDRAM parameter tRSC (Mode Register Set Cycle Time).

| RS | SC | tRSC     | Remark            |

|----|----|----------|-------------------|

| 1  | 0  | ikse     | Remark            |

| 0  | 0  |          |                   |

| 0  | 1  | -        |                   |

| 1  | 0  | 2 SYSCLK | Recommended value |

| 1  | 1  | 3 SYSCLK | (Reset value)     |

**Memo** Use the recommended value. The operation is not guaranteed if a value other than the recommended value is used.

AP: Sets whether to use the SDRAM automatic precharge function.

| AP | Automatic precharge | Remark      |

|----|---------------------|-------------|

| 0  | Use                 |             |

| 1  | Don't use           | Reset value |

#### 7.4.3. DRAM Initialization Port (DRAM\_INIT B800-4000H[Write Only])

SDRAM is initialized based on the DRAMC setting value. Data is don't care. The Mode Register Set command of SDRAM is issued when output is performed.

This port is used to write the parameters set for the ports to SDRAM. After setting all the parameters to the ports, output them to this port as the last step.

#### 7.4.4. SW1 Read Port (SW1 B800-0000H [Read Only])

This port is used to read the status of SW1. The table below indicates the data format.

| Dhuming La dalar an | Data bus |     |     |     |     |     |     | Octilian |         |

|---------------------|----------|-----|-----|-----|-----|-----|-----|----------|---------|

| Physical address    | D7       | D6  | D5  | D4  | D3  | D2  | D1  | D0       | Setting |

| B800000H            | SW1      | SW1 | SW1 | SW1 | SW1 | SW1 | SW1 | SW1      | 0 = ON  |

| input               | -8       | -7  | -6  | -5  | -4  | -3  | -2  | -1       | 1 = OFF |

SW1-1 corresponds to switch 1 of SW1, while SW1-8 corresponds to switch 8 of SW1. When a bit of the corresponding switch is set to ON, 0 is read. When it is set to OFF, 1 is read. SW1 is used to set the operation of the monitor. For how to set this switch, see **11.1.2 SW1 Setting** and **12.1.1 SW1 Setting**.

#### 7.4.5. SW2 Read Port (SW2 B800-1000H [Read Only])

This port is used to read the status of SW2. The data format of this port is shown in the table below.

| Dhuaisal addusas | Data bus |     |     |     |     |     |     |     | Catting |  |

|------------------|----------|-----|-----|-----|-----|-----|-----|-----|---------|--|

| Physical address | D7       | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Setting |  |

| B801000H         | SW2      | SW2 | SW2 | SW2 | SW2 | SW2 | SW2 | SW2 | 0 = ON  |  |

| input            | -8       | -7  | -6  | -5  | -4  | -3  | -2  | -1  | 1 = OFF |  |

SW2-1 corresponds to bit 1 of SW2, and SW2-8 corresponds to bit 8 of SW2. When a bit of the corresponding switch is set to ON, 0 is read; when it is set to OFF, 1 is read. SW2 is used to switch the hardware operation. For the function of each switch, see **5.4 SWITCH2 (SW2)**.

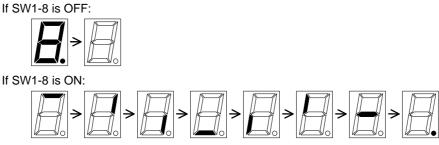

#### 7.4.6. 7-Segment LED Display Data Output Port (7SEG-LED B800-2000 [Write Only])

This port sets the data to be displayed on the four 7-segment LED. The table below indicates the data format. When a bit is set to 0, the corresponding segment is turned on.

| La siant a data an |      | Data |      |      |      |      |      |      |                |

|--------------------|------|------|------|------|------|------|------|------|----------------|

| Logical address    | D731 | D630 | D529 | D428 | D327 | D226 | D125 | D024 | Setting        |

| B800-2000H         | LED1 |                |

| output             | -DP  | -G   | -F   | -E   | -D   | -C   | -B   | -A   |                |

| B800-2001H         | LED2 |                |

| output             | -DP  | -G   | -F   | -E   | -D   | -C   | -B   | -A   | 0 = Turned on  |

| B800-2002H         | LED3 | 1 = Turned off |

| output             | -DP  | -G   | -F   | -E   | -D   | -C   | -B   | -A   |                |

| B800-2003H         | LED4 |                |

| output             | -DP  | -G   | -F   | -E   | -D   | -C   | -B   | -A   |                |

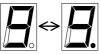

The figure below illustrates the correspondence between the bits and the segments of the 7-segment LED.

#### 7.4.7. Serial/parallel I/O (SCC0/1 LPT B900-1000 to B900-4000[Read/Write])

The TL16PIR552 (dual UART with 1284 parallel port) made by Texas Instruments is used as the UART/printer. The TL16PIR552 provides two UART channels and an IEEE1284-compliant bidirectional printer port (1 channel). The UART send/receive block features a 16-character FIFO buffer, and a function to automatically control the RTS/CTS flow is provided, which reduces overrun errors with a minimum of interrupts.

The TL16PIR552 registers are allocated as indicated in the table. For the functions of the registers, see the TL16PIR552 manual. (The TL16PIR552 manual can be obtained in the TI&ME corner in the homepage of Texas Instruments (http://www.ti.com/).

| Address                | Function        | Read           | Write         |

|------------------------|-----------------|----------------|---------------|

| B900-1000              | UART-CH#0       | RBR/DLL        | THR/DLL       |

| B900-1010              |                 | IER/DLM        | IER/DLM       |

| B900-1020              |                 | IIR            | FCR           |

| B900-1030              |                 | LCR            | LCR           |

| B900-1040              |                 | MCR            | MCR           |

| B900-1050              |                 | LSR            | LSR           |

| B900-1060              |                 | MSR            | MSR           |

| B900-1070              |                 | SCR            | SCR           |

| B900-2000              | UART-CH#1       | RBR/DLL        | THR/DLL       |

| B900-2010              |                 | IER/DLM        | IER/DLM       |

| B900-2020              |                 | IIR            | FCR           |

| B900-2030              |                 | LCR            | LCR           |

| B900-2040              |                 | MCR            | MCR           |

| B900-2050              |                 | LSR            | LSR           |

| B900-2060              |                 | MSR            | MSR           |

| B900-2070              |                 | SCR            | SCR           |

| B900-3000              | PRINTER(PPCS-)  | DATA           | DATA/ECPAFIFO |

| B900-3010              |                 | DSR            |               |

| B900-3020              |                 | DCR            | DCR           |

| B900-3030              |                 | EPPADDR        | EPPADDR       |

| B900-3040 to B900-3070 |                 | EPPDATA        | EPPDATA       |

| B900-4000              | PRINTER(ECPCS-) | PPDATAFIFO/    | PPDATAFIFO/   |

|                        |                 | TESTFIFO/CNFGA | TESTFIFO      |

| B900-4010              |                 | CNFGB          |               |

| B900-4020              |                 | ECR            | ECR           |

TL16PIR552 Register Allocation

A 16-MHz clock is connected to the XIN input of the TL16PIR552.