# **RTE-V832-PC**

## USER'S MANUAL (Rev. 1.04)

Midas lab

## **REVISION HISTORY**

| Date               | REV. | Chapter | Explanation of revision                                                                                                                            |  |

|--------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| September 10, 1998 | 1.02 |         | First edition                                                                                                                                      |  |

| February 2, 1999   | 1.03 | 11.1    | Revised RFC set value                                                                                                                              |  |

| December 26, 2000  | 1.04 | 8.9     | The interrupt input from the printer of PIC is changed into the rising edge from high level. The board of revision newer than Rev.2.1 corresponds. |  |

|                    |      |         |                                                                                                                                                    |  |

|                    |      |         |                                                                                                                                                    |  |

## **CONTENTS**

| 1. | INTR  | ODUCTION                                                         | 1   |

|----|-------|------------------------------------------------------------------|-----|

|    | 1.1.  | NUMERIC NOTATION                                                 | 1   |

|    |       |                                                                  |     |

| 2. | FUNC  | TIONS                                                            | 1   |

| 3. | NA 10 | DR FEATURES                                                      | 2   |

| э. | WAJ   | JR FEATURES                                                      | Z   |

| 4. | BASI  | C SPECIFICATIONS                                                 | 2   |

| 5. | BOAI  | RD CONFIGURATION                                                 | 3   |

|    | 5.1.  | RESET SWITCH (RESET)                                             | 3   |

|    | 5.2.  | POWER JACK (JPOWER)                                              | 3   |

|    | 5.3.  | SWITCH 1 (SW1)                                                   | 3   |

|    | 5.4.  | SWITCH 2 (SW2)                                                   | 4   |

|    | 5.5.  | SWITCH 3 (SW3)                                                   | 4   |

|    | 5.6.  | SWITCH 4 (SW4)                                                   | 5   |

|    | 5.7.  | LED                                                              | 5   |

|    | 5.8.  | TEST PINS FOR ROM EMULATOR (JROM_EM)                             |     |

|    | 5.9.  | CLOCK SOCKET (OSC1)                                              | 6   |

|    | 5.10. | ROM SOCKETS                                                      | 6   |

|    | 5.11. | DMARQ0-, DMARQ1- SEPARATION JUMPER (JP1)                         | 6   |

|    | 5.12. | TIMER CLOCK FREQUENCY SELECT JUMPER (JP2)                        | 6   |

|    | 5.13. | AUDIO INPUT LEVEL SELECT JUMPERS (JP3, JP4, JP5, JP6)            | 6   |

|    | 5.14. | SERIAL CONNECTOR (JSIO1, JSIO2)                                  | 7   |

|    | 5.15. | PARALLEL CONNECTOR (JPRT)                                        | 8   |

|    | 5.16. | AUDIO MINI-JACKS (JIN-R, JIN-L, JLINEOUT)                        | 8   |

|    | 5.17. | DEBUGGING CONNECTOR (JDCU)                                       | 9   |

|    | 5.18. | CPU CONNECTOR (JCPU-1, JCPU-2)                                   | .10 |

|    | 5.19. | EXTENSION BUS CONNECTOR (JEXT)                                   | .11 |

| 6. | CON   | NECTION WITH THE HOST PC                                         | 40  |

| 0. | 6.1.  | STANDALONE USE OF THE BOARD (RS-232C CONNECTION)                 |     |

|    | 6.2.  | INSERTING IN PCI SLOT (PCI BUS CONNECTION )                      |     |

|    | 0.2.  | INSERTING IN FCI SECT (FCI BUS CONNECTION )                      | .12 |

| 7. | HAR   |                                                                  | .13 |

|    | 7.1.  | MEMORY AND I/O MAP                                               | .13 |

| 8. | I/O M | AP                                                               | .15 |

|    | 8.1.  | I/O LIST                                                         | .15 |

|    | 8.2.  | DIPSW2 READ PORT (4500-0000H [READ ONLY])                        | .16 |

|    | 8.3.  | DIPSW1 READ PORT (4500-1000H [READ ONLY])                        |     |

|    | 8.4.  | 7-SEGMENT LED DISPLAY DATA OUTPUT PORT (4500-2000H [WRITE ONLY]) |     |

|    | 8.5.  | COMMAND REGISTER (4500-5000H [READ/WRITE])                       |     |

|    | 8.6.  | EXT-IO HIGH-ORDER ADDRESS SETTING REGISTER                       |     |

|    |       | (4500-6000H [READ/WRITE])                                        | .17 |

|    | 8.7.  | UART/PRINTER (TL16PIR552) (4500-8000H TO 4500-A03EH)             |     |

|    | 8.8.  | TIC (mPD71054) (4500-B000H TO 4500-B00CH)                        |     |

|    | 8.9.  | INTERRUPT CONTROLLER (PIC) (4500-D000H TO 4500-D018H)            |     |

|    |       |                                                                  |     |

|     | 8.10. | AUDIO CONTROLLER (AUDCNT) (4580-0000H TO 4580-0010H, 4580-200                                                                       | 0H)21                |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 8.11. | mPD63310 REGISTER (4580-1000H TO 4580-100FH)                                                                                        | 23                   |

|     |       |                                                                                                                                     |                      |

| 9.  |       | RRUPTS AND DMA                                                                                                                      |                      |

|     | 9.1.  | INTERRUPT                                                                                                                           |                      |

|     | 9.2.  |                                                                                                                                     |                      |

|     | 9.3.  | DMA REQUEST                                                                                                                         | 25                   |

| 10. | EXT-  | BUS                                                                                                                                 |                      |

|     |       | PIN ARRANGEMENT                                                                                                                     |                      |

|     |       | SIGNALS                                                                                                                             |                      |

|     |       | CONNECTION OF DATA BUS                                                                                                              |                      |

|     |       | 10.3.1. 16-Bit Data Bus CPU (Reference)                                                                                             |                      |

|     |       | 10.3.2. 32-Bit Data Bus CPU (with V832)                                                                                             |                      |

|     | 10.4. | TIMING                                                                                                                              |                      |

|     |       | APPLICABLE CONNECTORS                                                                                                               |                      |

|     |       | NOTES ON USE                                                                                                                        |                      |

|     |       |                                                                                                                                     |                      |

| 11. |       | TWARE                                                                                                                               | -                    |

|     |       |                                                                                                                                     |                      |

|     |       |                                                                                                                                     |                      |

|     | -     | USING TIMERS                                                                                                                        | -                    |

|     | 11.4. | AUDIO I/O                                                                                                                           | 35                   |

| 12. | DEVE  | ELOPMENT OF APPLICATIONS USING MASKABLE INTERRUPTS                                                                                  |                      |

|     |       | INTERRUPT VECTOR                                                                                                                    |                      |

|     |       | INTERNAL INSTRUCTION RAM                                                                                                            |                      |

|     |       | GENERAL RESTRICTIONS/NOTES                                                                                                          |                      |

|     |       | RESTRICTIONS ON BREAK POINTS IN THE INTERRUPT HANDLING                                                                              |                      |

|     |       |                                                                                                                                     |                      |

| 13. |       |                                                                                                                                     |                      |

|     | 13.1. | BOARD SETTING                                                                                                                       |                      |

|     |       | 13.1.1. RTE for Win 32 Installation                                                                                                 |                      |

|     |       | 13.1.2. SW1 Setting                                                                                                                 |                      |

|     | 40.0  | 13.1.3. Connection of Board                                                                                                         |                      |

|     | 13.2. | MULTI MONITOR                                                                                                                       |                      |

|     |       | 13.2.1. Monitor Work RAM                                                                                                            |                      |

|     |       | 13.2.2. Interrupt                                                                                                                   |                      |

|     |       | 13.2.3. Interrupt for Forced Break                                                                                                  |                      |

|     |       | 13.2.4INIT_SP Setting                                                                                                               |                      |

|     |       | 13.2.5. Remote Connection                                                                                                           |                      |

|     |       | 13.2.6. Monitor Execution Area                                                                                                      |                      |

|     | 10.0  | 13.2.7. Special Instruction                                                                                                         | 41                   |

|     | 13.3. |                                                                                                                                     | 40                   |

|     |       | RTE COMMANDS                                                                                                                        |                      |

|     |       | RTE COMMANDS                                                                                                                        | 42                   |

|     |       | RTE COMMANDS         13.3.1.       HELP(?)         13.3.2.       INIT                                                               | 42<br>42             |

|     |       | RTE COMMANDS         13.3.1.       HELP(?)         13.3.2.       INIT         13.3.3.       VER                                     | 42<br>42<br>42       |

|     |       | RTE COMMANDS         13.3.1.       HELP(?)         13.3.2.       INIT         13.3.3.       VER         13.3.4.       INB, INH, INW | 42<br>42<br>42<br>42 |

|     |       | RTE COMMANDS         13.3.1.       HELP(?)         13.3.2.       INIT         13.3.3.       VER                                     |                      |

|     |       |          | ICTR Command               |    |

|-----|-------|----------|----------------------------|----|

|     |       | 13.3.8.  | PLLCR Command              |    |

|     |       | 13.3.9.  | •••••                      |    |

|     |       | 13.3.10. | SFR Command                | 43 |

| 14. | APPE  | NDIX B   | PARTNER MONITOR            | 44 |

|     | 14.1. | BOARD    | SETTING                    | 44 |

|     |       | 14.1.1.  | SW1 Setting                | 44 |

|     | 14.2. | PARTN    | ER MONITOR                 | 45 |

|     |       | 14.2.1.  | Monitor Work RAM           | 45 |

|     |       | 14.2.2.  | Interrupt                  | 45 |

|     |       | 14.2.3.  | Interrupt for Forced Break | 45 |

|     |       | 14.2.4.  | SP Setting                 | 45 |

|     |       | 14.2.5.  | Remote Connection          | 45 |

|     |       | 14.2.6.  | Monitor Execution Area     |    |

|     |       | 14.2.7.  | Special Instruction        | 45 |

|     |       |          |                            |    |

## 1. INTRODUCTION

The **RTE-V832-PC** is an evaluation board, conforming to the PCI bus interface, that is designed to evaluate the NEC V832 RISC processor. This board can be inserted into the PCI slot of a DOS/V-compatible machine.

The board features a V832 capable of operating at a maximum speed of 143 MHz, memory, serial and parallel interfaces, and inputs/outputs such as audio inputs/outputs. As the memories, a high-speed SRAM and high-capacity SDRAM are provided as standard. The SDRAM is controlled by using the internal memory controller of the V832.

These functions enable the RTE-V832-PC to be used for a wide variety of applications including processor performance evaluation and application program development at the initial stage, and to also be used as an engine for demonstration and simulation.

The GHS Multi or Midas PARTNER source-level debugger can be used as a development software tool with the RTE-V832-PC. The type of monitor to be stored in ROM depends on the debugger type.

In ROM, the monitor specified at the time of purchase is stored. Even when neither of the debuggers is purchased together with the RTE-V832-PC, they can be purchased at anytime subsequently.

## 1.1. NUMERIC NOTATION

This manual represents numbers according to the notation described in the following table. Hexadecimal and binary numbers are hyphenated at every four digits, if they are difficult to read because of many digits being in each number.

| Number                 | Notation rule                       | Example                                |

|------------------------|-------------------------------------|----------------------------------------|

| Decimal number         | Only numerals are indicated.        | "10" represents number 10 in decimal.  |

| Hexa-decimal<br>number | A number is suffixed with letter H. | "10H" represents number 16 in decimal. |

| Binary number          | A number is suffixed with letter B. | "10B" represents number 2 in decimal.  |

Number Notation Rules

MULTI is a trademark of Green Hills Software, Inc. in the US.

## 2. FUNCTIONS

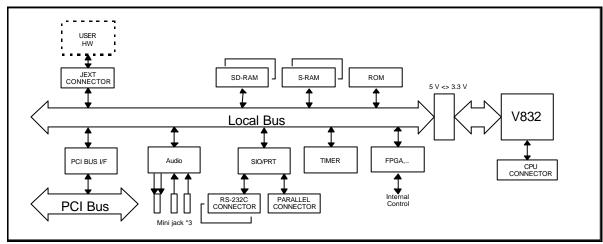

The overview of each function block of the RTE-V832-PC is shown below.

RTE-V832-PC Block Diagram

#### 3. MAJOR FEATURES

- Two types of monitor ROM are provided: one is used for the Green Hills Multi and the other for the Midas PARTNER.

- Real-time execution and evaluation at a high-level language level using Multi or PARTNER.

- A ROM emulator can be connected.

- 512K bytes of high-speed SRAM and 32M bytes of SDRAM are provided as standard.

- SRAM and DRAM can be evaluated in 16-bit bus mode.

- Two serial interfaces and one printer interface are provided.

- Two timer channels are provided. (One channel is used for the monitor.)

- Two audio input channels and two audio output channels are provided.

#### 4. BASIC SPECIFICATIONS

| Descar                    | 1/000                                                                  |  |  |  |

|---------------------------|------------------------------------------------------------------------|--|--|--|

| Processor                 | V832                                                                   |  |  |  |

| CPU clock                 | 142.8 MHz                                                              |  |  |  |

| Bus clock                 | 47.6 MHz                                                               |  |  |  |

| Power consumption         | +5 V (2 A)                                                             |  |  |  |

| Memory                    |                                                                        |  |  |  |

| EPROM                     | 128 KB 64 K $\times$ 16 bits (40-pin DIP) $\times$ 1 (512K bytes max.) |  |  |  |

| SRAM                      | 512 KB 128 K × 8 bits × 4                                              |  |  |  |

| DRAM                      | 32 MB 64 M-SDRAM × 4                                                   |  |  |  |

| I/O                       |                                                                        |  |  |  |

| Serial (2 ch)             | Equivalent to NS16550, 10-pin header, DB9 connector                    |  |  |  |

| Printer                   | IEEE1284-compatible, 26-pin header                                     |  |  |  |

| Audio input/output (2 ch) | <i>m</i> PD63310, Mini-jack (MIC×2, LINEOUT×1)                         |  |  |  |

| Timer                     | Equivalent to i8254, 500-ns resolution                                 |  |  |  |

| I/O port                  | LED (7-segment) display/switch input                                   |  |  |  |

| Others                    |                                                                        |  |  |  |

| CPU connector             | Connector with all function pins of the V832 connected                 |  |  |  |

| 32-bit standard external  | RTE-PC standard 32-bit interface                                       |  |  |  |

| extension bus             | (16M bytes, 32-bit bus, correspond to DMA)                             |  |  |  |

| Reset switch              | Push type                                                              |  |  |  |

|                           |                                                                        |  |  |  |

## 5. BOARD CONFIGURATION

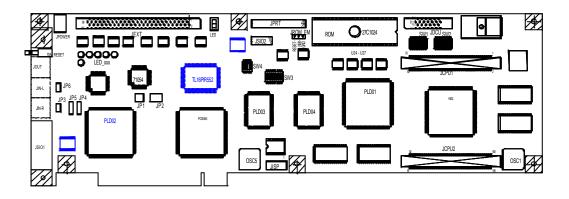

The physical layout of the major components on the RTE-V832-PC board is shown below. This chapter explains each component.

#### 5.1. RESET SWITCH (RESET)

RESET is a reset switch for the entire board. Pressing this switch causes all the circuits including the CPU to be reset.

#### 5.2. POWER JACK (JPOWER)

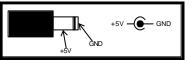

When this board is to be used as a standalone, that is, without being inserted in a PCI bus slot, the board should be supplied with power from an external power supply by connecting it to the JPOWER connector.

The external power should be one rated as listed below.

5 V

Voltage:

Current:Maximum of 2.0 A (excluding the current supplied to the JEXT connector)Mating connector:Type A (5.5 mm in diameter)

Polarity:

**[Caution]** When attaching an external power supply to the board, be <u>careful about its connector</u> <u>polarity</u>. When inserting the board into the PCI bus slot, do not attach the JPOWER connector to an external power supply. It may result in a malfunction.

## 5.3. SWITCH 1 (SW1)

SW1 is a general-purpose input port switch. When the monitor is used, all SW1 switches except some are already set. When the port is read, a switch being set to OFF represents 1, while its being set to ON represents 0. Set this switch for assignment with the monitor by referring to the following sections and in accordance with your environment:

When using Multi, see Section 13.1.2.

When using PARTNER, see Section 14.1.1.

## 5.4. SWITCH 2 (SW2)

SW2 sets the H/W status of this board. All the bits of this switch can be read by software. When this switch is read from a port, OFF indicates 1 and ON indicates 0. For details, see Section 8.2.

| No. | Function name | Description                                                                                                                                                                                                                      |  |  |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | BSIZE16       | Specifies bus size of SRAM and SDRAM.<br>OFF: 32 bits (factory setting)<br>ON: 16 bits                                                                                                                                           |  |  |

| 2   | BCLK_HI       | Specifies frequency of bus clock.<br>OFF: Frequency exceeding 33 MHz (factory setting)<br>ON: Frequency less than 33 MHz                                                                                                         |  |  |

| 3   | CMODE         | Directly connected to CMODE pin of CPU.<br>OFF: Multiplied by 8<br>ON: Multiplied by 6 (factory setting)                                                                                                                         |  |  |

| 4   | TEST          | Must always be OFF.                                                                                                                                                                                                              |  |  |

| 5   | ROM_TYPE0     | pecifies the type of ROM to be used.                                                                                                                                                                                             |  |  |

| 6   | ROM_TYPE1     | [ROM_TYPE1, ROM_TYPE0]         [OFF, OFF]       When monitor ROM is used (factory setting)         [OFF, ON]       When 27C4096 is used         [ON, OFF]       When 27C2048 is used         [ON, ON]       When 27C1024 is used |  |  |

| 7   | BNK_DIS       | Specifies whether the upper and lower halves (banks) of ROM are separated<br>OFF: Upper and lower halves of ROM are separated (factory setting).<br>ON: Upper and lower halves of ROM are used as a contiguous area.             |  |  |

| 8   | BNK_LOW       | Selects either the upper or lower half when BNK_DIS = OFF<br>OFF: Selects upper half.<br>ON: Selects lower half (factory setting).                                                                                               |  |  |

## 5.5. SWITCH 3 (SW3)

SW3 physically cuts the interrupts used in this board. All the bits of this switch are set to ON (connected status) at the factory. Set the corresponding bit of this switch only when it is used externally, and only when the internally used interrupt is unnecessary.

| No. | INT name | Internally used interrupt source                                |  |  |

|-----|----------|-----------------------------------------------------------------|--|--|

| 1   | INTP03   | PIC-INT0 (Do not set this bit to OFF when the monitor is used.) |  |  |

| 2   | INTP02   | PIC-INT1                                                        |  |  |

| 3   | INTP01   | EXTbus-INT0                                                     |  |  |

| 4   | INTP00   | Audio                                                           |  |  |

| 5   | INTP13   | EXTbus-INT3                                                     |  |  |

| 6   | INTP12   | EXTbus-INT2                                                     |  |  |

| 7   | INTP11   | EXTbus-INT1                                                     |  |  |

| 8   | INTP10   | Printer                                                         |  |  |

## 5.6. SWITCH 4 (SW4)

SW4 physically cuts the DMA used by this board. All the bits of this switch are set to ON (connected status) at the factory. Set the corresponding bit of this switch only when it is used externally, and only when the internally used DMA is unnecessary.

| No. | DMA name | Internally used interrupt source |  |  |

|-----|----------|----------------------------------|--|--|

| 1   | DMARQ2-  | EXTbus-DREQ0-                    |  |  |

| 2   | DMAAK2-  | EXTbus-DACK0-                    |  |  |

| 3   | DMARQ3-  | EXTbus-DREQ1-                    |  |  |

| 4   | DMAAK3-  | EXTbus-DACK1-                    |  |  |

**[Caution]** Set switch bits 1 and 2, and 3 and 4 to the same positions.

## 5.7. LED

The LEDs are used to indicate statuses, as listed below.

| LED       | Description                                                                                        |  |  |

|-----------|----------------------------------------------------------------------------------------------------|--|--|

| POWER     | Lights when power is supplied to the RTE-V832-PC board.                                            |  |  |

| PLY       | hts in green when voice is output.<br>hts in red if an error occurs during voice output.           |  |  |

| REC       | ights in green when voice is recorded.<br>.ights in red if an error occurs during voice recording. |  |  |

| PCI_PERR  | Lights if a parity error occurs in the PCI bus.                                                    |  |  |

| PCI9_DEAD | Lights if the PCI controller is deadlocked.                                                        |  |  |

| TOVER     | Lights when a time-out occurs.                                                                     |  |  |

LED Indication

[Caution] If PCI\_PERR and PCI9\_DEAD light, restart the system.

#### 5.8. TEST PINS FOR ROM EMULATOR (JROM\_EM)

Test pins (JROM\_EMs) are used to connect a ROM emulator. They accept control signals from the ROM emulator. The following table lists the signal names and functions related to each test pin.

| Signal | Input/<br>output | Function                                                                                   |  |  |

|--------|------------------|--------------------------------------------------------------------------------------------|--|--|

| RESET- | Input            | When a low level is supplied to this test pin, the CPU is reset.                           |  |  |

| (1)    |                  | A reset request signal from the ROM emulator is connected to the test pin.                 |  |  |

|        |                  | The test pin is pulled up with 1 k $\Omega$ .                                              |  |  |

| NMI-   | Input            | When a low level is supplied to this test pin, an NMI signal is given to the CPU. This     |  |  |

| (2)    |                  | signal can be masked by software, so it is necessary to reset the mask. (See Section 8.9.) |  |  |

|        |                  | NMI request signal from the ROM emulator is connected to the test pin.                     |  |  |

|        |                  | The test pin is pulled up with 1 k $\Omega$ .                                              |  |  |

| GND    |                  | This test pin is at a ground level. The ground level of the ROM emulator is connected      |  |  |

| (3)    |                  | to the test pin.                                                                           |  |  |

JROM\_EM Pin Functions

## 5.9. CLOCK SOCKET (OSC1)

An oscillator for generating the clock signal to be supplied to the CPU is mounted in the OSC1 socket. With the V832, a PLL is used to generate a system clock. The frequency of the oscillator must be onesixth or one-eighth the internal operating frequency of the V832. Accepts DIP 8-pin (half-type) oscillators.

**[Caution]** When you have to cut an oscillator pin for convenience, be careful not to cut it too short, or otherwise the frame (housing) of the oscillator may touch a tine in the socket, resulting in a short-circuit occurring.

## 5.10. ROM SOCKETS

The RTE-V832-PC has ROM sockets to hold 40-pin ROM chips to provide standard 128K bytes ( $64K \times 16$  bits). When the ROM chips used here are to be replaced, their type should be 27C1024, 27C2048, or 27C4096, and the access time should be 120 ns or less. SW2 may need to be set according to the type and purpose of the ROM chips to be used. For details, see Section 5.4.

## 5.11. DMARQ0-, DMARQ1- SEPARATION JUMPER (JP1)

JP1 is a jumper that physically cuts off DMARQ0- and DMARQ1-, used for Audio data transfer, from the V832. Usually, jumper 1-2, and 3-4.

[Remark] If this jumper is opened, Audio data cannot be transferred by means of DMA.

## 5.12. TIMER CLOCK FREQUENCY SELECT JUMPER (JP2)

JP2 is used to select which of two clocks is to be supplied to the timers (CH#1, CH#2) that can be used by applications.

- 1-2: 2 MHz (factory-set)

- 3-4: 4 MHz

- 5-6: 8 MHz

#### 5.13. AUDIO INPUT LEVEL SELECT JUMPERS (JP3, JP4, JP5, JP6)

These jumpers are used to select the input level of Audio. Set these jumpers as shown below, depending on whether MIC or LINE is used. MIC is the factory setting.

| Input level | JP3   | JP4       | JP5       | JP6   |

|-------------|-------|-----------|-----------|-------|

| MIC         | Short | 1-2 short | 1-2 short | Short |

| LINE        | Open  | 2-3 short | 2-3 short | Open  |

## 5.14. SERIAL CONNECTOR (JSIO1, JSIO2)

The JSIO1 and JSIO2 connectors are used for the RS-232C interface that is controlled by the serial controller (TL16PIR552PH). JSIO1 is a 9-pin D-SUB RS-232C connector like that commonly used on the PC/AT, while JSIO2 is a pin plug type connector with a pitch of 2.54 mm. All signals on both of these connectors are converted to the RS-232C level. The figures and table below indicate the pin and signal arrangements of these connectors.

For the signals to be connected to the host, the table indicates two modes of wiring on the host: one for a 9-pin D-SUB connector, and the other for a 25-pin D-SUB connector. (Regular cross-cable wiring is used for these connections.)

The pin arrangement of JSIO2 will be identical to that of JSIO1 when a push-fit connector is used with a ribbon cable.

JSIO1 Pin Arrangement (Male)

| JSIO2 Pin Arrangement |

|-----------------------|

|                       |

| JSIO1   | JSIO2   | Signal name  | Input/ | Connector pin num | per on the host side |

|---------|---------|--------------|--------|-------------------|----------------------|

| pin No. | pin No. | Olghai haine | output | D-SUB9            | D-SUB25              |

| 1       | 1       | DCD          | Input  |                   |                      |

| 2       | 3       | RxD(RD)      | Input  | 3                 | 2                    |

| 3       | 5       | TxD(SD)      | Output | 2                 | 3                    |

| 4       | 7       | DTR(DR)      | Output | 1, 6              | 6, 8                 |

| 5       | 9       | GND          |        | 5                 | 7                    |

| 6       | 2       | DSR(ER)      | Input  | 4                 | 20                   |

| 7       | 4       | RTS(RS)      | Output | 8                 | 5                    |

| 8       | 6       | CTS(CS)      | Input  | 7                 | 4                    |

| 9       | 8       | RI           | Input  |                   |                      |

|         | 10      | NC           |        |                   |                      |

JSIO1 and JSIO2 Connector Signals

## 5.15. PARALLEL CONNECTOR (JPRT)

The JPRT connector is used for parallel communication controlled by the parallel (printer) controller (TL16PIR552PH). JPRT is a pin plug type connector with a 2.54 mm pitch. All signals on the connector are 5-V level signals. The figure and table below indicate the pin and signal arrangements of the connector.

The pin arrangement of JPRT will be identical to that of the 25-pin D-SUB connector, like that commonly used on the PC/AT, when a push-fit connector is used with a ribbon cable.

## 24 14 6 18 10 12 14 16 16 20 22 23 26 11 13 5 17 19 11 15 15 17 19 20 23 25

| JPRT pin No. | Signal name | JPRT pin No. | Signal name |

|--------------|-------------|--------------|-------------|

| 1            | STB-        | 2            | AUTO_FD-    |

| 3            | D0          | 4            | ERROR-      |

| 5            | D1          | 6            | INIT-       |

| 7            | D2          | 8            | SELECT_IN-  |

| 9            | D3          | 10           | GND         |

| 11           | D4          | 12           | GND         |

| 13           | D5          | 14           | GND         |

| 15           | D6          | 16           | GND         |

| 17           | D7          | 18           | GND         |

| 19           | ACK-        | 20           | GND         |

| 21           | BUSY        | 22           | GND         |

| 23           | PE          | 24           | GND         |

| 25           | SELECT      | 26           | NC          |

JPRT Pin Arrangement

JPRT Connector Signals

#### 5.16. AUDIO MINI-JACKS (JIN-R, JIN-L, JLINEOUT)

Audio jacks are provided for two monaural microphone or line input channels and one stereo output channel. The input/output conditions of these jacks are indicated below.

#### JIN-R, JIN-L

Electrical input condition

When MIC input is specified: 140 mVp-p (Internal amplification: About 20 dB) When LINE input is specified: 1.4 Vp-p

Physical shape of mating plug

Monaural mini-plug (f3.5)  $\times$  2 channels

#### JLINEOUT

Electrical output condition 1.4 Vp-p Physical shape of mating plug Stereo mini-plug (£3.5) ×1 channel

[Supplement] Selection between MIC and LINE is performed by setting JP3, JP4, JP5, and JP6.

## 5.17. DEBUGGING CONNECTOR (JDCU)

The JDCU connector is used to connect a debug tool based on the debug function built into the V832.

On-board connector: 8830E-026-170S manufactured by KEL

| Pin No. | Signal name | Pin No. | Signal name |

|---------|-------------|---------|-------------|

| A1      | TRCCLK      | B1      | GND         |

| A2      | TRCDATA0    | B2      | GND         |

| A3      | TRCDATA1    | B3      | GND         |

| A4      | TRCDATA2    | B4      | GND         |

| A5      | TRCDATA3    | B5      | GND         |

| A6      | NC.         | B6      | GND         |

| A7      | DDI         | B7      | GND         |

| A8      | DCK         | B8      | GND         |

| A9      | DMS         | B9      | GND         |

| A10     | DDO         | B10     | GND         |

| A11     | DRST-       | B11     | NC.         |

| A12     | NC.         | B12     | NC.         |

| A13     | NC.         | B13     | +3.3 V      |

JDCU Connector Signals

## 5.18. CPU CONNECTOR (JCPU-1, JCPU-2)

The CPU connector signals are connected directly to the V832. Many signals are used on the board. So, be careful when extracting signals from the JCPU. The 3.3-V signal level is used.

| Pin No. | Signal name             | Pin No. | Signal name |

|---------|-------------------------|---------|-------------|

| 1       | GND                     | 2       | CS1-        |

| 3       | CS0-                    | 4       | WE-         |

| 5       | RAS-                    | 6       | UUDQM       |

| 7       | ULDQM                   | 8       | LUDQM       |

| 9       | LLDQM                   | 10      | +3.3 V      |

| 11      | GND                     | 12      | SDCLKOUT    |

| 13      | CKE                     | 14      | CAS-        |

| 15      | A1                      | 16      | A2          |

| 17      | A3                      | 18      | A4          |

| 19      | +2.5 V                  | 20      | GND         |

| 21      | +3.3 V                  | 22      | GND         |

| 23      | A5                      | 24      | A6          |

| 25      | Α7                      | 26      | A8          |

| 27      | A9                      | 28      | A10         |

| 29      | A11                     | 30      | +3.3 V      |

| 31      | GND                     | 32      | A12         |

| 33      | A13                     | 34      | A14         |

| 35      | A15                     | 36      | A16         |

| 37      | A17                     | 38      | A18         |

| 39      | A19                     | 40      | +5 V        |

| 41      | GND                     | 42      | A20         |

| 43      | A21                     | 44      | A22         |

| 45      | A23                     | 46      | CLKOUT      |

| 47      | BCLK2 (buffered CLKOUT) | 48      | MWR0-       |

| 49      | MWR1-                   | 50      | MWR2-       |

| 51      | MWR3-                   | 52      | NC.         |

| 53      | NC.                     | 54      | NC.         |

| 55      | NC.                     | 56      | NC.         |

| 57      | NC.                     | 58      | GND         |

| 59      | +2.5 V                  | 60      | GND         |

| 61      | NC.                     | 62      | BT16B (GND) |

| 63      | RESET-                  | 64      | NMI-        |

| 65      | NC.                     | 66      | CMODE       |

| 67      | P3                      | 68      | P4          |

| 69      | P2                      | 70      | P1          |

| 71      | P0                      | 72      | +5 V        |

| 73      | GND                     | 74      | INTP0       |

| 75      | INTP12                  | 76      | INTP11      |

| 77      | INTP13                  | 78      | PB0         |

| 79      | PB1                     | 80      | +2.5 V      |

JCPU-1 Connector Signals

| 81         GND         82         INTPO           83         INTPO1         84         INTPO2           85         INTPO3         86         DMARQ3-           87         DMARQ0-         90         DMAAK3-           91         DMAAK0-         94         TC-STOPAK-           93         DMAAK0-         94         TC-STOPAK-           95         CS7-         96         CS6-           97         CS5-         98         CS4-           99         CS3-         100         CS2-           101         +3.3 V         102         GND           103         HLDAK-         104         HLDRQ-           105         R/W-         106         READY-           107         BCYST-         108         IORD-           109         IOWR         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         116         +3.3 V           115         MRD-         116         +3.3 V           117         GND         118         D0           118         D0         122         D2           <                                                  | Pin No. | Signal name | Pin No. | Signal name |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|---------|-------------|

| 86         INTP03         86         DMARQ3-           87         DMARQ2-         88         DMARQ1-           89         DMARQ0-         90         DMAAK3-           91         DMAAK0-         94         TC-/STOPAK-           93         DMAAK0-         94         TC-/STOPAK-           95         CS7-         96         CS6-           97         CS5-         98         CS4-           99         CS3-         100         CS2-           101         +3.3 V         102         GND           103         HLDAK-         104         HLDRQ-           105         RW-         106         READY-           107         BCYST-         108         IORD-           109         IOWR         110         UUBEN-           111         ULBEN-         114         MWR-           113         LLBEN-         116         +3.3 V           119         D1         120         +2.5 V           121         GND         112         D2           123         D3         124         D4           125         D5         126         D6                                                                 | 81      | GND         | 82      | INTP00      |

| 87         DMARQ2-         88         DMARQ1-           89         DMARQ0-         90         DMAAK3-           91         DMAAK2-         92         DMAAK1-           93         DMAAK0-         94         TC-/STOPAK-           95         CS7-         96         CS6-           97         CS5-         98         CS4-           99         CS3-         100         CS2-           101         +3.3 V         102         GND           103         HLDAK-         104         HLDRQ-           105         RW-         106         READY-           107         BCYST-         108         IORD-           109         IOWR         110         UUBEN-           111         ULBEN-         114         MWR-           113         LLBEN-         114         MWR-           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           133         D3         124         D4           125 <td>83</td> <td>INTP01</td> <td>84</td> <td>INTP02</td> | 83      | INTP01      | 84      | INTP02      |

| 89         DMARQO-         90         DMAAK3-           91         DMAAK2-         92         DMAAK1-           93         DMAAK0-         94         TC-/STOPAK-           95         CS7-         96         CS6-           97         CS5-         98         CS4-           99         CS3-         100         CS2-           101         +3.3 V         102         GND           103         HLDAK-         104         HLDRQ-           105         RW-         106         READY-           107         BCYST-         108         IORD-           109         IOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127                                                               | 85      | INTP03      | 86      | DMARQ3-     |

| 91         DMAAK2-         92         DMAAK1-           93         DMAAK0-         94         TC-/STOPAK-           95         CS7-         96         CS6-           97         CS5-         98         CS4-           99         CS3-         100         CS2-           101         +3.3 V         102         GND           103         HLDAK-         104         HLDRQ-           105         RW-         106         READY-           107         BCYST-         108         IORD-           109         IOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         112         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         <                                                           | 87      | DMARQ2-     | 88      | DMARQ1-     |

| 93         DMAAKO-         94         TC-/STOPAK-           95         CS7-         96         CS6-           97         CS5-         98         CS4-           99         CS3-         100         CS2-           101         +3.3 V         102         GND           103         HLDAK-         104         HLDRQ-           105         RW-         106         READY-           107         BCYST-         108         IORD-           109         JOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9 </td <td>89</td> <td>DMARQ0-</td> <td>90</td> <td>DMAAK3-</td>  | 89      | DMARQ0-     | 90      | DMAAK3-     |

| 95CS7-96CS6-97CS5-98CS4-99CS3-100CS2-101 $+3.3 V$ 102GND103HLDAK-104HLDRQ-105RW-106READY-107BCYST-108IORD-109IOWR-110UUBEN-111ULBEN-112LUBEN-113LLBEN-114MWR-115MRD116 $+3.3 V$ 117GND118D0119D1120 $+2.5 V$ 121GND122D2123D3124D4125D5126D6127D7128 $+5 V$ 129GND130D8131D9132D10133D11134D12134D15138 $+5 V$ 139GND140D16141D17142D18143D19144D20145D21146D22147D23148 $+5 V$ 151GND152D24153D25154D26155D27156D28157D29158D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91      | DMAAK2-     | 92      | DMAAK1-     |

| 97CS5-98CS4-99CS3-100CS2-101 $+3.3$ V102GND103HLDAK-104HLDRQ-105RW-106READY-107BCYST-108IORD-109IOWR-110UUBEN-111ULBEN-112LUBEN-113LLBEN-114MWR-115MRD-116 $+3.3$ V117GND118D0119D1120 $+2.5$ V121GND122D2123D3124D4125D5126D6127D7128 $+5$ V129GND130D8131D9132D10133D11134D12134D15138 $+5$ V139GND140D16141D17142D18143D19144D20145D21146D22147D23148 $+5$ V151GND150 $+2.5$ V1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93      | DMAAK0-     | 94      | TC-/STOPAK- |

| 99CS3-100CS2-101 $+3.3$ V102GND103HLDAK-104HLDRQ-105RW-106READY-107BCYST-108IORD-109IOWR110UUBEN-111ULBEN-112LUBEN-113LLBEN-116 $+3.3$ V117GND118D0119D1120 $+2.5$ V121GND122D2123D3124D4125D5126D6127D7128 $+5$ V129GND130D8131D9132D10133D11134D12134D17142D18143D19144D20144D17142D18143D21146D22145D21146D22147D23148 $+5$ V149GND150 $+2.5$ V151GND150 $+2.5$ V151GND150 $+2.5$ V151GND150 $+2.5$ V151GND152D24155D27156D28157D29158D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95      | CS7-        | 96      | CS6-        |

| 101         +3.3 V         102         GND           103         HLDAK-         104         HLDRQ-           105         RW-         106         READY-           107         BCYST-         108         IORD-           109         IOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         112         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16      141         D17         142<                                                                    | 97      | CS5-        | 98      | CS4-        |

| 103         HLDAK-         104         HLDRQ-           105         RW-         106         READY-           107         BCYST-         108         IORD-           109         IOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR-           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16      141         D17         142 </td <td>99</td> <td>CS3-</td> <td>100</td> <td>CS2-</td>            | 99      | CS3-        | 100     | CS2-        |

| 105         RW-         106         READY-           107         BCYST-         108         IORD-           109         IOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR-           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         14                                                                        | 101     | +3.3 V      | 102     | GND         |

| 107         BCYST-         108         IORD-           109         IOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR-           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146 </td <td>103</td> <td>HLDAK-</td> <td>104</td> <td>HLDRQ-</td>           | 103     | HLDAK-      | 104     | HLDRQ-      |

| 109         IOWR-         110         UUBEN-           111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR-           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148                                                                               | 105     | R/W-        | 106     | READY -     |

| 111         ULBEN-         112         LUBEN-           113         LLBEN-         114         MWR-           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150                                                                                   | 107     | BCYST-      | 108     | IORD-       |

| 113         LLBEN-         114         MWR-           115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           134         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +                                                                                 | 109     | IOWR-       | 110     | UUBEN-      |

| 115         MRD-         116         +3.3 V           117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           134         D12         135         D13         136           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25                                                                                          | 111     | ULBEN-      | 112     | LUBEN-      |

| 117         GND         118         D0           119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           134         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           144         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24 </td <td>113</td> <td>LLBEN-</td> <td>114</td> <td>MWR-</td>                      | 113     | LLBEN-      | 114     | MWR-        |

| 119         D1         120         +2.5 V           121         GND         122         D2           123         D3         124         D4           125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                 | 115     | MRD-        | 116     | +3.3 V      |

| 121       GND       122       D2         123       D3       124       D4         125       D5       126       D6         127       D7       128       +5 V         129       GND       130       D8         131       D9       132       D10         133       D11       134       D12         135       D13       136       D14         137       D15       138       +5 V         139       GND       140       D16         141       D17       142       D18         143       D19       144       D20         145       D21       146       D22         147       D23       148       +5 V         149       GND       150       +2.5 V         151       GND       152       D24         153       D25       154       D26         155       D27       156       D28         157       D29       158       D30                                                                                                                                                                                                                                                                                           | 117     | GND         | 118     | D0          |

| 123       D3       124       D4         125       D5       126       D6         127       D7       128       +5 V         129       GND       130       D8         131       D9       132       D10         133       D11       134       D12         135       D13       136       D14         137       D15       138       +5 V         139       GND       140       D16         141       D17       142       D18         143       D19       144       D20         145       D21       146       D22         147       D23       148       +5 V         149       GND       150       +2.5 V         151       GND       152       D24         153       D25       154       D26         155       D27       156       D28         157       D29       158       D30                                                                                                                                                                                                                                                                                                                                    | 119     | D1          | 120     | +2.5 V      |

| 125         D5         126         D6           127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                      | 121     | GND         | 122     | D2          |

| 127         D7         128         +5 V           129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           151         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                      | 123     | D3          | 124     | D4          |

| 129         GND         130         D8           131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           151         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                        | 125     | D5          | 126     | D6          |

| 131         D9         132         D10           133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                         | 127     | D7          | 128     | +5 V        |

| 133         D11         134         D12           135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                                                                          | 129     | GND         | 130     | D8          |

| 135         D13         136         D14           137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           150         +2.5 V         151         GND         152         D24           153         D25         154         D26         155         D27         156         D28           157         D29         158         D30         D30         D30         D30         D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 131     | D9          | 132     | D10         |

| 137         D15         138         +5 V           139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 133     | D11         | 134     | D12         |

| 139         GND         140         D16           141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 135     | D13         | 136     | D14         |

| 141         D17         142         D18           143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 137     | D15         | 138     | +5 V        |

| 143         D19         144         D20           145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 139     | GND         | 140     | D16         |

| 145         D21         146         D22           147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 141     | D17         | 142     | D18         |

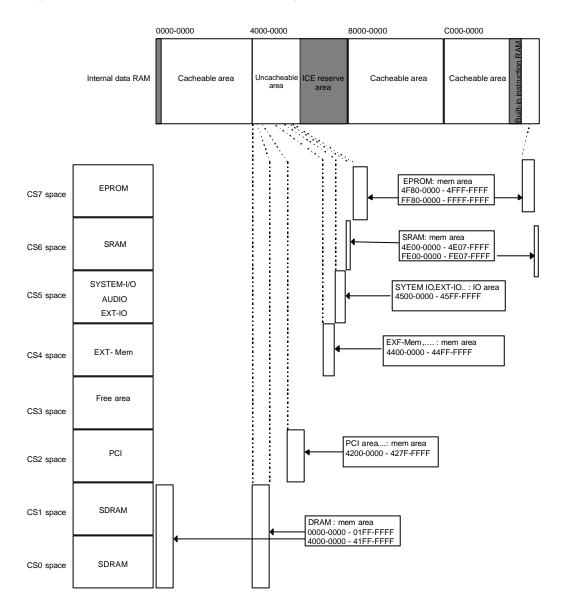

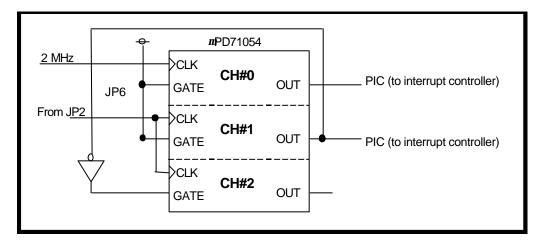

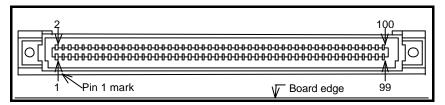

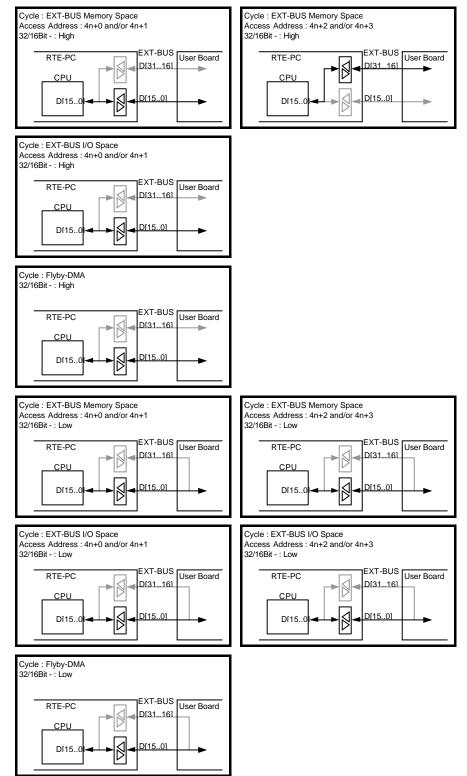

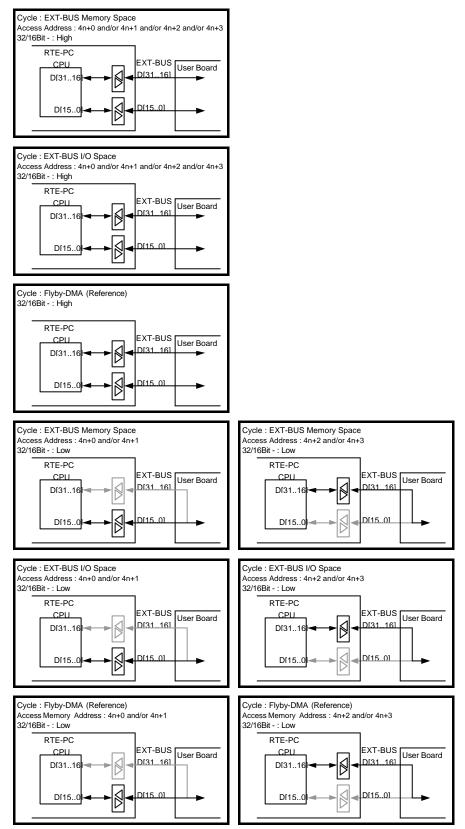

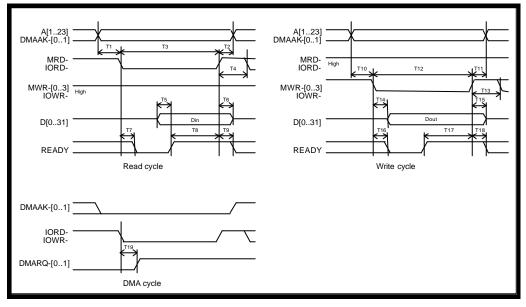

| 147         D23         148         +5 V           149         GND         150         +2.5 V           151         GND         152         D24           153         D25         154         D26           155         D27         156         D28           157         D29         158         D30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 143     | D19         | 144     | D20         |