# RTE-V850E/MS1-PC

User's Manual (Rev. 1.01)

Midas lab

| Date of enforcement     | Revision | Chapter | Description                                                            |  |

|-------------------------|----------|---------|------------------------------------------------------------------------|--|

| September 12, 1997 0.00 |          |         | Preliminary edition                                                    |  |

| October 15, 1997        | 0.80     |         | First edition                                                          |  |

| November 5, 1997 0.81   |          | 1.5.4   | <ul> <li>Added the description about SIMM.</li> </ul>                  |  |

| January 10, 1997        | 1.00     | 4.5.6   | <ul> <li>33MHz-&gt;40MHz.Added the detection of SIMM.</li> </ul>       |  |

|                         |          | 7       | <ul> <li>Added the recommended settings at 40MHz.Changed</li> </ul>    |  |

|                         |          |         | the setting data.                                                      |  |

| January 16, 1997        | 1.01     | 8.2     | <ul> <li>Changed the explanation of 32/16BIT- in the table.</li> </ul> |  |

|                         |          |         | <ul> <li>Changed the description of caution 1.</li> </ul>              |  |

|                         |          |         | <ul> <li>Added the caution 4.</li> </ul>                               |  |

|                         |          | 8.3     | <ul> <li>Added the section.</li> </ul>                                 |  |

## **REVISION HISTORY**

## **CONTENTS**

| 1. | INTR | ODUCTI  | ON                                         | 6    |

|----|------|---------|--------------------------------------------|------|

|    | 1.1. | NUME    | RIC NOTATION                               | 6    |

| 2. | FEAT |         | ND FUNCTIONS                               | 7    |

| 3. | BOA  | RD CON  | FIGURATION                                 | 8    |

|    | 3.1. | DIP SW  | /ITCHES                                    | 8    |

|    |      | 3.1.1.  | DIP Switch 1 (SW1)                         | 8    |

|    |      | 3.1.2.  | DIP Switch 2 (SW2)                         | 9    |

|    |      | 3.1.3.  | DIP Switch 3 (SW3)                         | 9    |

|    |      | 3.1.4.  | DIP Switch 4 (SW4)                         | .10  |

|    |      | 3.1.5.  | DIP Switch 5 (SW5)                         | .10  |

|    |      | 3.1.6.  | DIP Switch 6 (SW6)                         | .11  |

|    |      | 3.1.7.  | DIP Switch 7 (SW7)                         | .11  |

|    | 3.2. | JUMPE   | R SWITCHES                                 | .11  |

|    |      | 3.2.1.  | JP2                                        | .11  |

|    |      | 3.2.2.  | AVDD Power Switching Jumper Switch (JP3)   | .11  |

|    |      | 3.2.3.  | ROM Size Switching Jumper Switch (JP5)     | . 12 |

|    |      | 3.2.4.  | TIC Clock Switching Jumper Switch (JP6)    | . 12 |

|    | 3.3. | SWITC   | Н                                          | .12  |

|    |      | 3.3.1.  | Reset Switch (SW_RESET)                    | . 12 |

|    | 3.4. | LEDs    |                                            | .12  |

|    | 3.5. | CONNE   | ECTORS AND SOCKETS                         | .13  |

|    |      | 3.5.1.  | Power Supply Connector (JPOWER)            | .13  |

|    |      | 3.5.2.  | Crystal Socket (JP4)                       | .13  |

|    |      | 3.5.3.  | Oscillator Socket (OSC1)                   | .13  |

|    |      | 3.5.4.  | DRAM-SIMM Sockets                          | .14  |

|    |      | 3.5.5.  | ROM Sockets                                | .14  |

|    |      | 3.5.6.  | Self-Writing Power Supply Connector (JVPP) | . 14 |

|    |      | 3.5.7.  | Connector for ROM Emulation (JROM_EM)      | . 14 |

|    |      | 3.5.8.  | Serial Connectors (JSIO1, JSIO2)           | .15  |

|    |      | 3.5.9.  | Parallel Connector (JPRT)                  | .16  |

|    |      | 3.5.10. | Serial Connector (JRS232C)                 | .17  |

|    |      | 3.5.11. | Flash Writing Connector (JFLASH)           | .18  |

|    |      | 3.5.12. | Processor Pin Connector (JCPU)             | . 19 |

|    | 3.6. | EXTEN   | SION BUS CONNECTOR (JEXT)                  | .20  |

| 4. | USIN | G THE E | BOARD WITH THE MULTI DEBUGGER              | 21   |

|    | 4.1. | SOFTV   | VARE                                       | .21  |

|    | 4.2. | METHO   | DDS OF USE                                 | .21  |

|    | 4.3. | SETTIN  | IG UP THE BOARD                            | .21  |

|    |      | 4.3.1.  | DIP Switch 1 (SW1)                         | .21  |

|    |      | 4.3.2.  | DIP Switch 2 (SW2)                         | .21  |

|    |        | 4.3.3.  | DIP Switch 3 (SW3)                                               | 21 |

|----|--------|---------|------------------------------------------------------------------|----|

|    |        | 4.3.4.  | DIP Switch 4 (SW4)                                               | 21 |

|    |        | 4.3.5.  | DIP Switch 5 (SW5)                                               | 22 |

|    |        | 4.3.6.  | DIP Switch 6 (SW6)                                               | 22 |

|    |        | 4.3.7.  | DIP Switch 7 (SW7)                                               | 22 |

|    |        | 4.3.8.  | JP2                                                              | 22 |

|    |        | 4.3.9.  | AVDD Power Switching Jumper Switch (JP3)                         | 22 |

|    |        | 4.3.10. | ROM Capacity Switching Jumper Switch (JP5)                       | 22 |

|    |        | 4.3.11. | TIC Clock Switching Jumper Switch (JP6)                          | 22 |

|    | 4.4.   | PROCE   | EDURES FOR USE                                                   | 23 |

|    |        | 4.4.1.  | Procedure Involving the Insertion of the Board into ISA Bus Slot | 23 |

|    |        | 4.4.2.  | Procedure for Using the Board as a Standalone                    | 23 |

|    | 4.5.   | ROM M   | IONITOR FOR THE MULTI DEBUGGER                                   | 24 |

|    |        | 4.5.1.  | 7-Segment LED at Startup                                         | 24 |

|    |        | 4.5.2.  | ROM Monitor Work RAM                                             | 24 |

|    |        | 4.5.3.  | _INIT_SP Setting                                                 | 24 |

|    |        | 4.5.4.  | Remote Connection                                                | 24 |

|    |        | 4.5.5.  | Timer Interrupt                                                  | 24 |

|    |        | 4.5.6.  | Hardware Initialization                                          | 25 |

|    | 4.6.   | APPLIC  | CATIONS USING MASKABLE INTERRUPTS                                | 25 |

|    |        | 4.6.1.  | Interrupt Vectors                                                | 25 |

|    |        | 4.6.2.  | General Restrictions and Cautions                                | 27 |

|    |        | 4.6.3.  | Restrictions and Cautions on Using Breakpoints                   | 28 |

|    | 4.7.   | RTE CO  | OMMANDS                                                          |    |

|    |        | 4.7.1.  | HELP (?)                                                         | 28 |

|    |        | 4.7.2.  | INIT                                                             | 29 |

|    |        | 4.7.3.  | VER                                                              | 29 |

|    |        | 4.7.4.  | SFR                                                              | 29 |

| 5. | HARD   | WARE    | REFERENCES                                                       | 30 |

|    | 5.1.   | MEMO    | RY MAP                                                           |    |

|    | 5.2.   | DETAIL  | S OF THE MEMORY MAP                                              | 31 |

| 6. | SYST   | EM-I/O  |                                                                  | 33 |

|    | 6.1.   | SYSTE   | M-I/O LIST                                                       | 33 |

|    | 6.2.   | UART/F  | PRINTER (TL16PIR552) (3D8-0000H TO 3D8-003EH)                    | 34 |

|    | TIC (m | PD71054 | l) (3F-F040H TO 3F-F048H)                                        | 35 |

|    | 6.3.   | 7-SEGN  | MENT LED DISPLAY DATA OUTPUT PORT (3D8-0050H [WRITE ONLY])       |    |

|    | 6.4.   | DIP SW  | /7 READ PORT (3D8-0050H [READ ONLY])                             |    |

|    | 6.5.   | STATU   | S READ PORT (3D8-0060H [READ ONLY])                              | 37 |

|    | 6.6.   | CONTR   | ROL PORT (3D8-0080H [READ/WRITE])                                |    |

|    | 6.7.   | NMI/IN  | TP130 SELECT PORT (3D8-0090H [READ/WRITE])                       |    |

|    | 6.8.   | NMI/IN  | TP130 STATUS PORT (3D8-00A0H [READ ONLY])                        |    |

|    | 6.9.   | BANK F  | PORT FOR EXT-BUS CPU-CORE (3D8-00B0H [READ/WRITE])               |    |

|    | 6.10.  | BANK F  | PORT FOR EXT-BUS DMA0 (3D8-00C0H [READ/WRITE])                   | 40 |

|     | 6.11.  | BANK PORT FOR EXT-BUS DMA1 (3D8-00D0H [READ/WRITE]) | .40 |

|-----|--------|-----------------------------------------------------|-----|

| 7.  | RECO   | MMENDED SETTINGS                                    | 41  |

|     | 7.1.   | CPU SETTING                                         | .41 |

|     | 7.2.   | CS0/CS7 SPACES (SRAM/ROM)                           | .41 |

|     | 7.3.   | CS2 SPACE (EDO-DRAM)                                | .41 |

|     | 7.4.   | CS3 SPACE (SIMM)                                    | .41 |

|     | 7.5.   | CS6 SPACE WAITS                                     | .42 |

|     | 7.6.   | CS6 SPACE COMMAND RECOVERY TIME                     | .42 |

| 8.  | EXT-E  | BUS SPECIFICATION                                   | 43  |

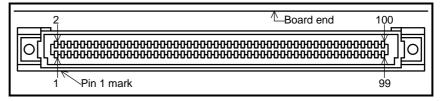

|     | 8.1.   | PIN ARRANGEMENT                                     | .43 |

|     | 8.2.   | SIGNALS                                             | .44 |

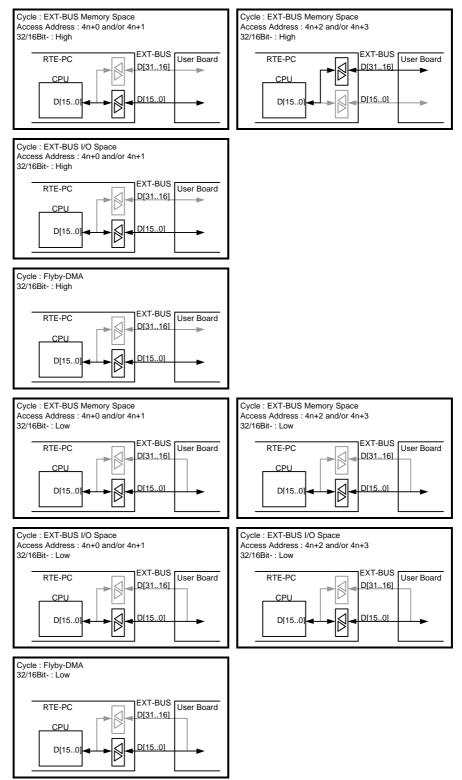

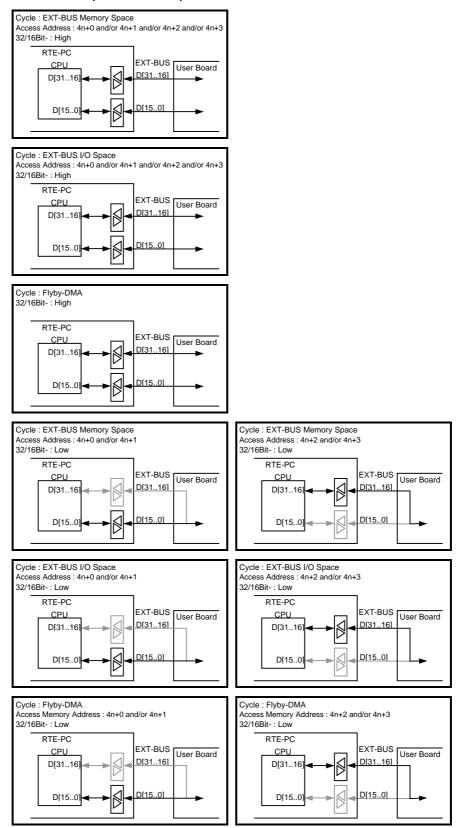

|     | 8.3.   | CONECTION OF DATA-BUS                               | .46 |

|     |        | 8.3.1. 16BIT DATA-BUS CPU (V850E/MS1)               | .46 |

|     |        | 8.3.2. 32BIT DATA-BUS CPU (for a reference)         | .47 |

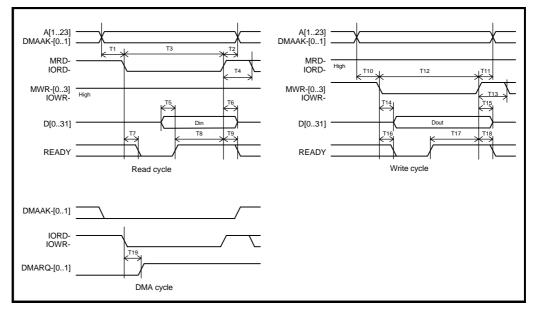

|     | 8.4.   | TIMING                                              | .48 |

|     | 8.5.   | CONNECTORS                                          | .49 |

|     | 8.6.   | CAUTIONS                                            | .49 |

| 9.  | DMA.   |                                                     | 50  |

|     | 9.1.   | SPACES BETWEEN WHICH DMA TRANSFER IS POSSIBLE       | .50 |

|     | 9.2.   | DMA CHANNELS                                        | .50 |

|     | 9.3.   | DIP SW SETTING                                      | .50 |

|     | 9.4.   | CPU SETTING                                         | .50 |

|     | 9.5.   | BANK PORT SETTING (2-CYCLE DMA)                     | .51 |

|     | 9.6.   | BANK PORT SETTING (FLY-BY DMA)                      | .51 |

|     | 9.7.   | WHEN USING MULTI                                    | .51 |

| 10. | CPU F  | PIN CONNECTION                                      | 52  |

|     | 10.1.  | LIST                                                | .52 |

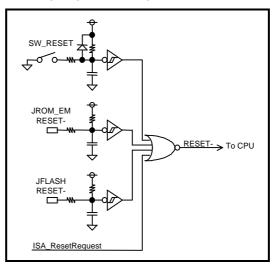

|     | 10.2.  | RESET                                               | .54 |

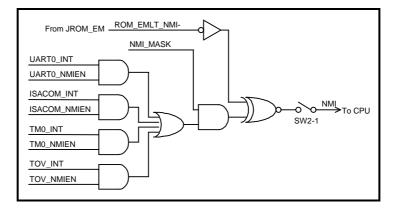

|     | 10.3.  | NMI                                                 | .55 |

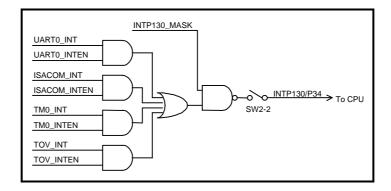

|     | 10.4.  | INTP130/P34                                         | .56 |

|     | 10.5.  | MODE0 TO MODE2 AND CKSEL                            | .56 |

|     | 10.6.  | MODE3/VPP AND P21                                   | .57 |

|     | 10.7.  | X1 AND X2                                           | .57 |

|     | 10.8.  | P22 TO P27                                          | .58 |

|     | 10.9.  | ANI0/P70 TO ANI7/P77, AVDD, AVSS, AND AVREF         | .58 |

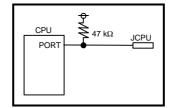

|     | 10.10. | PORT (TYPE 1)                                       | .59 |

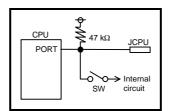

|     | 10.11. | PORT (TYPE 2)                                       | .59 |

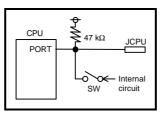

|     | 10.12. | PORT (TYPE 3)                                       | .60 |

| 11. | WRIT   | NG TO THE BUILT-IN FLASH ROM OF THE CPU             | 61  |

|     | 11.1.  | SWITCH SETTING                                      | .61 |

|     | 11.2.  | COMMUNICATION MODES                                 | .61 |

|     | 11.3.  | WRITING PROCEDURE                                   | .61 |

|     | 11.4.  | CAUTION                                             | .61 |

| 12. | BUS ( | US CYCLE |                    |    |  |  |  |  |  |

|-----|-------|----------|--------------------|----|--|--|--|--|--|

|     | 12.1. | TIME-O   | VER READY          | 62 |  |  |  |  |  |

|     | 12.2. | SIMM II  | NTERFACE           | 62 |  |  |  |  |  |

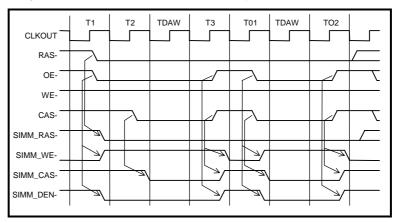

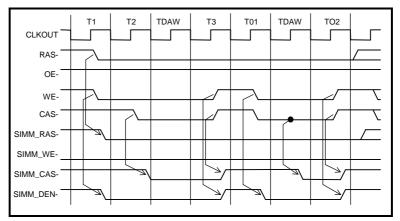

|     |       | 12.2.1.  | Outline            | 62 |  |  |  |  |  |

|     |       | 12.2.2.  | Signal Description | 62 |  |  |  |  |  |

|     |       | 12.2.3.  | Read Cycle         | 63 |  |  |  |  |  |

|     |       | 12.2.4.  | Write Cycle        | 63 |  |  |  |  |  |

#### 1. INTRODUCTION

This manual describes the **RTE-V850E/MS1-PC**, which is an evaluation board for the V850E/MS1, NEC's CPU. With the RTE-V850E/MS1-PC, it is possible to develop and debug programs, and evaluate the CPU performance, using the GreenHills Multi debugger. Communication with this debugger is carried out using the IBM-PC/AT ISA bus or RS-232C serial interface. It is also possible to expand memory and I/O units using local bus connectors provided on the evaluation board.

## 1.1. NUMERIC NOTATION

This manual represents numbers according to the notation described in the following table. Hexadecimal and binary numbers are hyphenated at every four digits, if they are difficult to read because of many digits being in each number.

| Number             | Notation rule                       | Example                                |

|--------------------|-------------------------------------|----------------------------------------|

| Decimal number     | Only numerals are indicated.        | "10" represents number 10 in decimal.  |

| Hexadecimal number | A number is suffixed with letter H. | "10H" represents number 16 in decimal. |

| Binary number      | A number is suffixed with letter B. | "10B" represents number 2 in decimal.  |

**Number Notation Rules**

## 2. FEATURES AND FUNCTIONS

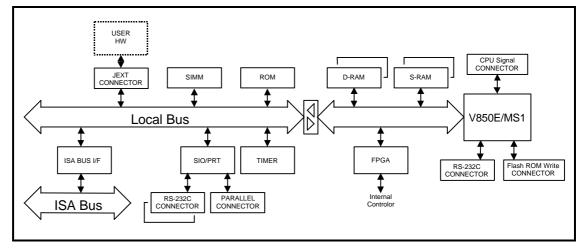

The overview of each function block of the RTE-V850E/MS1-PC is shown below.

RTE-V850E/MS1-PC Block Diagram

## Features

- ROM : Standard 128 Kbytes ( $64K \times 16$ -bit EPROM  $\times 1$ )

- Maximum 512 Kbytes (256K  $\times$  16-bit EPROM  $\times$  1)

- SRAM : 512 Kbytes (64K  $\times$  16-bit SRAM  $\times$  4)

- DRAM : 4 Mbytes ( $2M \times 8$ -bit EDO-RAM  $\times 2$ )

- SIMM : 4 or 8 Mbytes (SIMM is optional) installed in one 72-pin SIMM socket The EDO-type DRAM-SIMM can be used as well as the ordinary type DRAM-SIMM.

- RS-232C port (9-pin D-SUB connector × 1, 10-pin 2.54-mm pin header × 2)

- Parallel port (26-pin 2.54-mm pin header × 1)

- Communication function supported using the ISA bus of a PC/AT or compatible

- Local bus connector for user-installed expansion equipment

- Processor pin connector for measuring CPU signals

- External reset switch provided on the rear panel

- Connection pins for ROM in-circuit debugger

- Connector for writing to the built-in flash ROM of the CPU

- RS-232C connector using the built-in UART of the CPU

## 3. BOARD CONFIGURATION

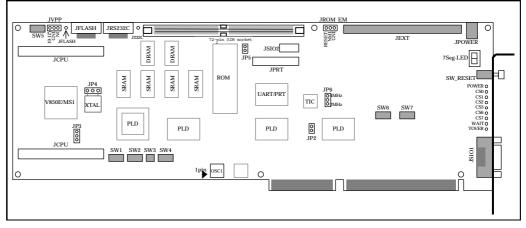

The physical layout of the major components on the RTE-V850E/MS1-PC board is shown below. This chapter explains each component.

RTE-V850E/MS1-PC Board Top View

#### 3.1. DIP SWITCHES

The RTE-V850E/MS1-PC features seven DIP switches, SW1 to SW7. The functions of these switches are explained below. The "Def." column in each of the following tables shows the factory-set positions.

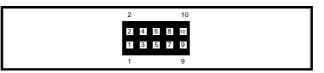

## 3.1.1. DIP Switch 1 (SW1)

DIP SW1 is used to set up DMA transfer over EXT-BUS.

| No. | Symbol               | Def. | Description                                                                              |

|-----|----------------------|------|------------------------------------------------------------------------------------------|

| 1   | EXDMA0 <sup>*1</sup> | OFF  | OFF : The INTP100/DMARQ0-/P04 and INTP110/DMAAK0-/P14 pins of the CPU can be             |

|     |                      |      | used for purposes other than DMA transfer over EXT-BUS.                                  |

| 2   | EXDMA0 <sup>*1</sup> | OFF  | ON : The INTP100/DMARQ0-/P04 and INTP110/DMAAK0-/P14 pins of the CPU are used for        |

|     |                      |      | DMA transfer over EXT-BUS.                                                               |

| 3   | EXDMA1 <sup>*2</sup> | OFF  | OFF : The INTP101/DMARQ1-/P05 and INTP111/DMAAK1-/P15 pins of the CPU can be             |

|     |                      |      | used for purposes other than DMA transfer over EXT-BUS.                                  |

| 4   | EXDMA1 <sup>*2</sup> | OFF  | ON : The INTP101/DMARQ1-/P05 and INTP111/DMAAK1-/P15 pins of the CPU are used for        |

|     |                      |      | DMA transfer over EXT-BUS.                                                               |

| 5   | PDMA                 | OFF  | Reserved by the system. Must be set to OFF.                                              |

| 6   | PDMA                 | OFF  |                                                                                          |

| 7   | IORD- <sup>*3</sup>  | OFF  | OFF : The CS5-/RAS5-/IORD-/P85 pins of the CPU can be used for purposes other than       |

|     |                      |      | DMA transfer over EXT-BUS.                                                               |

|     |                      |      | ON : The CS5-/RAS5-/IORD-/P85 pins of the CPU are used as IORD- for DMA transfer over    |

|     |                      |      | EXT-BUS.                                                                                 |

| 8   | IOWR-*3              | OFF  | OFF : The CS4-/RAS4-/IOWR-/P84 pins of the CPU can be used for purposes other than       |

|     |                      |      | DMA transfer over EXT-BUS.                                                               |

|     |                      |      | ON : The CS4-/RAS4-/IOWR-/P84 pins of the CPU can be used as IOWR- for DMA transfer over |

|     |                      |      | EXT-BUS.                                                                                 |

\*1: To perform DMA0 transfer over EXT-BUS, set switches 1 and 2 to ON.

\*2: To perform DMA1 transfer over EXT-BUS, set switches 3 and 4 to ON.

\*3: To perform DMA transfer over EXT-BUS, set switches 7 and 8 to ON.

## 3.1.2. DIP Switch 2 (SW2)

DIP SW2 is used to set interrupts.

| No. | Symbol            | Def. | Description                                                                                                                  |

|-----|-------------------|------|------------------------------------------------------------------------------------------------------------------------------|

| 1   | NMI <sup>*1</sup> | ON   | OFF : The NMI/P20 pins of the CPU can be used for purposes other than the NMI from the NMI generator circuit.                |

|     |                   |      | ON : The NMI/P20 pins of the CPU are connected to the NMI from the NMI generator circuit.                                    |

| 2   | INTP130           | OFF  | OFF : The INTP130/P34 pins of the CPU can be used for purposes other than the INTP130<br>from the INTP130 generator circuit. |

|     |                   |      | ON : The INTP130/P34 pins of the CPU are connected to the INTP130 from the INTP130 generator circuit.                        |

| 3   | I_UART0           | OFF  | OFF : The INTP131/SO2/P35 pins of the CPU can be used for purposes other than the UART0 interrupt of the TL16PIR552.         |

|     |                   |      | ON : The INTP131/SO2/P35 pins of the CPU are connected to the INTRPT0 pin of the<br>TL16PIR552 (UART0 interrupt).            |

| 4   | I_UART1           | OFF  | OFF The INTP132/SI2/P36 pins of the CPU can be used for purposes other than the UART1 interrupt of the TL16PIR552.           |

|     |                   |      | ON : The INTP132/SI2/P36 pins of the CPU are connected to the INTRPT1 pin of the<br>TL16PIR552 (UART1 interrupt).            |

| 5   | I_PRT             | OFF  | OFF : The INTP133/SCK2-/P37 pins of the CPU can be used for purposes other than the<br>PRINTER interrupt of the TL16PIR552.  |

|     |                   |      | ON : The INTP133/SCK2-/P37 pins of the CPU are connected to the PINTR- pin of the<br>TL16PIR552 (PRINTER interrupt).         |

| 6   | I_TMR1            | OFF  | OFF : The INTP140/P114 pins of the CPU can be used for purposes other than the timer 1 interrupt of the TIC (nPD71054).      |

|     |                   |      | ON : The INTP140/P114 pins of the CPU are connected to the TOUT1 pin of the TIC (nPD71054) (timer 1 interrupt).              |

| 7   | I_ISA             | OFF  | Reserved by the system. Must be set to OFF.                                                                                  |

| 8   | Not used          | OFF  |                                                                                                                              |

\*1: To use the ROM monitor for the Multi debugger, set switch 1 to ON.

## 3.1.3. DIP Switch 3 (SW3)

DIP SW3 is used to set EXT-BUS interrupts.

| No. | Symbol | Def. | Description                                                                           |

|-----|--------|------|---------------------------------------------------------------------------------------|

| 1   | EXINT0 | OFF  | OFF : The INTP150/P124 pins of the CPU can be used for purposes other than interrupts |

|     |        |      | from EXT-BUS.                                                                         |

|     |        |      | ON : The INTP150/P124 pins of the CPU are connected to INT0 of EXT-BUS.               |

| 2   | EXINT1 | OFF  | OFF : The INTP151/P125 pins of the CPU can be used for purposes other than interrupts |

|     |        |      | from EXT-BUS.                                                                         |

|     |        |      | ON : The INTP151/P125 pins of the CPU are connected to INT1 of EXT-BUS.               |

| 3   | EXINT2 | OFF  | OFF : The INTP152/P126 pins of the CPU can be used for purposes other than interrupts |

|     |        |      | from EXT-BUS.                                                                         |

|     |        |      | ON : The INTP152/P126 pins of the CPU are connected to INT2 of EXT-BUS.               |

| 4   | EXINT3 | OFF  | OFF : The INTP153/P127 pins of the CPU can be used for purposes other than interrupts |

|     |        |      | from EXT-BUS.                                                                         |

|     |        |      | ON : The INTP153/P127 pins of the CPU are connected to INT3 of EXT-BUS.               |

## 3.1.4. DIP Switch 4 (SW4)

DIP SW4 is used to set up the SIMM type and time-over ready interrupts.

| No. | Symbol                | Def. | Description                                                                                                                                                                                                                                                            |  |  |

|-----|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | FLS_WP                | OFF  | Reserved by the system. Must be set to OFF.                                                                                                                                                                                                                            |  |  |

| 2   | FLS_VPP               | OFF  | Reserved by the system. Must be set to OFF.                                                                                                                                                                                                                            |  |  |

| 3   | TOVEN <sup>*1</sup>   | ON   | <ul> <li>OFF : A time-over ready interrupt does not occur if a bus cycle does not end within a fixed period of time.</li> <li>OFF : A time-over ready interrupt occurs if a bus cycle does not end within a fixed period of time to make the bus cycle end.</li> </ul> |  |  |

| 4   | SIMMEDO <sup>*2</sup> | OFF  | OFF : Set the contact to OFF when the SIMM is not of EDO type.<br>ON : Set the contact to ON when the SIMM is of EDO type.                                                                                                                                             |  |  |

| 5   | NMI/130               | OFF  | Reserved by the system. Must be set to OFF.                                                                                                                                                                                                                            |  |  |

| 6   | Not used              | OFF  |                                                                                                                                                                                                                                                                        |  |  |

| 7   | Not used              | OFF  |                                                                                                                                                                                                                                                                        |  |  |

| 8   | Not used              | OFF  |                                                                                                                                                                                                                                                                        |  |  |

\*1: For an explanation of time-over ready interrupts, see Section 12.1.

\*2: Setting this switch does not cause any switching in the hardware. The settings of this switch are read by the ROM monitor for the Multi debugger and used to initialize the DRAM controller inside the CPU.

## 3.1.5. DIP Switch 5 (SW5)

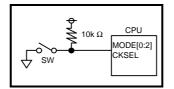

DIP SW5 is used to set the states of CPU pins.

| No. | Symbol | Def. | Description                                                                                |  |  |

|-----|--------|------|--------------------------------------------------------------------------------------------|--|--|

|     |        |      |                                                                                            |  |  |

| 1   | MODE0  | ON   | OFF : Sets the MODE0 pin of the CPU to High.                                               |  |  |

|     |        |      | ON : Sets the MODE0 pin of the CPU to Low.                                                 |  |  |

| 2   | MODE1  | ON   | OFF : Sets the MODE1 pin of the CPU to High.                                               |  |  |

|     |        |      | ON : Sets the MODE1 pin of the CPU to Low.                                                 |  |  |

| 3   | MODE2  | ON   | OFF : Sets the MODE2 pin of the CPU to High.                                               |  |  |

|     |        |      | ON Sets the MODE2 pin of the CPU to Low.                                                   |  |  |

| 4   | CKSEL  | ON   | OFF : Sets the CKSEL pin of the CPU to High (direct mode).                                 |  |  |

|     |        |      | ON : Sets the CKSEL pin of the CPU to Low (PLL mode).                                      |  |  |

| 5   | M3_NML | ON   | Reserved by the system. Must be set to ON.                                                 |  |  |

| 6   | M3_HI  | OFF  | Reserved by the system. Must be set to OFF.                                                |  |  |

| 7   | J232C  | OFF  | J232C and JFLASH are used in combination, as follows:                                      |  |  |

|     |        |      | [J232C, JFLASH]                                                                            |  |  |

|     |        |      | [OFF, OFF]: Pins P22 to P27 of the CPU can be used for purposes other than those described |  |  |

|     |        |      | below.                                                                                     |  |  |

| 8   | JFLASH | OFF  | [ON, OFF] : Pins P22 to P27 of the CPU are connected to the JRS232C connector, thus        |  |  |

|     |        |      | enabling the JRS232C connector. (The J232C-LED lights.)                                    |  |  |

|     |        |      | [X, ON] : The system enters the mode in which writing to the built-in flash ROM of the CPU |  |  |

|     |        |      | is possible using a writer, thus enabling the JFLASH connector. (The                       |  |  |

|     |        |      |                                                                                            |  |  |

|     |        |      | JFLASH-LED lights.)                                                                        |  |  |

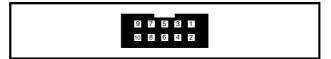

## 3.1.6. DIP Switch 6 (SW6)

DIP SW6 is used to select the I/O address of the ISA bus. Switch contacts 1 to 8 correspond to A4 to A11 of the ISA bus address. (A12 to A15 are fixed to 0.) Therefore, this switch can be used to select an I/O address in the range of 000xH to 0FFxH. When a switch contact is OFF, it represents 1. When it is ON, it represents 0. The default is 0200H.

| No. | Symbol | Def. | Description                                          |

|-----|--------|------|------------------------------------------------------|

| 1   | A4     | ON   | Select the I/O address of the ISA bus. (OFF=1, ON=0) |

| 2   | A5     | ON   |                                                      |

| 3   | A6     | ON   |                                                      |

| 4   | A7     | ON   |                                                      |

| 5   | A8     | ON   |                                                      |

| 6   | A9     | OFF  |                                                      |

| 7   | A10    | ON   |                                                      |

| 8   | A11    | ON   |                                                      |

## 3.1.7. DIP Switch 7 (SW7)

The settings of this switch can be read by the CPU via a general-purpose port. When the ROM monitor for the Multi debugger is used, some of the bits are reserved. See Sections 4.3.7 and 6.5 for details.

### 3.2. JUMPER SWITCHES

The RTE-V850E/MS1-PC features four jumper switches: JP2, JP3, JP5, and JP6. The functions of these jumper switches are explained below.

#### 3.2.1. JP2

JP2 is reserved by the system. Leave it open.

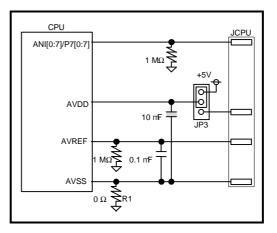

## 3.2.2. AVDD Power Switching Jumper Switch (JP3)

JP3 is used to select the power to be supplied to the AVDD pin of the CPU. (See Section 10.9.)

| JP3 setting          | Description                                                                         |

|----------------------|-------------------------------------------------------------------------------------|

| Jumper pins 1 and 2. | The same power (+5V) as that supplied to the HVDD pin of the CPU is supplied to the |

|                      | AVDD pin of the CPU. (Factory setting)                                              |

| Jumper pins 2 and 3. | The AVDD signal from the JCPU connector is supplied to the AVDD pin of the CPU.     |

The AVSS pin of the CPU is connected to GND via resistor R1 (0 W) located at the rear of JP3. To isolate the AVSS pin from GND and supply AVSS from the JCPU connector, remove resistor R1.

## 3.2.3. ROM Size Switching Jumper Switch (JP5)

JP5 must be set according to the size of the mounted ROM.

| JP5 setting              | Description                                                                                           |

|--------------------------|-------------------------------------------------------------------------------------------------------|

| Leave pins 1 and 2 open. | Leave the pins open when 128 Kbytes ( $64K \times 16$ bits) or 256 Kbytes ( $128K \times 16$ bits) of |

|                          | ROM is mounted. (Factory setting)                                                                     |

| Jumper pins 1 and 2.     | Jumper the pins when 512 Kbytes (256K $	imes$ 16 bits) of ROM is mounted.                             |

## 3.2.4. TIC Clock Switching Jumper Switch (JP6)

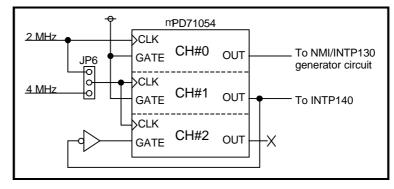

JP6 is used to select the clock pulses to be supplied to counters #1 and #2 of the TIC (mPD71054). (See Section 6.3.)

|   | JP6 setting          | Description                                                                         |

|---|----------------------|-------------------------------------------------------------------------------------|

|   | Jumper pins 1 and 2. | 2-MHz clock pulses are supplied to counters #1 and #2 of the TIC. (Factory setting) |

| I | Jumper pins 2 and 3. | 4-MHz clock pulses are supplied to counters #1 and #2 of the TIC.                   |

## 3.3. SWITCH

The RTE-V850E/MS1-PC contains the SW\_RESET switch.

## 3.3.1. Reset Switch (SW\_RESET)

SW\_RESET is a reset switch. Pressing this switch resets both the CPU and the board. (See Section 10.2.)

## 3.4. LEDs

The RTE-V850E/MS1-PC contains LEDs to indicate its status. The functions of the LEDs are explained below.

| LED name | Description                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------|

| POWER    | Lights when power is supplied to the board.                                                                |

| CS0      | Lights when the CS0- pin of the CPU goes Low.                                                              |

| CS1      | Lights when the CS1- pin of the CPU goes Low.                                                              |

| CS2      | Lights when the CS2- pin of the CPU goes Low.                                                              |

| CS3      | Lights when the CS3- pin of the CPU goes Low.                                                              |

| CS4      | Lights when the CS4- pin of the CPU goes Low.                                                              |

| CS5      | Lights when the CS5- pin of the CPU goes Low.                                                              |

| CS6      | Lights when the CS6- pin of the CPU goes Low.                                                              |

| CS7      | Lights when the CS7- pin of the CPU goes Low.                                                              |

| WAIT     | Lights when the WAIT- pin of the CPU goes Low.                                                             |

| TOVER    | Lights when a time-over ready interrupt occurs.                                                            |

| JFLASH   | Lights when the JFLASH connector is enabled.                                                               |

| J232C    | Lights when the JRS232C connector is enabled.                                                              |

| 7Seg-LED | Can be made to light depending on the contents of the output of a general-purpose port. (See Section 6.4.) |

## 3.5. CONNECTORS AND SOCKETS

The RTE-V850E/MS1-PC features several connectors and sockets. These are explained below.

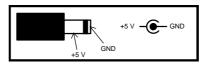

#### 3.5.1. Power Supply Connector (JPOWER)

When this board is to be used as a standalone, that is, without being inserted in an ISA bus slot, the board should be supplied with power from an external power supply by connecting it to the JPOWER connector.

The external power should be one rated as listed below.

Voltage: 5 V

Current:Maximum of 2 A (excluding the current supplied to the JEXT connector)Mating connector:Type A (5.5 mm in diameter)

Polarity:

When attaching an external power supply to the board, <u>pay</u> <u>careful attention to its connector polarity</u>. When inserting the board into the ISA bus slot, do not attach the JPOWER connector to an external power supply.

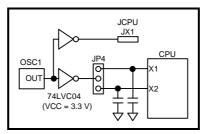

## 3.5.2. Crystal Socket (JP4)

JP4 has two roles. Namely, it is used to select the clock supplied to the CPU and also acts as the connector for the crystal oscillator. (See Section 10.7.)

| JP4 setting                              | Description                                                             |  |  |

|------------------------------------------|-------------------------------------------------------------------------|--|--|

| Mount a crystal oscillator between pins  | The mounted crystal oscillator is connected to pins X1 and X2 of the    |  |  |

| X1 and X2.                               | CPU.                                                                    |  |  |

| Jumper pin X1 and the center pin of JP4. | The oscillator mounted on the OSC1 socket is connected to pin X1 of the |  |  |

|                                          | CPU.                                                                    |  |  |

## 3.5.3. Oscillator Socket (OSC1)

The OSC1 socket is used to mount the oscillator used to supply clock pulses to the CPU.

The crystal oscillator mounted on JP4 can also be used to supply clock pulses to the CPU, by using JP4. (See Section 10.7.)

On the OSC1 socket, a 5V oscillator of 8-pin DIP type (half type) must be mounted.

When mounting an oscillator, pay careful attention to the orientation of pin 1. If the leads of the oscillator are short, the frame (outer coating)

of the oscillator may be short-circuited with the socket pins. 5V power is supplied to the oscillator.

## 3.5.4. DRAM-SIMM Sockets

The DRAM-SIMM socket can hold a 72-pin SIMM (known as a module in the case of PC/AT machines. it's DRAM has Row-Address and Column-Address of same bit width, and It's has 4 separate RAS-signal lines.) with a capacity of 4 or 8 Mbytes, and can also accept an EDO type DRAM-SIMM in addition to normal DRAM-SIMMs. The capacity of the connected SIMM can be read through the PIO port. (See Section 6.6.)

A 16-/32-Mbyte SIMM cannot be used.

#### 3.5.5. ROM Sockets

The RTE-V850E/MS1-PC has ROM sockets to hold 40-pin ROM chips to provide standard 128 Kbytes ( $64K \times 16$  bits). When the standard ROM is to be replaced to enable the use of the Multi debugger, it must be replaced by a ROM having an access time of less than 120 ns. When mounting ROM of a different capacity, it may be necessary to switch JP5 on the board. (See Section 3.2.3.)

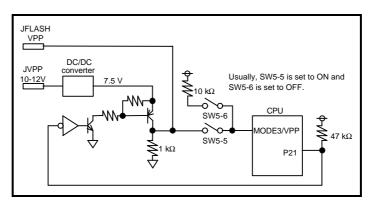

### 3.5.6. Self-Writing Power Supply Connector (JVPP)

To enable self-writing to the built-in flash ROM of the CPU, 7.5V power is required. The JVPP connector is used to supply the power for generating the 7.5V power.

By supplying <u>**10 to 12V</u>** power to this connector and setting pin P21 of the CPU to Low, 7.5V power is supplied to the VPP pin of the CPU. (See Section 10.6.)</u>

The pins of the JVPP connector are listed in the table below.

| JVPP pin No. | Name   | Input/ | Description                                 |  |

|--------------|--------|--------|---------------------------------------------|--|

|              |        | output |                                             |  |

| 1            | 10-12V | Input  | To be connected to 10 to 12V power supply.  |  |

| 2            | GND    | Input  | To be connected to GND of the power supply. |  |

| 3            | NC     |        | Not to be connected.                        |  |

#### 3.5.7. Connector for ROM Emulation (JROM\_EM)

JROM\_EM are the test pins used to connect a ROM in-circuit type debugger. These test pins accept control signals from the ROM in-circuit debugger. The signal names and functions are listed in the table below.

| JROM_EM pin No. | Signal name | Input/output | Function                                                                                                                                                                                                                           |

|-----------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | RESET-      | Input        | Connects the reset request signal from the ROM in-circuit debugger. The CPU is reset when a Low level signal is input. The input is pulled up by a $1-k\Omega$ resistor on the board. (See Section 10.2.)                          |

| 2               | NMI-        | Input        | Connects the NMI request signal (break request) from the ROM in-circuit debugger. The NMI is input to the CPU when a Low level signal is input. The input is pulled up by a $1-k\Omega$ resistor on the board. (See Section 10.3.) |

| 3               | GND         |              | Ground pin to ground the ROM in-circuit debugger.                                                                                                                                                                                  |

## 3.5.8. Serial Connectors (JSIO1, JSIO2)

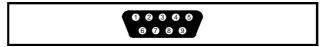

The JSIO1 and JSIO2 connectors are used for the RS-232C interface controlled by the serial controller (TL16PIR552). Regarding the connector shapes, JSIO1 is a 9-pin D-SUB RS-232C connector like that normally provided on the PC/AT, while JSIO2 is a pin header type connector with a pitch of 2.54 mm. All signals at both of these connectors are converted to RS-232C level. The pin arrangements of these connectors are shown below, after which the signal assignments are listed.

For the connection signals when the connectors are connected to the host, the table lists the wiring for both the D-SUB 9 pins and D-SUB 25 pins on the host side. (Regular cross-cable wiring is used for these connections.)

The pin arrangement of JSIO2 is identical to that of JSIO1 when a push-fit connector with a ribbon cable is connected to JSIO2.

**JSIO1 Pin Arrangement**

| JSIO1 pin No. | JSIO2 pin No. | Signal name | Input/output | Connector pin No | o. on the host side |

|---------------|---------------|-------------|--------------|------------------|---------------------|

|               |               |             |              | D-SUB9           | D-SUB25             |

| 1             | 1             | DCD         | Input        |                  |                     |

| 2             | 3             | RxD(RD)     | Input        | 3                | 2                   |

| 3             | 5             | TxD(SD)     | Output       | 2                | 3                   |

| 4             | 7             | DTR(DR)     | Output       | 1, 6             | 6, 8                |

| 5             | 9             | GND         |              | 5                | 7                   |

| 6             | 2             | DSR(ER)     | Input        | 4                | 20                  |

| 7             | 4             | RTS(RS)     | Output       | 8                | 5                   |

| 8             | 6             | CTS(CS)     | Input        | 7                | 4                   |

| 9             | 8             | RI          | Input        |                  |                     |

|               | 10            | NC          |              |                  |                     |

**JSIO2** Pin Arrangement

## 3.5.9. Parallel Connector (JPRT)

The JPRT connector is used for the parallel interface controlled by the parallel (printer) controller (TL16PIR552). It is a pin header type connector with a pitch of 2.54 mm. All signals at this connector are at the RS-232C level. Its pin arrangement and signal assignment are shown and listed below. The pin arrangement of JPRT is identical to the 25-pin D-SUB connector like that normally provided on the PC/AT when a push-fit connector with a ribbon cable is used.

| 2 2 4 6 8 10 12 14 16 18 20 22 24 26 |

|--------------------------------------|

| 1 3 5 7 9 11 13 15 17 19 21 23 25    |

| JPRT pin No. | Signal name | JPRT pin No. | Signal name |

|--------------|-------------|--------------|-------------|

| 1            | STB-        | 2            | AUTO_FD-    |

| 3            | D0          | 4            | ERROR-      |

| 5            | D1          | 6            | INIT-       |

| 7            | D2          | 8            | SELECT_IN-  |

| 9            | D3          | 10           | GND         |

| 11           | D4          | 12           | GND         |

| 13           | D5          | 14           | GND         |

| 15           | D6          | 16           | GND         |

| 17           | D7          | 18           | GND         |

| 19           | ACK-        | 20           | GND         |

| 21           | BUSY        | 22           | GND         |

| 23           | PE          | 24           | GND         |

| 25           | SELECT      | 26           | NC          |

JPRT Pin Arrangement

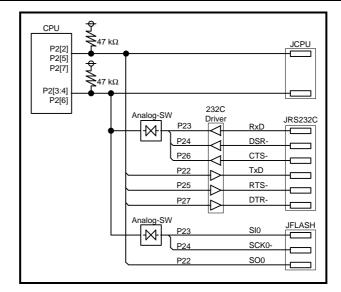

## 3.5.10. Serial Connector (JRS232C)

The JRS232C connector is an RS-232C connector controlled by the built-in UART of the CPU. (See Section 10.8.) This connector is a pin header type connector with a pitch of 2.54 mm. When a push-fit connector with a ribbon cable is connected to JRS232C, the pin arrangement of JRS232C is identical to that of a 9-pin D-SUB RS-232C connector like that normally provided on a PC/AT. All signals are converted to the RS-232C level.

To enable the use of JRS232C, SW5 must be set. (See Section 3.1.5.)

When JRS232C is enabled for use, the J232C-LED lights. (See Section 3.4.)

The pin arrangement of the JRS232C connector is shown below, after which the signal assignment is listed. For an explanation of the connections when the connector is connected to a personal computer (host), see the table given in Section 3.5.8.

#### JRS232C Signal name Input/output Correspondin pin No. g CPU pin 1 NC Input 3 RxD(RD) P23 Input 5 TxD(SD) Output P22 7 DTR(DR) Output P27 9 GND DSR(ER) P24 2 Input 4 RTS(RS) P25 Output CTS(CS) P26 6 Input NC 8 10 NC

JRS232C Pin Arrangement

## 3.5.11. Flash Writing Connector (JFLASH)

The JFLASH connector is used to connect a writer when writing is to be performed to the built-in flash ROM of the CPU using that writer. The NEC FP-100 flash writer can be connected directly to this connector.

To enable the use of JFLASH, SW5 must be set. (See Section 3.1.5.) When JFLASH is enabled, the JFLASH-LED lights. (See Section 3.4.) For details of writing to flash ROM, see Chapter 11.

| JFLASH<br>pin No. | Signal name | Input/<br>output | Remarks                                     |

|-------------------|-------------|------------------|---------------------------------------------|

| 1                 | SO0         | Output           | Synchronous serial data output (CMOS level) |

| 2                 | SI0         | Input            | Synchronous serial data input (CMOS level)  |

| 3                 | SCK0-       | Input            | Synchronous serial clock input (CMOS level) |

| 4                 | RESET-      | Input            | Reset input                                 |

| 5                 | VPP         | Input            | VPP input                                   |

| 6                 | +3.3V       | Output           | CPU core power level output                 |

| 7                 | +5V         | Output           | CPU-I/O power level output                  |

| 8                 | GND         | -                | Ground                                      |

| 9                 | NC          | -                | Not connected                               |

| (10)              | NC          | -                | Not connected (no pin)                      |

## JFLASH Pin Arrangement

## 3.5.12. Processor Pin Connector (JCPU)

The pins of the CPU are connected to the JCPU connector. For an explanation of the connections on the board, see Chapter 10.

| JCPU<br>pin No. | Signal name              | JCPU<br>pin No. | Signal name          |

|-----------------|--------------------------|-----------------|----------------------|

| 1               | GND                      | 2               | INTP142/SI3/P116     |

| 3               | INTP141/SO3/P115         | 4               | INTP140/P114         |

| 5               | TI14/P113                | 6               | TCLR14/P112          |

| 7               | TO141/P111               | 8               | TO140/P110           |

| 9               | +3.3V                    | 10              | Not connected        |

| 11              | +3.3V                    | 12              | JX1 <sup>*1</sup>    |

| 13              | GND                      | 14              | CKSEL                |

| 15              | MODE0                    | 16              | MODE1                |

| 17              | MODE2                    | 18              | MODE3/VPP            |

| 19              | RESET-                   | 20              | INTP153/ADTRG/P127   |

| 21              | +5V                      | 22              | INTP152/P126         |

| 23              | INTP151/P125             | 24              | INTP150/P124         |

| 25              | TI15/P123                | 26              | TCLR15/P122          |

| 27              | TO151/P121               | 28              | TO150/P120           |

| 29              | CLKOUT/PX7               | 30              | WAIT-/PX6            |

| 31              | GND                      | 32              | REFRQ-/PX5           |

| 33              | JCPU_WAIT- <sup>*2</sup> | 34              | HLDRQ-/P97           |

| 35              | HLDAK-/P96               | 36              | OE-/P95              |

| 37              | ADV-/BCYST-/P94          | 38              | WE-/P93              |

| 39              | RD-/P92                  | 40              | UCAS-/UWR-/P91       |

| 41              | +3.3V                    | 42              | LCAS-/LWR-/P90       |

| 43              | CS7-/RAS7-/P87           | 44              | CS6-/RAS6-/P86       |

| 45              | CS5-/RAS5-/IORD-/P85     | 46              | CS4-/RAS4-/IOWR-/P84 |

| 47              | CS3-/RAS3-/P83           | 48              | CS2-/RAS2-/P82       |

| 49              | CS1-/RAS1-/P81           | 50              | CS0-/RAS0-/P80       |

| 51              | +5V                      | 52              | +5V                  |

| 53              | A23/P67                  | 54              | A22/P66              |

| 55              | A21/P65                  | 56              | A20/P64              |

| 57              | A19/P63                  | 58              | A18/P62              |

| 59              | A17/P61                  | 60              | A16/P60              |

| 61              | GND                      | 62              | A15/PB7              |

| 63              | A14/PB6                  | 64              | A13/PB5              |

| 65              | A12/PB4                  | 66              | A11/PB3              |

| 67              | A10/PB2                  | 68              | A9/PB1               |

| 69              | A8/PB0                   | 70              | GND                  |

| 71              | +3.3V                    | 72              | A7/PA7               |

| 73              | A6/PA6                   | 74              | A5/PA5               |

| 75              | A4/PA4                   | 76              | A3/PA3               |

| 77              | A2/PA2                   | 78              | A1/PA1               |

| 79              | A0/PA0                   | 80              | +5V                  |

- \*1: The output of the oscillator mounted on the OSC1 socket is converted to the 3.3V level and output to this pin. (See Section 10.7.)

- \*2: WAIT- input from the JCPU connector. This is used to insert waits into a bus cycle via the JCPU connector.

| JCPU<br>pin No. | Signal name         | JCPU<br>pin No. | Signal name         |

|-----------------|---------------------|-----------------|---------------------|

| 81              | GND                 | 82              | D15/P57             |

| 83              | D14/P56             | 84              | D13/P55             |

| 85              | D12/P54             | 86              | D11/P53             |

| 87              | D10/P52             | 88              | D9/P51              |

| 89              | D8/P50              | 90              | GND                 |

| 91              | +3.3V               | 92              | D7/P47              |

| 93              | D6/P46              | 94              | D5/P45              |

| 95              | D4/P44              | 96              | D3/P43              |

| 97              | D2/P42              | 98              | D1/P41              |

| 99              | D0/P40              | 100             | +3.3V               |

| 101             | +5V                 | 102             | INTP103/DMARQ3-/P07 |

| 103             | INTP102/DMARQ2-/P06 | 104             | INTP101/DMARQ1-/P05 |

| 105             | INTP100/DMARQ0-/P04 | 106             | TI10/P03            |

| 107             | TCLR10/P02          | 108             | TO101/P01           |

| 109             | TO100/P00           | 110             | GND                 |

| 111             | GND                 | 112             | INTP113/DMAAK3-/P17 |

| 113             | INTP112/DMAAK2-/P16 | 114             | INTP111/DMAAK1-/P15 |

| 115             | INTP110/DMAAK0-/P14 | 116             | TI11/P13            |

| 117             | TCLR11/P12          | 118             | TO111/P11           |

| 119             | TO110/P10           | 120             | INTP123/TC3-/P107   |

| 121             | +3.3V               | 122             | INTP122/TC2-/P106   |

| 123             | INTP121/TC1-/P105   | 124             | INTP120/TC0-/P104   |

| 125             | TI12/P103           | 126             | TCLR12/P102         |

| 127             | TO121/P101          | 128             | TO120/P100          |

| 129             | ANI7/P77            | 130             | ANI6/P76            |

| 131             | +5V                 | 132             | ANI5/P75            |

| 133             | ANI4/P74            | 134             | ANI3/P73            |

| 135             | ANI2/P72            | 136             | ANI1/P71            |

| 137             | ANI0/P70            | 138             | AVDD*3              |

| 139             | AVSS <sup>*3</sup>  | 140             | AVREF               |

| 141             | GND                 | 142             | NMI/P20             |

| 143             | P21                 | 144             | TXD0/SO0/P22        |

| 145             | RXD0/SI0/P23        | 146             | SCK0-/P24           |

| 147             | TXD1/SO1/P25        | 148             | RXD1/SI1/P126       |

| 149             | SCK1-/P27           | 150             | +3.3V               |

| 151             | +3.3V               | 152             | INTP133/SCK2-/P37   |

| 153             | INTP132/SI2/P36     | 154             | INTP131/SO2/P35     |

| 155             | INTP130/P34         | 156             | TI13/P33            |

| 157             | TCLR13/P32          | 158             | TO131/P31           |

| 159             | TO130/P30           | 160             | INTP143/SCK3-/P117  |

\*3: For an explanation of how to connect AVDD and AVSS to the CPU, see Section 10.9.

## 3.6. EXTENSION BUS CONNECTOR (JEXT)

The JEXT connector is provided to enable the extension of memory or I/O. This connector is internally connected to the local bus of the Base board. For details of this connector, see Chapter 8.

## 4. USING THE BOARD WITH THE MULTI DEBUGGER

This chapter explains how to set up the RTE-V850E/MS1-PC board when it is being used in combination with the Multi debugger of Green Hills Software, as the well as the cautions to be observed.

## 4.1. SOFTWARE

To use the RTE-V850E/MS1-PC with the Multi debugger, two software products must be installed, in addition to the Multi debugger.

One is the Midas server (rteserv). This software product controls RTE for WIN32 in accordance with the instructions received from the Multi debugger.

The other is RTE for WIN32. This software product is used for communication with the board.

For an explanation of how to install each software product, see the installation manual supplied with the product.

## 4.2. METHODS OF USE

The RTE-V850E/MS1-PC can be used in combination with the Multi debugger in either of two ways. In one case, the board is inserted into the ISA bus slot of a PC/AT or compatible, so that communication is performed via the ISA bus.

In the other case, the board is not inserted into the ISA bus, but is supplied with +5V power from JPOWER and connected to the host with an RS-232C cable, so that communication is performed via the RS-232C cable.

## 4.3. SETTING UP THE BOARD

The following explains how to set the switches on the board to enable use of the board with the Multi debugger.

## 4.3.1. DIP Switch 1 (SW1)

Usually, this switch need not be changed from the default settings. (See Section 3.1.1.)

## 4.3.2. DIP Switch 2 (SW2)

Set switch 1 of SW2 to the ON position to connect the NMI from the NMI generator circuit to CPU pins. The other switches usually need not be changed from their default positions. (See Section 3.1.2.)

## 4.3.3. DIP Switch 3 (SW3)

Usually, this switch need not be changed from the default settings. (See Section 3.1.3.)

## 4.3.4. DIP Switch 4 (SW4)

When using a SIMM, set contact 4 of SW4 according to whether the SIMM is of EDO or FastPage type. (If the user program is designed to set the SIMM-related SFRs, contact 4 of SW4 need not be set.) The other switches usually need not be changed from their default positions. (See Section 3.1.4.)

## 4.3.5. DIP Switch 5 (SW5)

Contacts 1 to 3, 5, and 6 of SW5 need not be changed from the default positions. The other switches usually need not be changed from their default positions, either. (See Section 3.1.5.)

## 4.3.6. DIP Switch 6 (SW6)

When inserting this board into an ISA bus slot, use this switch to set the I/O address on the host that is to be used by this board. The default I/O address is 020xH (0200H to 020FH). When setting the I/O address, make sure that the address is not the same as that of the mother board or any other board. (See Section 3.1.6.)

When not inserting this board into the ISA bus slot, this switch need not be changed from its default positions.

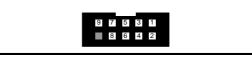

## 4.3.7. DIP Switch 7 (SW7)

DIP switch 7 is connected to the general-purpose input ports. For the ROM monitor for the Multi debugger, this switch is used to set the baud rate at which the board will communicate with the Multi debugger via the RS-232C interface and to set the profiler period. Contacts 5 to 8 of SW7 must be set to OFF.

| SW7 |     | V7 Baud rate                |  |

|-----|-----|-----------------------------|--|

| 1   | 2   |                             |  |

| ON  | ON  | Not used                    |  |

| OFF | ON  | 38400 baud                  |  |

| ON  | OFF | 19200 baud                  |  |

| OFF | OFF | 9600 baud (Factory setting) |  |

| SW7 |     | Profiler period                  |  |

|-----|-----|----------------------------------|--|

| 3   | 4   |                                  |  |

| ON  | ON  | The timer is not used.           |  |

| OFF | ON  | 200 Hz 5 ms                      |  |

| ON  | OFF | 100 Hz 10 ms                     |  |

| OFF | OFF | 60 Hz 16.67 ms (Factory setting) |  |

## Setting the Baud Rate

#### Setting the Profiler Period

## 4.3.8. JP2

Leave JP2 open.

## 4.3.9. AVDD Power Switching Jumper Switch (JP3)

Usually, this switch need not be changed from the default setting. (See Section 3.2.2.)

## 4.3.10. ROM Capacity Switching Jumper Switch (JP5)

Set JP5 according to the size of the ROM containing the monitor for the Multi debugger. (See Section 3.2.3.)

#### 4.3.11. TIC Clock Switching Jumper Switch (JP6)

Usually, this switch need not be changed from the default setting. (See Section 3.2.4.)

#### 4.4. PROCEDURES FOR USE

The procedures for using the RTE-V850E/MS1-PC are explained below.

#### 4.4.1. Procedure Involving the Insertion of the Board into ISA Bus Slot

When the board is inserted into an ISA bus slot in the PC, power (+5V) is supplied from the ISA bus to the board. In addition, the ISA bus can be used for communication with the debugger, so that programs are downloaded at high speed.

The board can be installed in the ISA bus slot according to the following procedure.

- <1> Set the I/O address of the PC that is to be used by the RTE-V850E/MS1-PC, using the appropriate switch on the board. Make sure that the I/O address is not the same as that of any other board. For an explanation of how to set this switch, see Section 3.1.6.

- <2> Turn off the power to the PC, open its housing, and select an ISA bus slot into which the board is to be inserted. If the slot is fitted with a rear panel, remove the panel.

- <3> Insert the board into the ISA bus slot. Make sure that the board does not touch any adjacent board. Fasten the rear panel, attached to the board, to the housing of the PC, using a screw.

- <4> Turn on the power to the PC, and check that the POWER-LED on the board lights. If the LED does not light, turn off the PC power immediately, and check the installation. If the system does not start normally (for example, if an error occurs during the installation of a device driver), it is likely that the set I/O address is the same as that of another board. Reconfirm the I/O address of the board by referring to the manuals supplied with the PC and other boards.

- <5> When the system is found to be normal, turn off the PC power again, and replace its housing.

- <6> Turn on the PC power, and check the installation using the Check RTE utility supplied with RTE for WIN32. (See the installation manual for RTE for WIN32.)

#### 4.4.2. Procedure for Using the Board as a Standalone

When the board is used as a standalone rather than being installed in the PC, it requires an external power supply. In addition, communication with the debugger is supported only by the RS-232C interface. This configuration is useful when the Multi debugger is used on a host other than a PC/AT or compatible, as well as when the board is used for hardware confirmation and expansion.

The board can be used as a standalone according to the following procedure.

- <1> Obtain an RS-232C cable (for connection with the host), an external power supply (+5V, 2A). In the case of the power supply, pay careful attention to its voltage and **connector polarity**. In addition, attach spacers to the four corners of the board, so that it will not pose any problem, regardless of where it is installed. See Sections 3.5.8 and 3.5.1 for an explanation of RS-232C cable connection and the power supply connector, respectively.

- <2> Using the corresponding DIP switch on the board, set the RS-232C baud rate. For an explanation of how to set this switch, see Section 4.3.7.

- <3> Connect the board to the host using the RS-232C cable. Also connect the external power supply to the JPOWER connector, then check that the POWER-LED on the board lights. If the LED does not light, turn off the power immediately, then check the connection.

- <4> Check the connection using the Check RTE utility supplied with RTE for WIN32. (See the installation manual provided with RTE for WIN32.)

### 4.5. ROM MONITOR FOR THE MULTI DEBUGGER

To enable the use of the RTE-V850E/MS1-PC in combination with the Multi debugger, ROM that contains the ROM monitor for the Multi debugger (RTEMON) must be mounted on the board. Cautions on the use of this ROM monitor are described below.

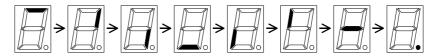

## 4.5.1. 7-Segment LED at Startup

When the ROM monitor for the Multi debugger is mounted, the 7-segment LED behaves as shown below when the power to the board is turned on. (The black portion is lit.)

1) Checking of the 7-segment LED (see the figure below)

- 2) Counting of numbers due to a simple memory check on SRAM

- 3) rteserv connection wait state. (The dot does not blink if the profiler timer is stopped.)

4) rteserv connected state. (The dot is either on or off depending on whether it was on or off when rteserv was connected.)

#### 4.5.2. ROM Monitor Work RAM

The ROM monitor uses the high-order 32 Kbytes (3E7-8000H to 3E7-FFFFH) of SRAM as its work RAM. User programs cannot, therefore, use this area and the image area of this area.

## 4.5.3. \_INIT\_SP Setting

\_INIT\_SP (stack pointer initial value) is set to 3E7-7FFCH (immediately before the monitor work RAM) by the monitor. (\_INIT\_SP can be changed in the Multi environment.)

## 4.5.4. Remote Connection

Either serial or ISA bus connection can be selected for operation with the Multi server (rteserv). To switch from serial connection to ISA bus connection or vice versa, it is necessary to reset the monitor (by pressing the reset switch on the rear panel) and run the Check RTE utility of RTE for WIN32.

## 4.5.5. Timer Interrupt

The profiler function of the Multi debugger cannot be used if timer interrupt is inhibited (see Section 4.3.7 for details of timer interrupt setting).

## 4.5.6. Hardware Initialization

Regarding the ROM, SRAM, and EDO-DRAM spaces, initializes the CPU (SFRs) internally as well as the board so that they are compatible with 40-MHz operation(See Section 7).

Regarding the SIMM space, only when a SIMM is mounted, the ROM monitor initializes the CPU (SFRs) internally so that it conforms to 40-MHz operation if a SIMM with an access time of 60 ns is mounted. Set the appropriate DIP switch according to whether the SIMM is of EDO or FastPage type. (See Section 3.1.4) At the time of a reset, the ROM monitor for the Multi debugger occurs 4 bytes writing and reading at the SIMM-Base-Address to detect a SIMM(Original data is write back).

## 4.6. APPLICATIONS USING MASKABLE INTERRUPTS

The following sections explain how to develop applications using maskable interrupts on the RTE-V850E/MS1-PC, as well as restrictions.

### 4.6.1. Interrupt Vectors

The interrupt vector area of the V850E/MS1, addresses 0000H to 07FFH, are fixed by the use of ROM, and cannot be changed. The ROM monitor for the Multi debugger provides an alternate vector area in SRAM, so that branch instructions for branching to the alternate vector area can be placed in the vector area of addresses 0000H to 07FFH.

If, for example, an interrupt with an exception code of 0080H is generated, the interrupt function of the CPU causes a branch to address 0080H, where there is a branch instruction for branching to offset address 0080H in the alternate vector area. Thus, by changing this alternate vector area in the same way as the original vector area, the user program can branch to an interrupt handling routine when an interrupt is generated.

A difference between an ordinary V850E/MS1 program and a program using Multi on the RTE-V850E/MS1-PC is that, for the former, the vector area is fixed at the time it is turned into ROM and the program need not establish (change) the area, while the latter must change a vector before enabling an interrupt.

The alternate vector area is located at addresses 3E7-8000H to 3E7-87FFH in SRAM. (Actually, reference/modification is possible from other addresses because an SRAM image is available.) For the above-mentioned interrupt with an exception code of 0080H, the instruction for branching to the desired interrupt handling routine must be written at address 3E7-8080H.

Actually, the interrupt vectors located at addresses 000-0000H to 000-07FFH and first referenced by the CPU, branch to FFE7-8000H to FFE7-87FFH. The CPU, however, masks bits 26 to 31 of the PC register to "0," so the vectors eventually branch to 3E7-8000H to 3E7-87FFH.

If the CPU has a built-in cache memory, a cache flush operation is required after a vector is changed. For the V850E/MS1, however, this is not required because it has no built-in cache memory.

A sample program for changing alternate vectors is shown on the next page. (This sample assumes

that the address of the interrupt handling routine relative to the alternate vector area is 22 bits or less.)

```

void SetAJump(int addr, int jmpdest) /* \leftarrowVector setting routine */

address where we're storing the 'jr' */

;; address where the 'jr' jumps to */

/* int addr;

/* int jmpdest;

1

int offset;

unsigned inst;

unsigned int *p ;

offset = impdest - addr;

inst = 0x07800000 /* 'jr' opcode */ | (offset & 0x003ffff);

*((UINT16 *)(addr )) = (inst >> 16) & 0xffff ;

*((UINT16 *)(addr + 2)) = (inst

) & Oxffff ;

main()

{

SetAJump((int)(0x080 + 0x3e78000) ,(int)IntEntry) ;

fexception code of the target interrupt */

/*

```

## 4.6.2. General Restrictions and Cautions

The restrictions and cautions on debugging applications that use maskable interrupts are described below:

- If an interrupt is generated before an alternate vector has been established, or if an interrupt is generated without establishing an alternate vector correctly, the program will break at the point where the interrupt is generated. The reason for this is that the initial value of an alternate vector is a branch instruction for branching to the break handling routine of the ROM monitor.

- 2) If the address of the interrupt handling routine relative to the alternate vector area exceeds 22 bits, either the value of at least one register must be destroyed or a relay point for branching must be established in order to branch to the interrupt handling routine.

- The alternate vector area is protected as an area managed by the ROM monitor. It cannot, therefore, be changed by downloading a program.

- 4) All peripheral devices including those related to interrupts can be initialized only with the reset switch on the board. If, therefore, a program is reloaded and executed after it has been executed, the effects of the previous execution of the program remain on the peripheral devices. For a program using peripheral devices, the following procedure must be observed if the program is to be executed from the beginning after it has been executed: Disconnect rteserv, press the reset button on the RTE-V850E/MS1-PC, and then reconnect rteserv.

- 5) A program must be set to the DI (disable interrupt) state at the beginning. Then, after the necessary peripheral devices and vectors have been established, the program must be set to the EI (enable interrupt) state.

#### 4.6.3. Restrictions and Cautions on Using Breakpoints

A breakpoint can be established within an interrupt handling routine to cause a break. After a break, the interrupt handling routine can be executed in single-step mode. In this case, note the following restrictions and cautions:

- 1) During a break, no maskable interrupts can be accepted.

- 2) The single-step function establishes a temporary break point for the next instruction. Consequently, if a user program in the EI (enable interrupts) state is executed in single-step mode, the program may accept an interrupt, branching to an interrupt handling routine, which, in turn, handles the interrupt, while a single instruction is executed in single-step mode. Even in single-step mode, therefore, pay careful attention to the cautions relating to breakpoints.

- 3) It is not possible to exit from an interrupt handling routine by using single-step execution. (To be more precise, single-step execution cannot be performed at the last "}" of an interrupt handling routine.) In addition, it is not possible to perform single-step execution of the reti instruction.

- 4) It is not possible to return from an interrupt handling routine to the previous routine by using the "Return" function of the debugger.

### 4.7. RTE COMMANDS

When using the board with the Multi debugger, connect the board to the Midas server (rteserv) to open the TARGET window. The RTE commands can be issued in this window. The following table lists the RTE commands.

| Command | Description                                      |

|---------|--------------------------------------------------|

| HELP, ? | Displays help messages.                          |

| INIT    | Initializes.                                     |

| VER     | Displays the version number.                     |

| SFR     | Changes or displays the internal register (SFR). |

#### **RTE Commands**

Some commands require parameters. All numeric parameters such as addresses and data are assumed to be hexadecimal numbers. The following numeric representations are <u>invalid</u>:

0x1234 1234H \$1234

## 4.7.1. HELP (?)

<Format> HELP [command-name]

Displays a list of RTE commands and their formats. A question mark (?) can also be used in place of the character string HELP. If no command name is specified in the parameter part, the HELP command lists all usable commands.

<Example> HELP SFR Displays help messages for the SFR command.

## 4.7.2. INIT

<Format> INIT Initializes the RTE environment. Usually, this command should not be used.

## 4.7.3. VER

<Format> VER

Displays the version number of the current RTE environment.

## 4.7.4. SFR

<Format> SFR[register-name[data]]

Displays the data in the CPU's internal register (SFR) or writes data into it.

When the parameters are omitted, this command displays a list of register names which can be specified with the SFR command.

When only the register-name parameter is specified, this command reads and displays the data in the specified register.

When both the register-name and data parameters are specified, this command writes the data into the specified register.

Specifying a display command for a read-inhibited register or a write command for a write-inhibited register results in an error. The access size for read or write is automatically set to the same size as that of the register.

#### 5. HARDWARE REFERENCES

This chapter describes the hardware of the RTE-V850E/MS1-PC.

#### 5.1. MEMORY MAP

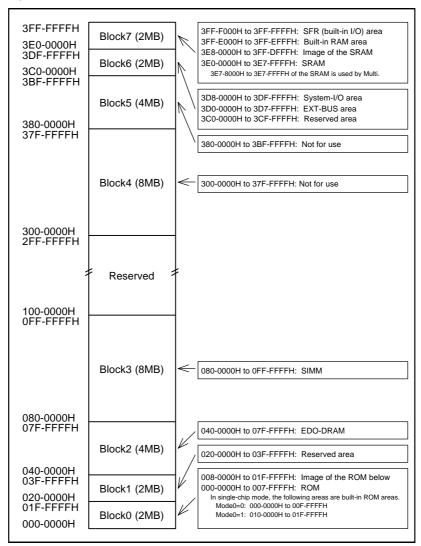

The memory assignment of the board is shown below.

Memory Map

#### 5.2. DETAILS OF THE MEMORY MAP

The memory map is explained in detail below. For an explanation of how to set the SFRs required to access these memory spaces, see Chapter 7.

#### CS0 space (Block0: 000-0000H to 01F-FFFFH, 16-bit ROM space)

This is the space for the ROM mounted on the board. A maximum of 512 Kbytes of ROM can be used. As standard,  $46K \times 16$  bits (128 Kbytes) of ROM with an access time of 120 ns or less is mounted. Wait control uses the programmable wait function of the CPU. For an explanation of the required wait count, see Chapter 7.

The ROM mounted as standard incorporates the Multi debugger monitor.

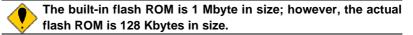

When the CPU is in single-chip mode, the built-in flash ROM of the CPU appears as part of this area. When the MODE0 pin of the CPU is Low, the built-in flash ROM area appears between 000-0000H and 00F-FFFFH. When the MODE0 pin is High, it appears between 010-0000H and 01F-FFFFH. Except for these areas, external ROM can be accessed even in single-chip mode.

#### CS1 space (Block1: 020-0000H to 03F-FFFFH, 16-bit reserved area)

This area is reserved by the system. Do not attempt to access this area. Operation is not guaranteed if this area is accessed.

#### CS2 space (Block2: 040-0000H to 07F-FFFFH, 16-bit EDO-DRAM space)

This is the space for the EDO-DRAM (Hyper-Page) mounted on the board. Two  $2M \times 8$ -bit EDO-DRAM chips (4 Mbytes) are mounted. The width of the data bus is set to 16 bits.

#### CS3 space (Block3: 080-0000H to 0FF-FFFFH, 16-bit SIMM space)