# ***RTE-V850ES/SA3-CB***

**ユーザーズ・マニュアル (Rev. 1.01)**

***Midas lab***

### 改訂履歴

| 実施日       | Revision | 章          | 内容                                       |

|-----------|----------|------------|------------------------------------------|

| 2002年7月5日 | 1.00     |            | 正式初版                                     |

| 2002年8月5日 | 1.01     | 5.4<br>9.1 | 修正<br>SW2 の機能変更と誤記訂正<br>割り込みベクタアドレスの誤記訂正 |

|           |          |            |                                          |

|           |          |            |                                          |

|           |          |            |                                          |

|           |          |            |                                          |

## 目次

|                                            |    |

|--------------------------------------------|----|

| 1. はじめに .....                              | 1  |

| 1.1. マニュアル表記について .....                     | 1  |

| 2. 機能 .....                                | 2  |

| 3. 主な特徴 .....                              | 3  |

| 4. 基本仕様 .....                              | 3  |

| 5. ボードの構成 .....                            | 4  |

| 5.1. リセット・スイッチ (SW_RESET) .....            | 4  |

| 5.2. 電源コネクタ (JPOWER) .....                 | 4  |

| 5.3. スイッチ 1 (SW1) .....                    | 4  |

| 5.4. スイッチ 2 (SW2) .....                    | 5  |

| 5.5. スイッチ 3 (SW3) .....                    | 5  |

| 5.6. スイッチ 4, 5 (SW4, SW5) .....            | 6  |

| 5.7. スイッチ 6 (SW6) .....                    | 6  |

| 5.8. スイッチ 7 (SW7) .....                    | 6  |

| 5.9. 7SEG-LED, xxx-LED .....               | 6  |

| 5.10. ROM エミュレータ用テストピン (JROM-EM1) .....    | 7  |

| 5.11. クリスタル・ソケット (JXTAL1) .....            | 7  |

| 5.12. AVDD 切り替えジャンパ (JP1) .....            | 7  |

| 5.13. LAN91C111:LINK 端子の設定ジャンパ (JP3) ..... | 8  |

| 5.14. ROM ソケット (U16) と 設定ジャンパ (JP2) .....  | 8  |

| 5.15. フラッシュ書き込みコネクタ (JFLASH1) .....        | 8  |

| 5.16. シリアル・コネクタ (JSIO1, JSIO2) .....       | 9  |

| 5.17. USB コネクタ (JUSB1) .....               | 10 |

| 5.18. LAN コネクタ (JLAN1) .....               | 10 |

| 5.19. JGBUS コネクタ (JGBUS) .....             | 10 |

| 5.20. 信号観測用コネクタ (J1, J2) .....             | 11 |

| 5.21. CPU 信号コネクタ (J3, J4) .....            | 12 |

| 6. ホスト PC との接続 .....                       | 14 |

| 6.1. RS-232C 接続 .....                      | 14 |

| 7. ハードウェア・リファレンス .....                     | 15 |

| 7.1. メモリ・I/O のマップ .....                    | 15 |

| 7.2. 推奨設定 .....                            | 17 |

| 7.2.1. CPU レジスタ .....                      | 17 |

| 7.3. メモリ詳細 .....                           | 17 |

| 7.3.1. SRAM (0100000 - 03FFFF) .....       | 17 |

| 7.3.2. UV-E PROM (0400000 - 047FFFF) ..... | 17 |

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| 7.4. IO 詳細 .....                                                                                  | 18 |

| 7.4.1. IO 一覧 .....                                                                                | 18 |

| 7.4.2. SW1 読出しポート(SW1 680000H [Read Only]) .....                                                  | 18 |

| 7.4.3. SW2 読出しポート(SW2 680100H [Read Only]) .....                                                  | 18 |

| 7.4.4. 7セグメント LED 表示データ出力ポート(7SEG-LED 680200H [Write Only]) .....                                 | 19 |

| 7.4.5. タイムオーバ・レディーLED クリア・パルス(TOVRDY_LED_CLRPLS 680300H [Write Only]) .....                       | 19 |

| 7.4.6. 割り込みコントローラ(PIC:680400H - 680430H [Read/Write]) .....                                       | 19 |

| 7.4.7. GBUS ACCESS CONTROL (680500H[Read/Write]) .....                                            | 21 |

| 7.4.8. MB-SRAM High ADDR (680600H[Read/Write]) .....                                              | 21 |

| 7.4.9. MB-FROM High ADDR (680610H[Read/Write]) .....                                              | 21 |

| 7.4.10. MB-EXTBUS-MEM High ADDR (680600H[Read/Write]) .....                                       | 21 |

| 7.4.11. MB-EXTBUS-IO High ADDR (680600H[Read/Write]) .....                                        | 21 |

| 7.4.12. UART (TL16C550C:680800H - 680870H) .....                                                  | 22 |

| 7.4.13. TIC (uPD71054 680900H ~ 680930FH) .....                                                   | 22 |

| 7.4.14. USB (ML60852A:681000H – 6810FEH) .....                                                    | 23 |

| 7.4.15. LANC (LAN91C111:684300H – 68430EH) .....                                                  | 24 |

| 8. ソフトウェア .....                                                                                   | 25 |

| 8.1. 初期化 .....                                                                                    | 25 |

| 8.2. uPD71054 に対する連続アクセス .....                                                                    | 25 |

| 8.3. ライブドリ .....                                                                                  | 25 |

| 8.4. タイマの使用例 .....                                                                                | 26 |

| 9. マスク割り込みを使用したアプリケーションの開発 .....                                                                  | 27 |

| 9.1. 割り込みベクタ .....                                                                                | 27 |

| 9.2. 一般的な制限事項 / 注意事項 .....                                                                        | 28 |

| 9.3. ダウンロード時の代替ベクタ領域書換え方法 .....                                                                   | 28 |

| 9.4. ブレーク・ポイント使用に関する制限事項 / 注意事項 .....                                                             | 29 |

| 10. CPU端子接続 .....                                                                                 | 30 |

| 10.1. 端子接続一覧 .....                                                                                | 30 |

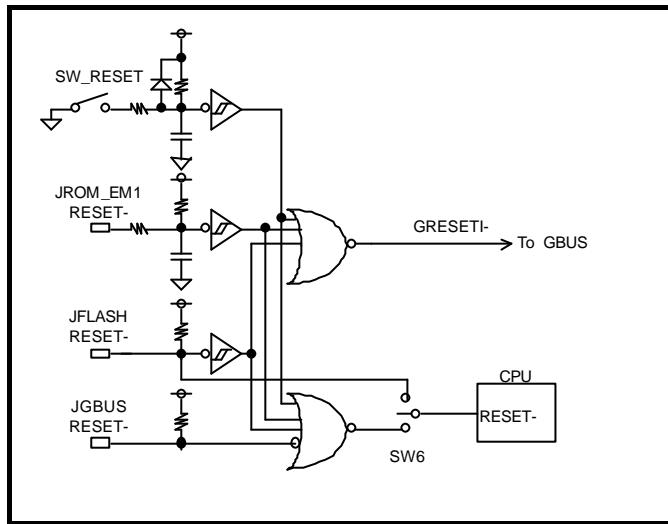

| 10.2. RESET- .....                                                                                | 31 |

| 10.3. PCM0/WAIT- .....                                                                            | 31 |

| 10.4. P00/NMI, P01/INTP0/TI2 .....                                                                | 32 |

| 10.5. P02/INTP1/TI3, P03/INTP2/TI4, P04/INTP3/TI5, P05/INTP4 .....                                | 32 |

| 10.6. P43/INTP00/TI0/TCLR0, P44/INTP01/TO0, P45/INTP10/TI1/TCLR1, P46/INTP11/TO1P46/INTP03/TO1 .. | 32 |

| 10.7. P30/SI1/RXD0 .....                                                                          | 33 |

| 10.8. P31/SO1/TXD0 .....                                                                          | 33 |

| 10.9. P32/SCK1- .....                                                                             | 33 |

| 10.10. P20/SI4 .....                                                                              | 34 |

| 10.11. P40/SI0, P41/SO0/SDA, P42/SCK0-/SCL .....                                                  | 34 |

| 10.12. その他の信号 .....                                                                               | 34 |

| 11. GBUS 個別仕様 .....                                                                               | 35 |

|                                   |           |

|-----------------------------------|-----------|

| 11.1. 概要                          | 35        |

| 11.2. バス・サイクル                     | 36        |

| 11.3. チップセレクト                     | 37        |

| 11.4. RTE-MB-A の初期設定              | 37        |

| <b>12. APPENDIXA MULTI モニタ</b>    | <b>38</b> |

| 12.1. ボードの設置                      | 38        |

| 12.1.1. RTE for Win32 のインストール     | 38        |

| 12.1.2. SW1 の設定                   | 38        |

| 12.1.3. ボードの接続                    | 38        |

| 12.2. Multi モニタ                   | 39        |

| 12.2.1. 起動時の 7Seg-LED             | 39        |

| 12.2.2. ROM モニタ・ワーク RAM           | 39        |

| 12.2.3. モニタ割り込み                   | 39        |

| 12.2.4. _INIT_SP の設定              | 39        |

| 12.2.5. タイマ割り込み                   | 39        |

| 12.2.6. ハードウェアの初期化                | 39        |

| 12.2.7. 特殊命令                      | 39        |

| 12.3. RTE コマンド                    | 40        |

| 12.3.1. HELP(?)                   | 40        |

| 12.3.2. INIT                      | 40        |

| 12.3.3. VER                       | 40        |

| 12.3.4. SFR コマンド                  | 40        |

| <b>13. APPENDIX.B PARTNER モニタ</b> | <b>41</b> |

| 13.1. ボードの設置                      | 41        |

| 13.1.1. SW1 の設定                   | 41        |

| 13.1.2. ボードの接続                    | 41        |

| 13.2. PARTNER モニタ                 | 42        |

| 13.2.1. 起動時の 7Seg-LED             | 42        |

| 13.2.2. ROM モニタ・ワーク RAM           | 42        |

| 13.2.3. モニタ割り込み                   | 42        |

| 13.2.4. SP の設定                    | 42        |

| 13.2.5. ハードウェアの初期化                | 42        |

| 13.2.6. 特殊命令                      | 42        |

| <b>14. APPENDIX.C GBUS 共通仕様</b>   | <b>43</b> |

| 14.1. 用語                          | 43        |

| 14.1.1. CPU ボードとマザー・ボード           | 43        |

| 14.1.2. バス・サイクル、マイクロ・サイクル         | 43        |

| 14.2. 信号                          | 43        |

| 14.3. ピン配置                        | 47        |

| 14.4. 未使用端子の処理                    | 48        |

| 14.5. GCS-[7:0]の割り付け              | 48        |

---

|                         |    |

|-------------------------|----|

| 14.6. バス・サイクル .....     | 49 |

| 14.6.1. シングル・サイクル.....  | 49 |

| 14.6.2. パースト・サイクル.....  | 49 |

| 14.6.3. GWAITI-.....    | 50 |

| 14.6.4. GBTERM-.....    | 51 |

| 14.7. タイミング .....       | 52 |

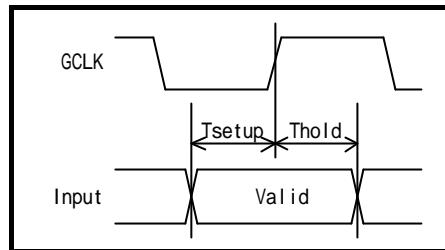

| 14.7.1. セットアップ・タイム..... | 52 |

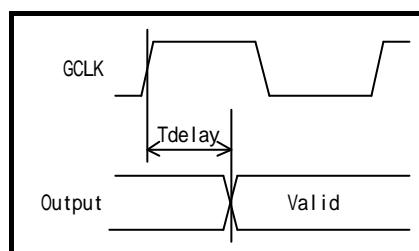

| 14.7.2. ディレイ・タイム.....   | 52 |

## 1. はじめに

「RTE-V850ES/SA3-CB」は、NEC 製の RISC プロセッサ V850ES/SA3 の評価を目的とした CPU ボードです。

ボードは、最高 17MHz で動作する V850ES/SA3 とメモリ、シリアル・インターフェース、USB、LAN、拡張用のバスコネクタ等で構成されます。

これらの機能を使用して、プロセッサの性能評価、デモ、シミュレータの実行エンジン、アプリケーション・プログラムの初期段階の開発など、幅広くご利用頂けます。

本製品は、開発用のソフトウェアツールとして、GHS 社の Multi と自社製の PARTNER のどちらかをソースレベルデバッガとしてご使用になれます。ご使用になるデバッガによって、ROM に搭載するモニタは異なります。

ROM は、購入時にご指定頂いたモニタが搭載されています。デバッガを同時に購入されていない場合は、それぞれ別売りされていますので、別途お買い求めください。

### 1.1. マニュアル表記について

本書では、数字の表記については下表の表記を用います。16 進数や 2 進数の表記では、桁数が多くて読みにくい場合は、4 桁ごとに“-”（ハイフン）を入れてあります。

| 進数    | 表記規則           | 例                      |

|-------|----------------|------------------------|

| 10 進数 | 数字のみを示します      | “10”は 10 進数の“10”を示します  |

| 16 進数 | 数字の末尾に“H”を記します | “10H”は 10 進数の“16”を示します |

| 2 進数  | 数字の末尾に“B”を記します | “10B”は 10 進数の“2”を示します  |

数字表記規則

## 2. 機能

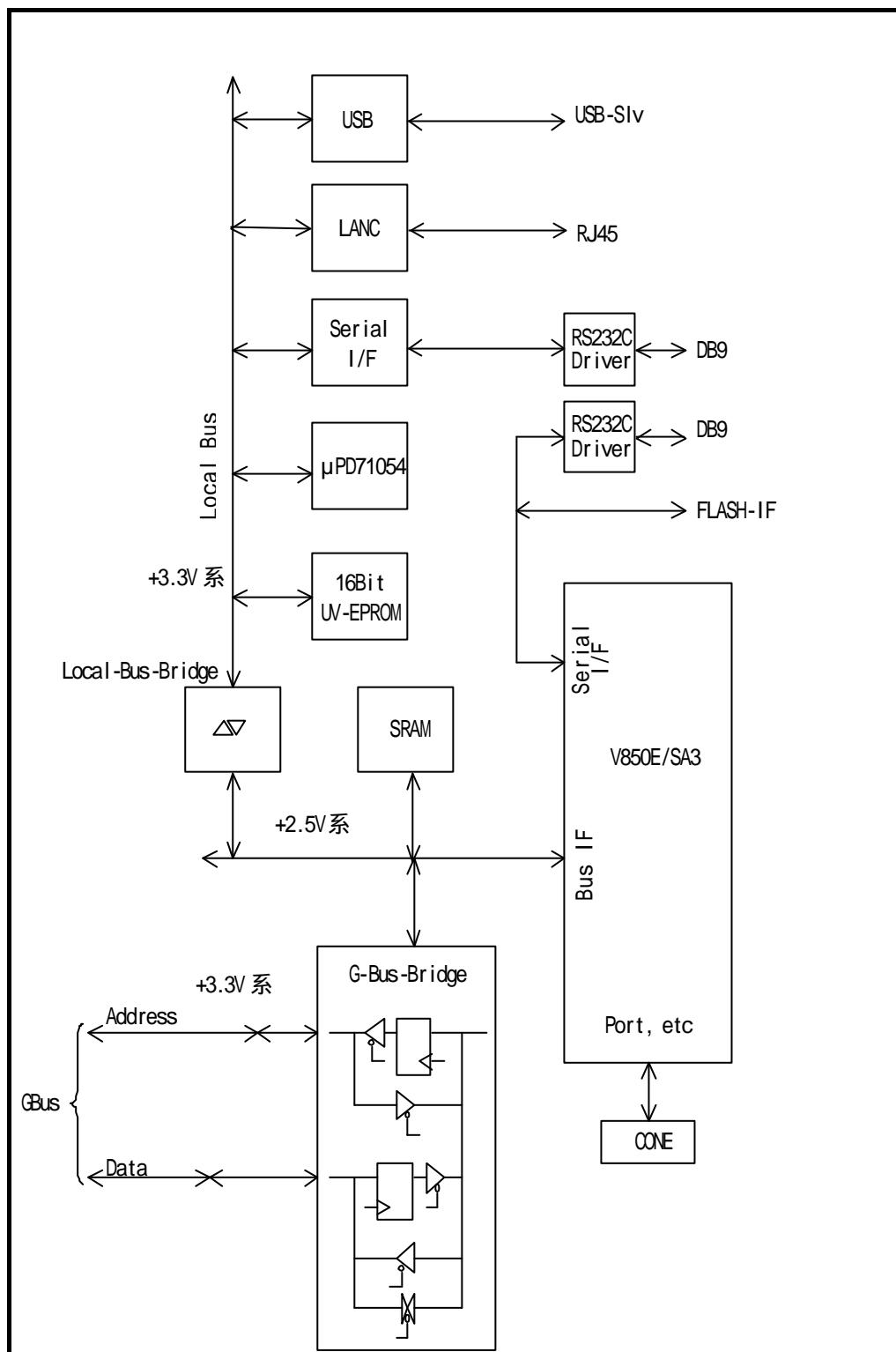

RTE-V850ES/SA3-CB の機能ブロックの概要を図に示します。

RTE-V850ES/SA3-CB ブロック図

### 3. 主な特徴

- GreenHills 社の Multi と自社製 PARTNER 用のモニタ ROM を 2 種類用意しています。

- Multi また PARTNER を使用した高級言語レベルでのリアルタイム実行・評価が可能です。

- ROM エミュレータが接続できます。

- 外部バス上に 3M-Byte の SRAM を搭載しています。

- シリアル(2ch)のインターフェースを用意しています ( 1ch は外部コントローラ、もう 1ch は CPU 内蔵のコントローラ )。

- タイマを外部に 3ch を搭載しています ( モニタで 1ch 使用 )

- USB のコントローラを搭載しています。

- LAN コントローラを搭載しています。

### 4. 基本仕様

|             |                                      |                                        |  |  |  |

|-------------|--------------------------------------|----------------------------------------|--|--|--|

| プロセッサ       | V850ES/SA3                           |                                        |  |  |  |

| CPU クロック    | 17MHz                                |                                        |  |  |  |

| バスクロック      | 17MHz                                |                                        |  |  |  |

| 電源          | +5V , 1.0A(max)                      |                                        |  |  |  |

| メモリ         |                                      |                                        |  |  |  |

| EPROM       | 128KB                                | 64K × 16bit (40pin-DIP) × 1(max.512KB) |  |  |  |

| SRAM        | 3MB                                  | 512K × 16bit × 3                       |  |  |  |

| I/O         |                                      |                                        |  |  |  |

| シリアル(2ch)   | CPU 内蔵(Uart)                         | DB9 コネクタ                               |  |  |  |

|             | NS16550 相当                           | DB9 コネクタ                               |  |  |  |

| USB         | Oki:ML60852                          |                                        |  |  |  |

| LAN         | Smsc:LAN91C111                       |                                        |  |  |  |

| タイマ         | uPD71054                             | 分解能 500nS                              |  |  |  |

| IO ポート      | LED(7seg)表示 / スイッチ入力                 |                                        |  |  |  |

| その他         |                                      |                                        |  |  |  |

| テストコネクタ     | バス等の信号を観測する為のロジアナ用のコネクタ              |                                        |  |  |  |

| GBUS コネクタ   | RTE-CB 標準 32bit I/F(33MHz, DMA は非対応) |                                        |  |  |  |

| FLASH IF    | FLASH Writer 接続用インターフェース             |                                        |  |  |  |

| GP ヘッダ      | CPU の未使用ピンを開放するためのコネクタ               |                                        |  |  |  |

| ROM-Emlt-IF | ROM エミュレータ制御信号接続用テストピン               |                                        |  |  |  |

| リセット・スイッチ   | Push 式                               |                                        |  |  |  |

## 5. ボードの構成

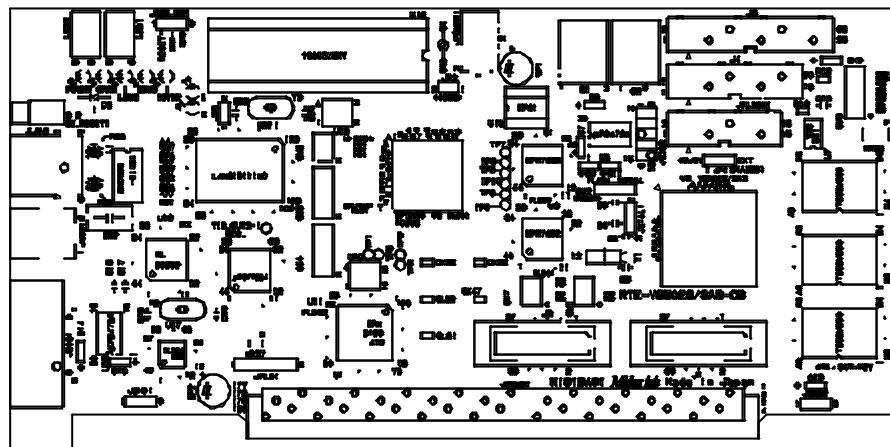

下図は RTE-V850ES/SA3-CB ボード上の主要な部品の物理的な配置です。本章では、それぞれの部品について説明します。

RTE-V850ES/SA3-CB の部品配置図(PRELIMINARY)

### 5.1. リセット・スイッチ (SW\_RESET)

SW\_RESET は本ボード全体のリセット・スイッチです。このスイッチを押すと CPU を含む全ての回路がリセットされます。

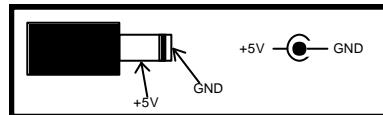

### 5.2. 電源コネクタ (JPOWER)

JPOWER コネクタに供給する電源は、以下の通りです。

電圧 : 5V

電流 : 1.0A(max)

適合コネクタ : Type A ( 5.5 )

極性 :

**電源コネクタの極性に十分ご注意ください。**

また、JGBUS コネクタから電源を供給する場合は、JPOWER に電源を接続しないでください。

### 5.3. スイッチ 1 (SW1)

SW1 は、汎用の入力ポートのスイッチです。設定状態は、入力ポートから読み出すことが可能ですが（「7.4.2 SW1 読出しポート(SW1\_680000H [Read Only])」参照）。ポートからの読み出し時、スイッチは OFF で 1、ON で 0 の値になります。モニタ ROM を使用する場合には、一部を除き割り当て済みです。モニタ ROM での割り付けは、以下の各章を参照し使用環境に合わせて設定してご使用ください。

Multi を使用する場合、「12.1.2 SW1 の設定」を参照ください。

PARTNER を使用する場合、「13.1.1 SW1 の設定」を参照ください。

#### 5.4. スイッチ 2 (SW2)

SW2 は、本ボードの動作をハード的に切り替えるスイッチです。設定内容は入力ポートから読み出すことが可能ですが（「7.4.3 SW2 読出しポート(SW2\_680100H [Read Only])」を参照）。

| 番号 | 信号名       | 出荷時の設定 | 機能                                                                                                                                                       |

|----|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | FBOOT     | OFF    | 0x400000-0x4ffff の空間に割り付ける資源を設定します。<br>OFF : UV-EPROM が割り付けられます。<br>ON : GCS1-空間(MB 上では FLASH ROM)が割り付けられます。（「7.1 メモリ・I/O のマップ」参照）。<br><注意> BOOT はできません。 |

| 2  | DIS_TOVER | OFF    | 通常、OFF でご使用ください。                                                                                                                                         |

| 3  | JMP_20000 | OFF    | 起動時のジャンプ先アドレスを設定します。<br>JMP_40000 JMP_20000<br>OFF OFF MULTI のモニタへジャンプ<br>OFF ON 0x020000 番地へジャンプ<br>ON OFF 0x400000 番地へジャンプ<br>ON ON Partner のモニタへジャンプ  |

| 4  | JMP_40000 | OFF    |                                                                                                                                                          |

| 5  | MON_INTP0 | OFF    | モニタが使用する割り込みを設定します。<br>OFF: NMI<br>ON: INTP0                                                                                                             |

| 6  | GCLK_LOW  | OFF    | 通常、常に OFF でご使用ください。                                                                                                                                      |

| 7  | 未使用       | OFF    | 未使用です。常に OFF でご使用ください。                                                                                                                                   |

| 8  | 未使用       | OFF    | 未使用です。常に OFF でご使用ください。                                                                                                                                   |

SW2-5 は、モニタで割り込みコントローラの設定のために読み出しているだけです。

#### 5.5. スイッチ 3 (SW3)

SW3 は CPU のモード設定用のスイッチです。Normal Mode と Flash Prog Mode 以外の設定は禁止です。

| 番号 | CPU 端子名 | Normal Mode<br>(Auto) | Flash Prog Mode<br>(Manual) |

|----|---------|-----------------------|-----------------------------|

| 1  | MODE0   | OFF                   | OFF                         |

| 2  | MODE1   | OFF                   | OFF                         |

| 3  | MODE2   | OFF                   | OFF                         |

| 4  | MODE3   | OFF                   | OFF                         |

| 5  | MODE4   | OFF                   | OFF                         |

| 6  | MODE5   | ON                    | ON                          |

| 7  | FLMD0   | OFF                   | ON                          |

| 8  | MDEN    | ON                    | ON                          |

Normal Mode(Auto)

: 通常使用時の設定です。（出荷時の設定）

FLMD0 を制御しているライタを使用する場合は、内蔵のフラッシュ ROM に書き込みを行う場合もこのままの設定で構いません。

Flash Prog Mode(Manual)

: FLMD0 を制御していないライタを使用して、内蔵のフラッシュ ROM に書き込みを行う場合の設定です。

注意：モニタ ROM を使用する場合は、出荷時の設定でご使用ください。

### 5.6. スイッチ 4, 5 ( SW4, SW5 )

SW4, SW5 は、CPU の端子に接続している本基板内の信号線を物理的にカットするためのスイッチです。出荷時全ての設定は、ON (接続された状態) になっています。外部で使用する場合にのみ、OFF に設定してください。但し、内部で使用している資源が不要な場合に限ります。

備考：以下の表は、CPU 端子と最終的な内部の資源名を記述しています。

[SW4]

| 番号 | CPU 端子名      | 出荷時の設定 | 内部で使用している資源 |

|----|--------------|--------|-------------|

| 1  | P30/SI1/RXD0 | ON     | SIO2-RXD-   |

| 2  | P20/SI4      | ON     | SIO2-DTS-   |

| 3  | 未使用          | OFF    |             |

| 4  | 未使用          | OFF    |             |

[SW5]

| 番号 | CPU 端子名              | 出荷時の設定 | 内部で使用している資源                    |

|----|----------------------|--------|--------------------------------|

| 1  | P43/INTP00/Ti0/TCLR0 | ON     | TIC_OUT1- : Timer CH#1 の出力     |

| 2  | P44/INTP01/TO0       | ON     | GINT1- : GBUS の割り込み要求信号 GINT1- |

| 3  | P45/INTP10/Ti1/TCLR1 | ON     | GINT2- : GBUS の割り込み要求信号 GINT2- |

| 4  | P46/INTP11/TO1       | ON     | GINT3- : GBUS の割り込み要求信号 GINT3- |

### 5.7. スイッチ 6 ( SW6 )

SW6 は CPU へ接続する RESET 信号の切替用のスライドスイッチです。

NORMAL 側 : 通常使用時の設定です。CPU のリセット端子にはボード上のリセットとフラッシュ・ライタからのリセットを論理和したリセットが接続されます。

(出荷時の設定)

FLASH 側 : CPU のリセット端子にはフラッシュ・ライタからだけのリセットが接続されます。特別な場合を除き、設定の必要はありません。

### 5.8. スイッチ 7 ( SW7 )

SW7 は、出荷時の状態でご使用ください。

| 番号 | CPU 端子名   | 出荷時の設定 | 備考                  |

|----|-----------|--------|---------------------|

| 1  | ISO0      | ON     | 出荷時の設定から変更しないでください。 |

| 2  | ISO1      | ON     | 出荷時の設定から変更しないでください。 |

| 3  | ISO2      | ON     | 出荷時の設定から変更しないでください。 |

| 4  | NO EEPROM | OFF    | 出荷時の設定から変更しないでください。 |

### 5.9. 7SEG-LED, xxx-LED

LED は、各種ステータスを示しています。表に内容を示します。2 つの 7SEG-LED は、起動時にモニタが使用しますが、その後、ユーザーアプリケーションで自由に使用可能です。

| 名称    | 内容                                                                                                              |

|-------|-----------------------------------------------------------------------------------------------------------------|

| POWER | ボードに電源が供給されている時に点灯                                                                                              |

| TOVER | タイムオーバー・レディー発生時に点灯、ソフト的にクリアするまで点灯する（「7.4.5 タイムオーバー・レディーLED クリア・パルス (TOVRDY_LED_CLRPLS 680300H [Write Only])」参照） |

| SRAM  | ボード上の SRAM 空間へのアクセス時に点灯します。                                                                                     |

| LBUS  | ボード上のローカルバス空間へのアクセス時に点灯します。                                                                                     |

| GBUS  | GBUS 空間へのアクセス時に点灯します。                                                                                           |

| A     | LAN91C111 の LEDA 端子(24pin)がローレベルで点灯します。                                                                         |

| B     | LAN91C111 の LEDB 端子(25pin)がローレベルで点灯します。                                                                         |

ボード LED ステータス

### 5.10. ROM エミュレータ用テストピン (JROM-EM1)

JROM-EM1 は、ROM エミュレータを接続する際に使用するテストピンです。下記の制御信号が入力できます。表に信号名と機能を示します。

| 信号名       | 入出力   | 機能                                                                                                                          |

|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| RESET-(1) | 入力    | Low レベル入力により、CPU がリセットされます。<br>ROM エミュレータからのリセット要求信号を接続します。<br>1K でプルアップされています。                                             |

| NMI-(2)   | 入力    | Low レベル入力により、CPU に NMI が入ります ( 10.4P00/NMI, P01/INTP0/TI2 を参照ください。 )。<br>ROM エミュレータからの NMI 要求信号を接続できます。<br>1K でプルアップされています。 |

| GND(3)    | - - - | GND。 ROM エミュレータの GND と接続します。                                                                                                |

JROM\_EM 端子の機能

### 5.11. クリスタル・ソケット (JXTAL1)

JXTAL1 は、CPU に供給するクロックの切り替えとクリスタルの実装ソケットの役割を持っています。

#### フラッシュ・ライタからのクロックを CPU のクロックとして使用する場合

JXTAL1 の 1pin と 2pin をショートします。この場合、クリスタルは実装しないでください。

#### JXTAL1 にクリスタルを実装し、CPU の発振回路を使用する場合

JXTAL1 の 1pin と 3pin の間にクリスタルを実装します。1pin、2pin 間はショートしないでください。出荷時は 17MHz のクリスタルが実装されています。

### 5.12. AVDD 切り替えジャンパ (JP1)

JP1 は、CPU に供給する AD 用の電源(AVDD)を切り替えるためのジャンパです。

#### ボードから供給する場合：出荷時の状態

JP1 の 1pin と 2pin をショートします。+2.5V を供給します。

#### 外部(J3)から供給する場合

JP1 の 2pin と 3pin をショートし、電源を J3 コネクタ-19 ピンから供給してください。

### 5.13. LAN91C111:LINK 端子の設定ジャンパ (JP3)

JP3 は、LAN91C111 の LINK-端子(22)の状態を切り替えるためのジャンパです。

ショートすることで GND レベルに設定されます。

### 5.14. ROM ソケット(U16)と設定ジャンパ(JP2)

ROM ソケットには、27C1024, 27C2048, 27C4096 タイプ (40pin-DIP の 16bit バスの EPROM) が実装できます。ROM を実装する場合は、アクセス・タイムが 120ns 以下のものをご使用ください。

出荷時このソケットには、27C1024 がブランク状態で実装されます。

JP2 は ROM の種類によって以下の通り設定してください。

27C4096 を実装時 : JP2 をショートしてください。

それ以外 : オープンです。

### 5.15. フラッシュ書き込みコネクタ (JFLASH1)

JFLASH1 コネクタは、フラッシュプログラム装置を使用して、CPU の内蔵フラッシュ ROM へ書き込みを行うときに使用するコネクタです。

JFLASH1 を使用する場合は、ライタや使用するモードによって、SW3, JXTAL1 の設定が必要です

(「5.5 スイッチ 3 (SW3)」, 5.11 クリスタル・ソケット(JXTAL1)」参照)

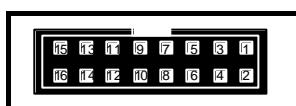

JFLASH ピン配置

#### 適合コネクタ :

16 ピンケーブル用 : オムロン株式会社 XG4M-1630-T 相当品可

16 ピン基板用 : オムロン株式会社 XG4C-1631/1634 相当品

| JFLASH<br>ピン番号 | ライタ信号名   | 基板上の接続先    | 入出力 | 備考              |

|----------------|----------|------------|-----|-----------------|

| 1              | GND      | GND        | --  |                 |

| 2              | /RESET   | CPU_RESET- | IN  | SW6 の設定が必要です。   |

| 3              | SI/RxD   | CPU_P41    | IN  |                 |

| 4              | VDD      | +2.5V      | --  |                 |

| 5              | SO/TxD   | CPU_P40    | OUT |                 |

| 6              | (VPP)    | N.C.       | --  |                 |

| 7              | SCK      | CPU_P42    | IN  |                 |

| 8              | H/S      | CPU_PDH0   | OUT |                 |

| 9              | CLK      | CPU_X1     | IN  | JXTAL の設定が必要です。 |

| 10             | (VDE)    | N.C.       | --  |                 |

| 11             | (VDD2)   | N.C.       | --  |                 |

| 12             | (FLMD1)  | N.C.       | --  |                 |

| 13             | (RFU)    | N.C.       | --  |                 |

| 14             | FLMD0    | CPU_FLMD0  | IN  |                 |

| 15             | Not Used | N.C.       | --  |                 |

| 16             | Not Used | N.C.       | --  |                 |

JFLASH1 コネクタ信号

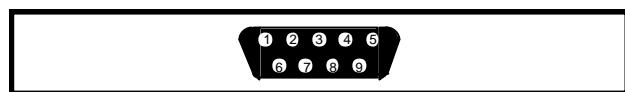

### 5.16. シリアル・コネクタ ( JSIO1,JSIO2 )

JSIO1 コネクタは、ボード上のシリアル・コントローラ ( TL16C550CPT ) によって制御される RS-232C インターフェース用のコネクタです。

JSIO2 コネクタは、CPU の内蔵シリアル・コントローラによって制御される RS-232C インターフェース用のコネクタです。

コネクタの形状は、JSIO1 は PC/AT で用いられる一般的な D-SUB9 ピンの RS-232C コネクタ、JSIO2 は 2.54mm ピッチのピンプラグ型のコネクタです。何れも、全ての信号は RS-232C レベルに変換されています。コネクタのピン番号と信号アサインは下の図と表の通りです。

表には、ホストと接続する場合の接続信号について、ホスト側が D-SUB9 ピンの場合と D-SUB25 ピンの場合の布線をそれぞれ示してあります（一般的なクロスケーブルの布線です）。

また JSIO2 のピン配置は、リボンケーブルに対して圧接型コネクタを使用した場合、JSIO1 のピン配置と同じになるようになっています。

JSIO1 ピン配置（オス）

JSIO2 ピン配置

#### 適合コネクタ：

|             |          |             |      |

|-------------|----------|-------------|------|

| 10 ピンケーブル用： | オムロン株式会社 | XG4M-1030-T | 相当品可 |

| 10 ピン基板用：   | オムロン株式会社 | XG8W-1031   | 相当品  |

| JSIO1<br>ピン番号 | 信号名     | 入出力 | ホストの接続ピン番号 |         |

|---------------|---------|-----|------------|---------|

|               |         |     | D-SUB9     | D-SUB25 |

| 1             | DCD     | 入力  |            |         |

| 2             | RxD(RD) | 入力  | 3          | 2       |

| 3             | TxD(SD) | 出力  | 2          | 3       |

| 4             | DTR(DR) | 出力  | 1, 6       | 6, 8    |

| 5             | GND     |     | 5          | 7       |

| 6             | DSR(ER) | 入力  | 4          | 20      |

| 7             | RTS(RS) | 出力  | 8          | 5       |

| 8             | CTS(CS) | 入力  | 7          | 4       |

| 9             | RI      | 入力  |            |         |

JSIO1 コネクタ信号

| JSIO2<br>ピン番号 | CPU<br>端子 | 信号名     | 入出力 | ホストの接続ピン番号 |         |

|---------------|-----------|---------|-----|------------|---------|

|               |           |         |     | D-SUB9     | D-SUB25 |

| 1             | --        | DCD     | 入力  |            |         |

| 3             | P30       | RxD(RD) | 入力  | 3          | 2       |

| 5             | P31       | TxD(SD) | 出力  | 2          | 3       |

| 7             | --        | DTR(DR) | 出力  | 1, 6       | 6, 8    |

| 9             |           | GND     |     | 5          | 7       |

| 2             | --        | DSR(ER) | 入力  | 4          | 20      |

| 4             | P32       | RTS(RS) | 出力  | 8          | 5       |

| 6             | P20       | CTS(CS) | 入力  | 7          | 4       |

| 8             | --        | RI      | 入力  |            |         |

JSIO2 コネクタ信号

**注意事項 :**

- 1 . JSIO2 の 1, 2, 8, 10 ピンは、ボード内で使用されていません。

- 2 . 7 ピン(DTR)は、通電することで常時アクティブです。

**5.17. USB コネクタ ( JUSB1 )**

JUSB1 コネクタは、本ボードに搭載している USB デバイスコントローラのインターフェース用でシリーズB のコネクタです。

| JUSB1<br>ピン番号 | 信号名   |

|---------------|-------|

| 1             | VCC   |

| 2             | -DATA |

| 3             | +DATA |

| 4             | GND   |

JUSB1 コネクタ信号

**5.18. LAN コネクタ ( JLAN1 )**

JLAN1 コネクタは、10BaseT 用の RJ45 コネクタです。

| JLAN1<br>ピン番号 | 信号名 | ピン番号 | 信号名 |

|---------------|-----|------|-----|

| A1            | TD+ | A5   | CT2 |

| A2            | TD- | A6   | RD- |

| A3            | RD+ | A7   | CT3 |

| A4            | CT1 | A8   | CT4 |

JLAN1 コネクタ信号

**5.19. JGBUS コネクタ ( JGBUS )**

拡張用の 32Bit データ幅のバスコネクタです。詳細は「 11 GBUS 個別仕様」、「 14 APPENDIX.C GBUS 共通仕様」を参照してください。

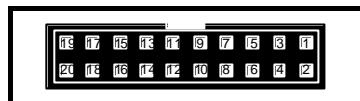

### 5.20. 信号観測用コネクタ(J1, J2)

J1, J2 コネクタは、HP 社の高密度プローブを接続してボード上の信号を観測する為のコネクタです。

| ピン番号 | 信号名     | ピン番号 | 信号名     |

|------|---------|------|---------|

| 1    | NC.     | 2    | NC.     |

| 3    | GND     | 4    | NC.     |

| 5    | CPU_RD  | 6    | NC.     |

| 7    | CPU_A15 | 8    | NC.     |

| 9    | CPU_A14 | 10   | NC.     |

| 11   | CPU_A13 | 12   | NC.     |

| 13   | CPU_A12 | 14   | NC.     |

| 15   | CPU_A11 | 16   | NC.     |

| 17   | CPU_A10 | 18   | NC.     |

| 19   | CPU_A9  | 20   | NC.     |

| 21   | CPU_A8  | 22   | NC.     |

| 23   | CPU_A7  | 24   | CPU_A23 |

| 25   | CPU_A6  | 26   | CPU_A22 |

| 27   | CPU_A5  | 28   | CPU_A21 |

| 29   | CPU_A4  | 30   | CPU_A20 |

| 31   | CPU_A3  | 32   | CPU_A19 |

| 33   | CPU_A2  | 34   | CPU_A18 |

| 35   | CPU_A1  | 36   | CPU_A17 |

| 37   | CPU_A0  | 38   | CPU_A16 |

J1 コネクタ信号

| ピン番号 | 信号名      | ピン番号 | 信号名       |

|------|----------|------|-----------|

| 1    | NC.      | 2    | NC.       |

| 3    | GND      | 4    | NC.       |

| 5    | CPU_WR0- | 6    | CPU_WR1   |

| 7    | CPU_D15  | 8    | GREADY-   |

| 9    | CPU_D14  | 10   | GW/R-     |

| 11   | CPU_D13  | 12   | GADS-     |

| 13   | CPU_D12  | 14   | GCLK      |

| 15   | CPU_D11  | 16   | CPU_NMI-  |

| 17   | CPU_D10  | 18   | LBUS_DEN- |

| 19   | CPU_D9   | 20   | LBUS_DTR  |

| 21   | CPU_D8   | 22   | ROM_CS-   |

| 23   | CPU_D7   | 24   | LED_GBUS- |

| 25   | CPU_D6   | 26   | LED_LBUS- |

| 27   | CPU_D5   | 28   | LED_SRAM- |

| 29   | CPU_D4   | 30   | CPU_READY |

| 31   | CPU_D3   | 32   | CPU_WR1-  |

| 33   | CPU_D2   | 34   | CPU_WR0-  |

| 35   | CPU_D1   | 36   | CPU_RD-   |

| 37   | CPU_D0   | 38   | CPU_BCLK  |

J2 コネクタ信号

NC : 基板側で未接続です。

#### 適合コネクタ :

ケーブル側 : AMP 社 MICTOR38 プラグ

基板用 : AMP 社 MICTOR38 レセプタクル 2-767004-2

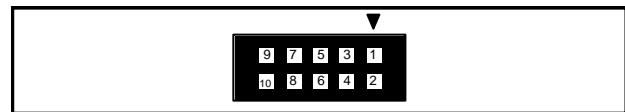

### 5.21. CPU 信号コネクタ (J3, J4)

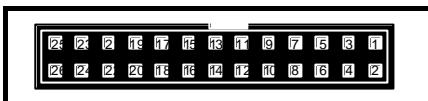

J3, J4 コネクタは、外部から CPU に信号を直接接続するためのコネクタです。コネクタの形状は、2.54mm ピッチのピンプラグ型のコネクタです。コネクタのピン番号と信号アサインは下の図と表の通りです。

J3 ピン配置

#### 適合コネクタ：

- |             |                             |

|-------------|-----------------------------|

| 20 ピンケーブル用： | オムロン株式会社 XG4M-2030-T 相当品可   |

| 20 ピン基板用：   | オムロン株式会社 XG4C-2031/2034 相当品 |

J4 ピン配置

#### 適合コネクタ：

- |             |                             |

|-------------|-----------------------------|

| 26 ピンケーブル用： | オムロン株式会社 XG4M-2630-T 相当品可   |

| 26 ピン基板用：   | オムロン株式会社 XG4C-2631/2634 相当品 |

| ピン番号 | 信号名         | ピン番号 | 信号名       |

|------|-------------|------|-----------|

| 1    | CPU_ANI0    | 2    | CPU_ANI1  |

| 3    | CPU_ANI2    | 4    | CPU_ANI3  |

| 5    | CPU_ANI4    | 6    | CPU_ANI5  |

| 7    | CPU_ANI6    | 8    | CPU_ANI7  |

| 9    | CPU_ANI8    | 10   | CPU_ANI9  |

| 11   | CPU_ANI10   | 12   | CPU_ANI11 |

| 13   | CPU_ANI12   | 14   | CPU_ANI13 |

| 15   | CPU_ANI14   | 16   | CPU_ANI15 |

| 17   | CPU_ANO0    | 18   | CPU_ANO1  |

| 19   | AVDD(JP1-3) | 20   | AVREF0    |

| 21   | AVREF1      | 22   | AVSS(GND) |

| 23   | N.C.        | 24   | N.C.      |

| 25   | GND         | 26   | GND       |

J3 コネクタ信号

| ピン番号 | 信号名      | ピン番号 | 信号名          |

|------|----------|------|--------------|

| 1    | CPU_P20  | 2    | CPU_P21      |

| 3    | CPU_P22  | 4    | CPU_P30      |

| 5    | CPU_P31  | 6    | CPU_P32      |

| 7    | CPU_PCD1 | 8    | CPU_PCD2     |

| 9    | CPU_PCD3 | 10   | CPU_PCS0     |

| 11   | CPU_PCS1 | 12   | CPU_PCS2     |

| 13   | CPU_PCS3 | 14   | CPU_PCS4     |

| 15   | CPU_PCS5 | 16   | CPU_PCS6     |

| 17   | CPU_PCS7 | 18   | Internal Use |

| 19   | GND      | 20   | GND          |

J4 コネクタ信号

以下の信号はボード内部で使用されていますので、外部と信号を接続する場合はボード内部で使用している機能は使用できなくなります。また、SW4による信号の切り離しも必要です。

(「5.16 シリアル・コネクタ (JSIO1,JSIO2)」参照)

ボード内部で使用している信号 : P20, P30 -P32

## 6. ホスト PC との接続

### 6.1. RS-232C 接続

モニタ ROM を使用して、ホストマシンとシリアルで接続する際の手順は以下の通りです。

添付品の RS-232C ケーブルと、電源を用意してください。

ボード上のスイッチの設定と確認を行ってください。SW1 のボーレイトの設定は、必ず実施ください。(「12.1.2 SW1 の設定」、「13.1.1 SW1 の設定」の各項を参照ください。)

JSIO1 コネクタとホストマシンを RS-232C ケーブルで接続し、JPOWER コネクタへ電源を供給してください。ボードの POWER-LED が点灯し、モニタの起動を示す 7seg-LED の表示がなされることを確認してください。

LED が点灯しない場合は、すぐに電源を切り接続を確認してください。

ホストマシンでデバッガを起動し、RS-232C 経由でコネクトします。エラーが発生する場合には、シリアル・ケーブルやスイッチ（特にボーレート）の設定等に間違いがないかを確認してください。デバッガの起動方法や手順は、各デバッガのマニュアルを参照ください。

ボードは絶縁物の上に設置してください。通電中に、導電物を基板に接触させると故障の原因になります。

## 7. ハードウェア・リファレンス

ここでは、RTE-V850ES/SA3-CB ボードのハードウェアについて記述します。

### 7.1. メモリ・I/O のマップ

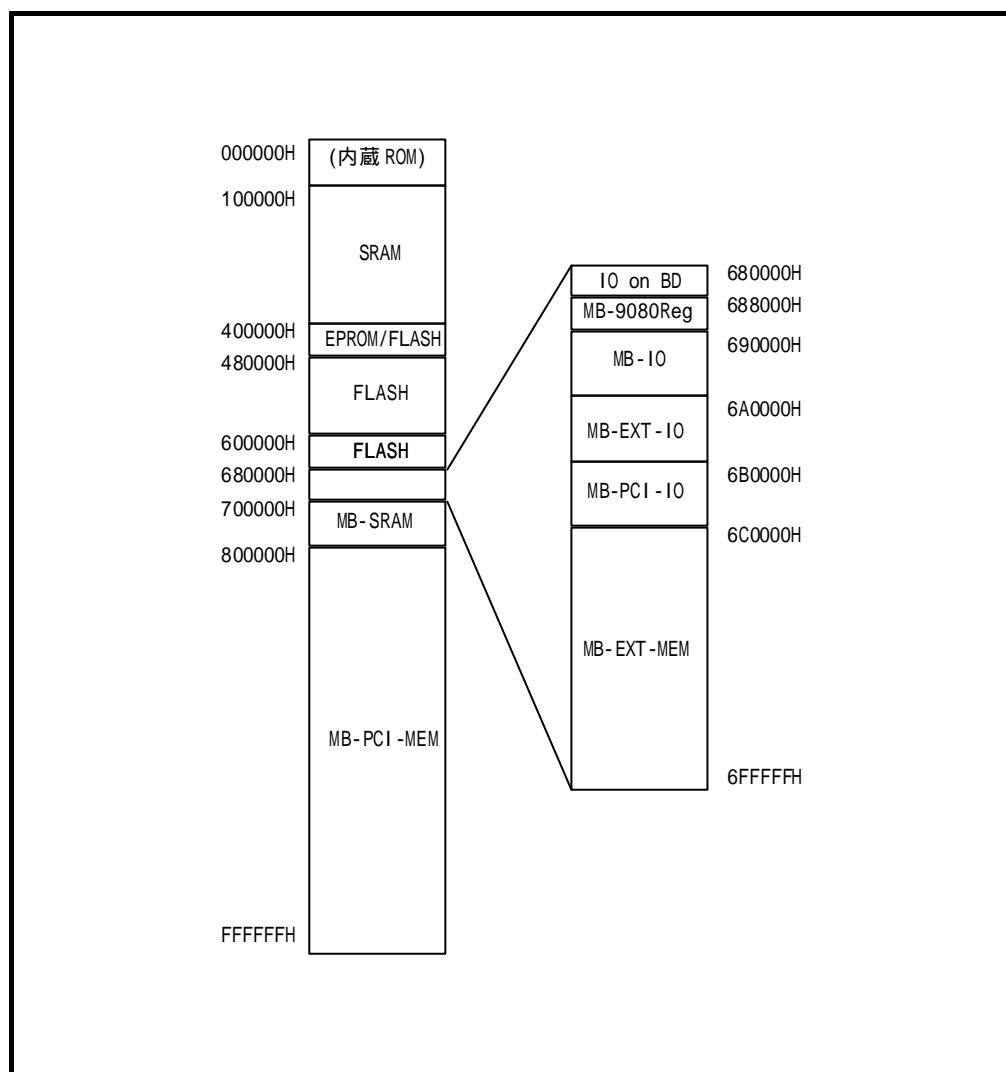

外部バス上のメモリと I/O の割り付けを以下に示します。

メモリ・I/O マップ

**内蔵 ROM:** 0000000 - 003FFFFF(256K-byte)

CPU が内蔵している ROM です。前半の 128K-byte にモニタが書き込まれた状態で出荷されます。

**SRAM:** 0100000 - 03FFFFFF(3M-byte)

オンボード上の SRAM が割り付けられています。実容量は 3M バイトです。モニタを使用する場合、0x0100000-0x0107fff(32K-Byte)はモニタのワークとして予約されます。

**EPROM, FLASH(GCS1):** 0400000 - 047FFFFF(512K-byte)

UV-EPROM またはマザー・ボード上のフラッシュのボトム側 512K バイトが割り付けられます。切り替えは SW2-1:FBOOT(5.4.スイッチ 2 (SW2) 参照)で行います。この空間のフラッシュは 0600000 - 067FFFFF でアクセスする領域と同じ領域です。

**FLASH(GCS1):** 0480000 - 05FFFFFF(1.5M-byte)

マザー・ボード上のフラッシュのボトム側 512K バイトより後ろの領域が割り付けられます。

**FLASH(GCS1):** 0600000 - 067FFFFF(512K-byte)

マザー・ボード上のフラッシュのボトム側 512K バイトが割り付けられます。

**IO on BD:** 0680000 - 0687FFF(32K-byte)

この空間は、オンボード上の I/O 空間として使用します。

**MB-9080Reg(GCS6):** 0688000 - 068FFFFF(32K-byte)

この空間は、マザー・ボード上の PCI ブリッジの制御レジスタの空間として使用します。

**MB-IO(GCS2):** 0690000 - 069FFFFF(64K-byte)

この空間は、マザー・ボード上の nonPCI の周辺 I/O 空間として使用します。

**MB-EXT-IO(GCS4):** 06A0000 - 06AFFFFF(64K-byte)

この空間は、マザー・ボード上の nonPCI の外部拡張コネクタの IO 空間として使用します。

**MB-PCI-IO(GCS7):** 06B0000 - 06BFFFFF(64K-byte)

この空間は、マザー・ボード上の PCI バスの IO 空間として使用します。

**MB-EXT-MEM(GCS3):** 06C0000 - 06FFFFFF(256K-byte)

この空間は、マザー・ボード上の nonPCI の外部拡張コネクタの MEM 空間として使用します。

**MB-SRAM(GCS0):** 0700000 - 07FFFFFF(1M-byte)

この空間は、マザー・ボード上の共有 RAM 空間として使用します。

**MB-PCI-MEM(GCS5):** 0800000 - 0FFFFFFF(8M-byte)

この空間は、マザー・ボード上の PCI の MEM 空間として使用します。

## 7.2. 推奨設定

ここでは、メモリおよびI/O資源のアクセスに関する各レジスタの推奨設定値を示します。

### 7.2.1. CPU レジスタ

バスに関する設定は、下表のように設定してください

| レジスタ名              | アドレス               | 設定値               | 備考                              |

|--------------------|--------------------|-------------------|---------------------------------|

| BSC                | 0xFFFFF066         | 0x5555            | All 16-bit: CPUの初期値に同じ          |

| VSWC               | 0xFFFFF06E         | 0x00              |                                 |

| DWC0               | 0xFFFFF484         | 0x0000            | CS0-3:0wait                     |

| AWC                | 0xFFFFF488         | 0xFF00            | アドレスウェイ特はなし                     |

| BCC                | 0xFFFFF48A         | 0xAAAA            | アイドルステート挿入                      |

| EXIMC              | 0xFFFFFBEB         | 0x01              | SMSEL=1:セルレートモード                |

| PMC9/<br>PFC9<br>2 | 0xFFFFF452/47<br>2 | 0xFFFF/<br>0x0000 | Port9[15..0]=[A15..0]           |

| PMCCM              | 0xFFFFF04C         | 0x03              | PortCM[1,0]=[CLKOUT, WAIT-]     |

| PMCCCT             | 0xFFFFF04A         | 0x13              | PortCT[4,1,0]=[RD-, WR1-, WR0-] |

| PMCDH              | 0xFFFFF046         | 0xFF              | PortDH[7..0]=[A23..16]          |

| PMCDL              | 0xFFFFF044         | 0xFFFF            | PortDL[15..0]=[D15..0]          |

バス以外の割込みや周辺を使用する場合は、ポートに接続されている信号に合わせ各ポートや周辺コントローラに対し初期化を実施してください。( 10.1端子接続一覧を参照ください )

## 7.3. メモリ詳細

### 7.3.1. SRAM (0100000 - 03FFFF)

SRAM は、512K-Word × 16bit の SRAM を 3 つ実装し、3M バイトの容量を搭載しています。

### 7.3.2. UV-E PROM (0400000 - 047FFFF)

UV-E PROM は、128K バイト ( 64KWord × 16Bit ) 256K バイト ( 128Kword × 16Bit ) 512K バイト ( 256KWord × 16Bit ) のいずれかで、アクセストイムが 120nS 以下の ROM が搭載できます。

## 7.4. IO 詳細

### 7.4.1. IO 一覧

IO の一覧を下表に示します。

| アドレス            | 用途                      |

|-----------------|-------------------------|

| 680000          | SW1                     |

| 680100          | SW2                     |

| 680200          | 7SEGLED                 |

| 680300          | TOVRDY_LED_CLRPLS       |

| 680400 - 680430 | PIC                     |

| 680500          | GBUS ACCESS CONTROL     |

| 680600          | MB-SRAM High ADDR       |

| 680610          | MB-FROM High ADDR       |

| 680620          | MB-EXTBUS-MEM High ADDR |

| 680630          | MB-EXTBUS-IO High ADDR  |

| 680800 - 680870 | UART (TL16C550C)        |

| 680900 - 680930 | TIC (uPD71054)          |

| 681000 -        | USB                     |

| 684000 -        | LANC                    |

### 7.4.2. SW1 読出しポート(SW1 680000H [Read Only])

SW1 の状態を読み出すためのポートです。データ・フォーマットを下表に示します。

| 物理アドレス        | データバス |       |       |       |       |       |       |       | 内容            |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

|               | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |               |

| 680000H<br>入力 | SW1-8 | SW1-7 | SW1-6 | SW1-5 | SW1-4 | SW1-3 | SW1-2 | SW1-1 | 0=ON<br>1=OFF |

SW1-1 が SW1 の”1”のスイッチに、SW1-8 が SW1 の”8”のスイッチに対応し、該当するビットのスイッチが ON で 0 が、OFF で 1 が読み出されます。SW1 は主にモニタの動作設定用のスイッチとして使用しています。

### 7.4.3. SW2 読出しポート(SW2 680100H [Read Only])

SW2 の状態を読み出すためのポートです。データ・フォーマットを下表に示します。

| 物理アドレス        | データバス |       |       |       |       |       |       |       | 内容            |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

|               | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |               |

| 680100H<br>入力 | SW2-8 | SW2-7 | SW2-6 | SW2-5 | SW2-4 | SW2-3 | SW2-2 | SW2-1 | 0=ON<br>1=OFF |

SW2-1 が SW2 の”1”のスイッチに、SW2-8 が SW2 の”8”のスイッチに対応し、該当するビットのスイッチが ON で 0 が、OFF で 1 が読み出されます。SW2 は主にハードウェアの動作を切り替えます。

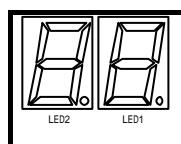

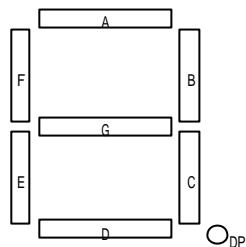

#### 7.4.4. 7セグメント LED表示データ出力ポート(7SEG-LED 680200H [Write Only])

4つの7セグメントLEDに表示するデータを設定します。データ・フォーマットを下表に示します。該当するビットに0を設定すると対応するセグメントが点灯します。

| 論理アドレス        | データ         |            |            |            |            |            |            |            | 内容           |

|---------------|-------------|------------|------------|------------|------------|------------|------------|------------|--------------|

|               | D7/D15      | D6/D14     | D5/D13     | D4/D12     | D3/D11     | D2/D10     | D1/D9      | D0/D8      |              |

| 680200H<br>出力 | LED1<br>-DP | LED1<br>-G | LED1<br>-F | LED1<br>-E | LED1<br>-D | LED1<br>-C | LED1<br>-B | LED1<br>-A | 0=点灯<br>1=消灯 |

| 680201H<br>出力 | LED2<br>-DP | LED2<br>-G | LED2<br>-F | LED2<br>-E | LED2<br>-D | LED2<br>-C | LED2<br>-B | LED2<br>-A | 0=点灯<br>1=消灯 |

7セグメントLEDのビット対応は、下図の通りです。

#### 7.4.5. タイムオーバ・レディーLEDクリア・パルス(TOVRDY\_LED\_CLRPLS 680300H [Write Only])

本ポートに書き込みを行うと、ボード上のタイムオーバ・レディー発生時に点灯する TOV\_RDY LED が消灯します。書き込まれたデータは無視されます。TOV\_RDY LED は一旦点灯すると、本ポートに書き込むか、ボードをリセットするまで点灯し続けます。

#### 7.4.6. 割り込みコントローラ(PIC:680400H - 680430H [Read/Write])

PIC は、Multi および PARTNER のモニタ・プログラムの動作に必要な割り込み(INT0)とユーザが使用できる割り込み(INT1)を各 1 本サポートし、INT0 は CPU の NMI 又は、INTP0 に、INT1 は CPU の INTP4 に接続されます。共にローアクティブの割込み要求信号です。

PIC に入力している割り込みは以下の通りです。

- 1)RS232C デバイス (UART, TL16C550C) からの通信割り込み

- 2)タイマ(TIC, μPD71054)の TOUT0 によるタイマ割り込み要求

- 3)タイムオーバ・レディの発生

- 4)GINT0 の割り込み

- 5)USB コントローラからの割込み

- 6)LANC からの割込み

| 論理アドレス  | レジスタ      | データバス       |      |      |      |      |      |            |            |

|---------|-----------|-------------|------|------|------|------|------|------------|------------|

|         |           | D7          | D6   | D5   | D4   | D3   | D2   | D1         | D0         |

| 680400H | PIC INT0M | IM07        | IM06 | IM05 | IM04 | IM03 | IM02 | IM01       | IM00       |

| 680410H | PIC INT1M | IM17        | IM16 | IM15 | IM14 | IM13 | IM12 | IM11       | IM10       |

| 680420H | PIC INTR  | IR7         | IR6  | IR5  | IR4  | IR3  | IR2  | IR1        | IR0        |

| 680430H | PIC INTEN | INT0<br>SEL | 0    | 0    | 0    | 0    | 0    | INT1<br>EN | INT0<br>EN |

INT0M, INT1M レジスタはそれぞれ INT0, INT1 に入力する割込みをマスクします。IM0x, IM1x の

ビットが”1”の時にイネーブルとなり、複数ビットを選択した場合にはそれぞれの OR で割込みがアクティブとなります。

INTR レジスタは割込みステータスで、割込み要求がある場合に”1”が読み出せます。これはマスク状態に関係ありません。またエッジ割込み要求の解除(クリア)には、このレジスタの対応ビットに”1”を書き込みます。

IM0[0..7],IM1[0..7].IR[0..7]の各ビットに割り付けられている割込み要因は以下の通りです。

| PIC<br>INT-MASK[],STATUS[] | 割り込み要因           | 要求レベル      |

|----------------------------|------------------|------------|

| 0                          | タイマ0(モード2)       | エッジ(立ち上がり) |

| 1                          | シリアル0            | レベル(High)  |

| 2                          | タイムオーバー          | レベル(High)  |

| 3                          | GINT0(from Gbus) | レベル(Low)   |

| 4                          | USB              | レベル(Low)   |

| 5                          | LANC             | レベル(High)  |

| 6                          | なし               |            |

| 7                          | なし               |            |

INTEN レジスタは、INT0,INT1への割込みの有効／禁止を制御します。

**INT0EN:** INT0 を制御します。このビットで INT0 をハード的に禁止することができます。

この時、INT0 端子の状態は High レベルとなります。

| INT0EN | INT0            |

|--------|-----------------|

| 0      | 禁止する<br>(リセット値) |

| 1      | 有効にする           |

**INT1EN:** INT1 を制御します。このビットで INT1 をハード的に禁止することができます。

この時、INT1 端子の状態は High レベルとなります。

INT1 は CPU の P05/INTP4 に接続されます。

| INT1EN | INT1            |

|--------|-----------------|

| 0      | 禁止する<br>(リセット値) |

| 1      | 有効にする           |

INTxEN は複数の割り込み要因が発生している時に、1 つの割り込み処理が終了した時点で、CPU への割り込み要求信号にエッジを生成するために使用します。CPU の割り込み受け付けがエッジ検出の場合、割り込みハンドラの最後のステップで、INTxEN ビットを一旦”1”に設定後、“0”にする処理を実行してください。これによって、保留中の割り込みが入ります。

**INT0SEL:** モニタで使用する割り込みを選択します。

| INT0SEL | モニタ用の割り込み          |

|---------|--------------------|

| 0       | NMI を使用<br>(リセット値) |

| 1       | INTP0 を使用          |

**注意：**モニタを使用中は、INT0 関連の内容は変更しないでください。

#### 7.4.7. GBUS ACCESS CONTROL (680500H[Read/Write])

GBUS に対し、ハーフワード(16-Bit)以外のアクセスサイズでアクセスを行う場合に使用します。

| 論理アドレス  | レジスタ     | データバス |    |    |    |    |    |      |      |

|---------|----------|-------|----|----|----|----|----|------|------|

|         |          | D7    | D6 | D5 | D4 | D3 | D2 | D1   | D0   |

| 680500H | GBUS ACC | x     | x  | x  | x  | x  | x  | Word | Byte |

**Byte:** GBUS に対し BYTE でリードしたい場合に”1”にします。通常は”0”でご使用ください。

V850ES/SA3 のリードサイクルは、命令のアクセスサイズに関係なくハーフワードのアクセスサイズで行われますが、GBUS 上の資源によっては、バイトでのアクセスのみを要求するデバイスがあります。このようなデバイスへのアクセス時、このビットに 1”を立て CPU からはバイトサイズでアクセスしてください。

**Word:** GBUS に対し Word(32-Bit)でアクセスしたい場合に”1”にします。通常は”0”でご使用ください。

V850ES/SA3 の外部バスは 16-Bit ですが、GBUS 上の資源によっては、ワード(32-Bit)でのアクセスを要求するデバイスがあります。このようなデバイスへのアクセス時、このビットに 1”を立て CPU からはワードサイズ(32-Bit)でアクセスしてください。

**注意：**Byte, Word の両方の Bit に”1”を設定しないでください。

**注意：**設定変更後は必ず IOWAIT()(ROM 領域のダミーリード)を行ってください。

#### 7.4.8. MB-SRAM High ADDR (680600H[Read/Write])

MB-SRAM の上位アドレスを指定します。

| 論理アドレス  | レジスタ              | データバス |    |    |     |    |    |    |    |

|---------|-------------------|-------|----|----|-----|----|----|----|----|

|         |                   | D7    | D6 | D5 | D4  | D3 | D2 | D1 | D0 |

| 680600H | MB-SRAM High ADDR | x     | x  | x  | A20 | x  | x  | x  | x  |

#### 7.4.9. MB-FROM High ADDR (680610H[Read/Write])

MB-FROMM の上位アドレスを指定します。

| 論理アドレス  | レジスタ              | データバス |     |     |    |    |    |    |    |

|---------|-------------------|-------|-----|-----|----|----|----|----|----|

|         |                   | D7    | D6  | D5  | D4 | D3 | D2 | D1 | D0 |

| 680610H | MB-FROM High ADDR | x     | A22 | A21 | x  | x  | x  | x  | x  |

#### 7.4.10. MB-EXTBUS-MEM High ADDR (680600H[Read/Write])

MB-EXTBUS-MEM の上位アドレスを指定します。

| 論理アドレス  | レジスタ                    | データバス |     |     |     |     |     |     |     |

|---------|-------------------------|-------|-----|-----|-----|-----|-----|-----|-----|

|         |                         | D7    | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 680600H | MB-EXTBUS-MEM High ADDR | A23   | A22 | A21 | A20 | A19 | A18 | A17 | A16 |

#### 7.4.11. MB-EXTBUS-IO High ADDR (680600H[Read/Write])

MB-EXTBUS-IO の上位アドレスを指定します。

| 論理アドレス  | レジスタ                   | データバス |     |     |     |     |     |     |     |

|---------|------------------------|-------|-----|-----|-----|-----|-----|-----|-----|

|         |                        | D7    | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 680600H | MB-EXTBUS-IO High ADDR | A23   | A22 | A21 | A20 | A19 | A18 | A17 | A16 |

#### 7.4.12. UART (TL16C550C:680800H - 680870H)

UART コントローラとして TEXAS INSTRUMENTS 製の TL16C550C LSI を使用しています。TL16C550C は、UART を 1 チャンネル備えており、UART の送受信部には 16 キャラクタ分の FIFO バッファを持ち、RTS/CTS フローを自動的に制御する機能を備えているため、最小限の割り込みで通信のオーバーラン・エラーを押さえられます。

TL16C550C の各レジスタは、表のように割り付けられています。各レジスタの機能については、TL16C550C のマニュアルを参照してください ( TL16C550C のマニュアルは米国 TEXAS INSTRUMENTS 社のホームページ (<http://www.ti.com/>) の TI&ME のコーナーで入手可能です )。

| アドレス    | 読み出し    | 書き込み    |

|---------|---------|---------|

| 680800H | RBR/DLL | THR/DLL |

| 680810H | IER/DLM | IER/DLM |

| 680820H | IIR     | FCR     |

| 680830H | LCR     | LCR     |

| 680840H | MCR     | MCR     |

| 680850H | LSR     | LSR     |

| 680860H | MSR     | MSR     |

| 680870H | SCR     | SCR     |

TL16C550C レジスタ配置

TL16C550C の XIN 入力には 16MHz のクロックが接続されています。

UART の割り込みは CPU の PIC を通して、CPU の NMI1 に入力できます。

UART はボードの JISO1 コネクタに接続しています。また、UART はリモートデバッガを用いる場合、ホストとの通信に使用されます。

TL16C550C は、システム・リセットによってリセットされます。

**注意：モニタ使用中は、UART の内容は変更しないでください。**

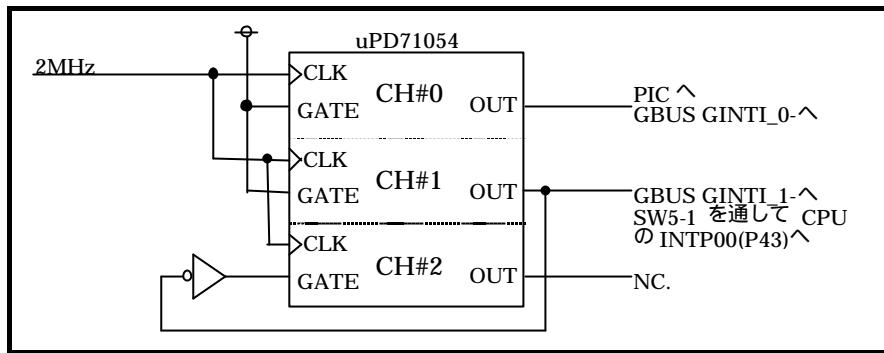

#### 7.4.13. TIC ( uPD71054 680900H ~ 680930FH )

TIC は NEC 社製の uPD71054 が実装されています。uPD71054 は Intel 製の i8254 と互換であり、3 つのタイマ / カウンタを持っています。これらのタイマ / カウンタにより、モニタのタイマ割り込みの生成を行っています。

TIC の各レジスタは、表の通りに割り当てられています。

| アドレス    | 読み出し      | 書き込み         |

|---------|-----------|--------------|

| 680900H | COUNTER#0 | COUNTER#0    |

| 680910H | COUNTER#1 | COUNTER#1    |

| 680920H | COUNTER#2 | COUNTER#2    |

| 680930H | -----     | Control Word |

TIC のレジスタ配置

TIC の各チャンネルは下図のように接続されています。

チャンネル 0 は、Multi の ROM モニタ・プログラムのインターバル・タイマとして使用されます。

チャンネル 1, 2 は、ユーザのプログラムで自由に使用することができます。

チャンネル 2 は、チャンネル 1 とカスケード接続されています。

#### 使用モード例

CH#0 : モード 2 (レートジェネレータ)

CH#1 : モード 2 (レートジェネレータ)

CH#2 : モード 0 (ダウンカウンタ)

**注意：モニタ使用中は、CH#0 の内容は変更しないでください。**

#### 7.4.14. USB (ML60852A:681000H – 6810FEH)

USBC は沖電気社製の ML60852A が実装されています。ML60852A は、Universal Serial Bus (USB) 汎用デバイスコントローラです。USB シリアル・インターフェース・エンジン、USB トランシーバ、FIFO 群、コントロール/ステータス・レジスタ群、アプリケーション・インターフェース回路、発振回路を含み、容易に USB システムを実現することを可能にします。

データ転送モードは、コントロール転送、バルク転送、インタラプト転送、およびアイソクロナス転送をサポートし、5 個あるいは 6 個のエンドポイントをサポートします。

主な特長を以下に記します。

USB1.1 準拠

Full-speed (12Mbps) に対応

4 つのデータ転送タイプに対応

コントロール転送、バルク転送、インタラプト転送、アイソクロナス転送

エンドポイント : 5 個あるいは 6 個

コントロール EP 1 個

バルク/インタラプト EP 3 個

アイソクロナス/バルク/インタラプト EP 1 個あるいは 2 個

データ格納用 FIFO 内蔵

EP1、EP2、EP4、EP5 の FIFO は 2 面構成

DMA 転送可能 (EP1,EP2,EP4,EP5)

バスパワードデバイス対応

サスペンド条件を自動検出し、低電力モードに入ります。またレジューム条件を検出すると正常動作に自動復帰します。

ML60852A のレジスタ群は 0x681000 からマップされますが、16-Bit のバスに接続されていますので、各レジスタのオフセットは ML60852A のマニュアル記載のアドレスに 2 を掛けたアドレスにな

ります。

| アドレス    | 対象レジスタ名       |

|---------|---------------|

| 681000H | bmRequestType |

| 681002H | brequest      |

| 681004H | wValueLSB     |

| //      | //            |

USBC のレジスタ配置

#### ハードウェア情報

DMA 転送を行う場合は以下の設定で使用してください。

- |               |                     |

|---------------|---------------------|

| データバス幅 :      | 16-Bit              |

| 転送モード :       | デュアルアドレスモード、シングルモード |

| DRQ のインターバル : | 未定                  |

| DRQ0/1 の論理 :  | アクティブ・ローを推奨         |

DMA 関連の制御信号は以下の通り接続されています。

- |         |                      |

|---------|----------------------|

| DRQ0-   | -> CPU_P02/INTP1/TI3 |

| DRQ1-   | -> CPU_P03/INTP2/TI4 |

| DACK0/1 | -> 未使用 ( プルダウン )     |

割込みは以下の通り接続されています。

- |       |                          |

|-------|--------------------------|

| INTR- | -> PIC 経由で CPU_P05/INTP4 |

|-------|--------------------------|

その他

コントローラへの入力クロックは、12MHz の Xtal です。

USB-IF の電源ライン ( 1pin ) が CPU\_P04/INTP3/TI5 に接続されており、通電時の論理レベルが “ 1 ” です。

#### 7.4.15. LANC (LAN91C111:684300H – 68430EH)

LANC は SMSC 社製の LAN91C111 が実装されています。LAN91C111 はシングルチップで、10/100Mbps の両方に対応した LAN コントローラです。詳細はコントローラのマニュアルを参照ください。

---

LAN コントローラのレジスタへのアクセスはハーフワード(16-Bit)で

アクセスしてください。バイトでのアクセスは禁止です。

---

## 8. ソフトウェア

RTE-V850ES/SA3-CB ボードのハードウェアの初期化と周辺デバイスの使用方法について説明します。

### 8.1. 初期化

モニタを使用しないで、ROM からブートするプログラムを開発する場合は、最初のルーチンで V850ES/SA3 の内部バスコントローラを初期化しなければなりません。初期化時に設定する値については、「7.2推奨設定」を参照してください。

### 8.2. uPD71054 に対する連続アクセス

uPD71054 に対し連続してアクセスする場合は、1回目のアクセスと2回目のアクセスの間に他の空間へのアクセスを1回以上入れてください。これは、uPD71054 に対するリカバリ・タイムを確保する為です。

リカバリ・タイムは、uPD71054 以外の資源（例えば、ROM）をダミーで一度リードすることで確保できます。

### 8.3. ライブラリ

Cコンパイラでプログラムする時に必要となるI/Oアクセスなどのライブラリです。ただし、これらの記述やパラメータ受け渡し方法などは、GHS環境でのものです。他のコンパイラ等を使用する場合には、変更が必要となる場合があります。

```

/* I/O 入出力ライブラリ */

/* GHS V800 コンパイラ パラメータ受け渡し */

/* arg0 : r6, arg1 : r7, arg2 : r8, return : r10 */

inb(int addr)           /* バイト(8ビット)入力 */

{

__asm__(" ldi.b 0[r6], r10");

}

inh(int addr)           /* ハーフワード(16ビット)入力 */

{

__asm__(" ldi.h 0[r6], r10");

}

inw(int addr)           /* ワード(32ビット)入力 */

{

__asm__(" ldi.w 0[r6], r10");

}

outb(int addr, int data) /* バイト(8ビット)出力 */

{

__asm__(" std.b r7, 0[r6]");

}

outh(int addr, int data) /* ハーフワード(16ビット)出力 */

{

__asm__(" std.h r7, 0[r6]");

}

outw(int addr, int data) /* ワード(32ビット)出力 */

{

__asm__(" std.w r7, 0[r6]");

}

```

#### 8.4. タイマの使用例

ボード上の外部タイマ (uPD71054) でカスケード接続されたタイマ1とタイマ2を使用した時間計測のサンプルを示します。タイマ1はインターバルカウンタ（モード2）、タイマ2は、ダウンカウンタ（モード0）として初期化して、時間計測するルーチンの前後でカウンタ値を求めておくことで実行時間が算出できます。ただし、タイマのカウント値はどちらもダウンカウンタとなることに注意してください。また、外部タイマの連続アクセスではコマンドリカバリ（ROM領域のダミーリード）が必要となります。

```

/* タイマによる実行時間計測サンプル */

#define TIMERCLK      2000000          /* 2MHz */

#define INTERVAL       (TIMERCLK * 10 / 1000) /* 10ms (1/100) */

#define IOWAIT()        (*(char *) 0x680000) /* I/O コマンドリカバリ用 */

InitTimer() /* タイマ初期化 */

{

outb(0x680930, 0x74);           IOWAIT(); /* タイマ1 モード2 */

outb(0x680910, INTERVAL);       IOWAIT(); /* タイマ1 下位カウント */

outb(0x680910, INTERVAL / 256); IOWAIT(); /* タイマ1 上位カウント */

outb(0x680930, 0x80);           IOWAIT(); /* タイマ2 モード0 */

outb(0x680920, 0xFF);           IOWAIT(); /* タイマ2 下位カウント */

outb(0x680920, 0xFF);           IOWAIT(); /* タイマ2 上位カウント */

return 0;

}

LatchTimer() /* カウントラッチ */

{

int count1, count2, counts;

outb(0x680930, 0xDC);           IOWAIT(); /* タイマ1/2 マルチブルラッチ */

count1 = inb(0x680910);         IOWAIT(); /* タイマ1 カウント */

count1 += inb(0x680910) * 256;   IOWAIT(); /* タイマ2 カウント */

count2 = inb(0x680920);         IOWAIT();

count2 += inb(0x680920) * 256;   IOWAIT(); /* タイマ2 カウント */

counts = INTERVAL * (0xFFFF - count2)

+ (INTERVAL - count1);

return counts;

}

double total_time;

main()

{

int start_count, stop_count;

InitTimer();

start_count = LatchTimer(); /* スタートカウント値 */

func();

stop_count = LatchTimer(); /* ストップカウント値 */

total_time = (double)(stop_count - start_count)

/ (double)TIMERCLK; /* 秒数 */

return 0;

}

#include <time.h>

func() /* 時間計測ルーチン */

{

....

}

```

## 9. マスカブル割り込みを使用したアプリケーションの開発

本章では、RTE-V850ES/SA3-CB 上でマスカブル割り込みを使用したアプリケーションの開発を行う場合の方法と制限事項について説明します。

### 9.1. 割り込みベクタ

V850ES/SA3 の割り込みベクタ領域である 000000H ~ 00037FH 番地は、ROM により固定されていて書換えることができません。そこでモニタでは、SRAM 上の 100000 ~ 10037FH 番地に代替えベクタ領域を用意しています。

このモニタでは、000000H ~ 00037FH 番地の割り込みベクタ領域から代替えベクタ領域に分岐しています。

例えば、例外コードが 0080H の割り込みが発生すると、CPU の割り込み機能により 000080H 番地に分岐します。そこには代替えベクタ領域のオフセット 0080H 番地への分岐命令があり、代替えベクタ領域のオフセット 0080H 番地へ分岐します。ユーザ・プログラムでは、分岐先の代替えベクタ領域を書換えることにより、割り込み発生時にユーザ・プログラムの割り込み処理ルーチンに分岐させることができます。

したがって、前述の例外コード 0080H 割り込みの場合、目的の割り込み処理に分岐する命令を 100080H 番地に書き込みます。

通常の V850ES/SA3 のプログラムと異なるのは、通常ベクタ領域は ROM 化の時点で固定されており、プログラムで設定する（書換える）必要はありません。しかし、RTE-V850ES/SA3-CB 上でモニタを使用したプログラムの場合、プログラムでベクタを書換えてから、割り込みを許可する必要があります。

代替えベクタを書換えるためのプログラム例を以下に示します（割り込み処理ルーチンから代替えベクタ領域への相対アドレスが 22Bit 以内の場合）。

```

void SetAJump(int addr, int jmpdest) /* ベクタ設定ルーチン */

{

/* int addr;                                address where we're storing the

* 'jr' */

/* int jmpdest;      address where the 'jr' jumps to */

{

int offset;

unsigned inst;

unsigned int *p;

offset = jmpdest - addr;

inst = 0x07800000 /* 'jr' opcode */ | (offset & 0x003ffff);

*((UINT16 *)addr) = (inst >> 16) & 0xffff;

*((UINT16 *)(addr + 2)) = (inst) & 0xffff;

}

.....

}

void __interrupt IntEntry() /* 割り込み処理ルーチン */

{

.....

}

.....

main()

{

.....

SetAJump((int)(0x080 + 0x100000),(int)IntEntry);

/*          目的の割り込みの例外コード */

}

```

## 9.2. 一般的な制限事項 / 注意事項

マスカブル割り込みを使用したアプリケーションをデバッグする上での制限事項と注意事項を以下に示します。

- 1) 代替えベクタの設定前に割り込みが発生した場合や、代替えベクタを正しく設定しないで割り込みが発生した場合には、割り込みの発生時点でのプログラム位置でブレークします。これは、代替えベクタの初期値がモニタのブレーク処理ルーチンへの分岐命令になっているためです。

- 2) 代替えベクタ領域から割り込み処理ルーチンまでの相対アドレスが 22Bit を超える場合、割り込み処理ルーチンへの分岐のために、少なくとも 1つ以上のレジスタの値を壊すか、分岐の中継点を作る必要があります。

- 3) 代替えベクタ領域は、プログラムで書換えるか、プログラムのダウンロード時に書換えることができます（「9.3 ダウンロード時の代替えベクタ領域書換え方法」を参照）。但し、プログラムのダウンロード時の書換えは、使用する割り込み以外を書換えないようにしてください。

- 4) 割り込み関係を含む全てのペリフェラルは、ボード上のリセット・スイッチによってのみ初期化されます。 したがって、一度プログラムを実行した後に、プログラムを再ロードして動作させる場合、前のプログラム実行による影響がペリフェラル上に残っている場合があり、誤動作の原因になります。ペリフェラルを使用するプログラムを再実行させる場合は、以下の手順にしたがってください。

- (1) モニタをディスコネクトします。

- (2) RTE-V850ES/SA3-CB のリセット・スイッチを押しボードをリセットします。

- (3) モニタにコネクトします。

- (4) プログラムをロードして実行します。

- 5) プログラムの先頭で DI ( 割り込み禁止 ) 状態にしてから、ペリフェラルやベクタの設定をした後、EI ( 割り込み許可 ) 状態にするようにしてください。

- 6) ブレーク中に割込みの DI(割込み禁止) / EI(割込み許可) 状態をデバッガの I/O(レジスタ) 操作機能で行う場合は、割込みマスクレジスタ(IMRn)の該当ビットで行ってください。ブレーク中に割込み制御レジスタ(PICn or PnnICn)をデバッガの I/O(レジスタ) 操作機能で操作した場合は、割込み動作が正しく機能しなくなることがありますので、割込み制御レジスタの操作は行わないでください。

## 9.3. ダウンロード時の代替えベクタ領域書換え方法

プログラムのダウンロード時にベクタを書換える方法として、GHS 社の Multi 環境を基に例を示します。また、この方法は実際に ROM 化するプログラムに類似した方法とも言えます。尚、前述のプログラム例と合わせて参照してください。

- 1) 割り込みベクタ書換え用のプログラムを定義 (ASM 言語)

割り込みベクタに置く分岐命令だけのプログラムを以下のように定義します。記述方法の詳細については、言語処理系のマニュアルを参照してください。

```

.section      "intvct", .text    /* Defined section name */

.align       4

.globl        _Int80

_Int80:

jr  _IntEntry           /* jump to handler */

nop

nop

```

但し、1つの割り込みに対してベクタの境界を超えて定義することはできませんので注意してください。

## 2) セクション・マップの定義

リンク時に使用するセクション・マップを以下のように定義します。以下は、内蔵 ROM 領域にプログラムを配置する場合の例です。記述方法の詳細については、言語処理系のマニュアルを参照してください。

```

{

.intvct      0x100080  :

.text         0x108000  :

.data         align(0x10)   :

.

.

}

```

ベクタに置くプログラムのセクションを最初に定義します。

複数の割り込みを使用する場合には、連続したベクタであれば1つのセクションを定義することで対処できます（割り込みベクタの境界を合わせることが必要です）。不連続の場合は、割り込み毎にセクションを定義し、セクション・マップに全てのセクションを指定することが必要です。

この方法でダウンロード時に代替ベクタ領域の所定の場所が書換えられます。また、割り込みベクタを書換えるためのコードを記述する手間を省くことができます。

## 9.4. ブレーク・ポイント使用に関する制限事項 / 注意事項

割り込み処理ルーチン内へのブレークポイントの設定や、その後の実行（シングルステップ）に関し、以下の制限事項 / 注意事項がありますのでご注意ください。

- 1) ブレーク中は全てのマスカブル割り込みは受け付けません。

- 2) シングル・ステップ機能は、次の命令にテンポラリ・ブレーク・ポイントを設定する方式を取っています。この結果、EI(割り込み許可)状態のユーザ・プログラムをシングル・ステップする場合、シングル・ステップ中にも割り込みを受け付け、1命令をシングル・ステップする間に割り込み処理に分岐し、割り込み処理を行うことがあります。

したがって、シングル・ステップでも、ブレーク・ポイントに関する注意事項に気をつけなければなりません。

- 3) シングルステップによって割り込み処理ルーチンから抜けることはできません（具体的には、割り込みルーチンの最後の"}でのシングルステップができません）。同様に、reti 命令のシングルステップもできません。デバッガの"Return"機能で、割り込み処理ルーチンから元のルーチンへ戻ることはできません。

## 10.CPU 端子接続

本章では、RTE-V850ES/SA3-CB 内での CPU の各端子の使用状態を説明します。

### 10.1. 端子接続一覧

下表は CPU 端子の使用状態の一覧です。

| 端子名                                                                              | 使用状態                                                                                               | 参照章   |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------|

| PDL0-15/D0-15                                                                    | システムのデータバスとして使用                                                                                    |       |

| P90-915/A0-15,,PDH0-7/A16-23                                                     | システムのアドレスバスとして使用<br>PDH0 はフラッシュプログラムの H/S 線としても使用                                                  |       |

| PCT0/LWR-<br>PCT1/UWR-<br>PCT4/RD-<br>PCT7/BCYST-                                | システムバスの制御信号として使用                                                                                   |       |

| PCM0/WAIT-                                                                       | WAIT-として使用                                                                                         | 10.3  |

| PCM1/CLKOUT                                                                      | BUSCLK として使用                                                                                       |       |

| P00/NMI<br>P01/INTP0/TI2/                                                        | モニタ用の割り込み線(INT0)の入力として使用                                                                           | 10.4  |

| P02/INTP1/TI3<br>P03/INTP2/TI4<br>P04/INTP3/TI5<br>P05/INTP4                     | USBC の DRQ0-の入力として使用<br>USBC の DRQ1-の入力として使用<br>USB-IF の電源ラインモニタ割込みとして使用<br>PIC の INT1 の割込み入力として使用 | 10.5  |

| P43/INTP00/TI0/TCLR0<br>P44/INTP01/TO0<br>P45/INTP10/TI1/TCLR1<br>P46/INTP11/TO1 | TIC_CH#1 の出力を割り込み入力として使用<br>GINT1-の割込み入力として使用<br>GINT2-の割込み入力として使用<br>GINT3-の割込み入力として使用            | 10.6  |

| P30/SI1/RXD0                                                                     | SIO2-RXD として予約(SW4 で切断可能)                                                                          | 10.7  |

| P31/SO1/TXD0                                                                     | SIO2-TXD として予約                                                                                     | 10.8  |

| P32/SCK1-                                                                        | SIO2 の制御にポート(RTS)として予約                                                                             | 10.9  |

| P20/SI4                                                                          | SIO2 の制御にポート(CTS)として予約(SW4 で切断可能)                                                                  | 10.10 |

| P40/SI0<br>P41/SO0/SDA<br>P42/SCK0-/SCL                                          | フラッシュライタからの書き込み用として使用                                                                              | 10.11 |

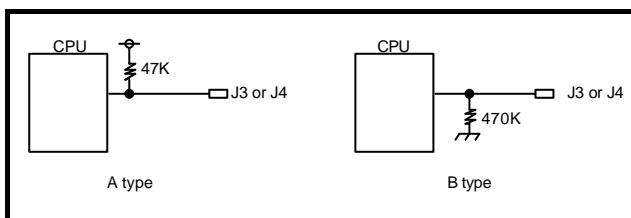

| P70-715/ANI0-15<br>P80-81/ANO0-1                                                 | 未使用、470K でブルダウン                                                                                    | 10.12 |

| その他のポート                                                                          | 未使用、47K でブルアップ                                                                                     | 10.12 |

| RESET-                                                                           | RESET を入力                                                                                          | 10.2  |

| X1,X2                                                                            | 17MHz の Xtal を接続<br>フラッシュプログラムからのクロックを接続することも可                                                     |       |

| XT1, XT2                                                                         | 32.768kHz の Xtal を接続                                                                               |       |

### 10.2. RESET-

CPUへのリセットは以下に示した要因で発生します。このリセットは、CPUをリセットすると共にボード全体のシステム・リセットとなります。

- **パワーオン・リセット**：ボードの電源ON時に発生するリセットです。

- **JROM\_EMからのリセット要求**：JROMEMコネクタのRESET-端子からの入力によるリセットです（「5.10 ROMエミュレータ用テストピン (JROM-EM1)」参照）。

- **SW\_RESETによるリセット**：リアパネル部分に用意されているリセット・スイッチ(SW\_RESET)が押されるとリセットが発生します（「5.1 リセット・スイッチ (SW\_RESET)」参照）。

- **JGBUSからのリセット**：JGBUSに接続したボードからのリセットです。

- **JFLASHからのリセット**：フラッシュプログラマからのリセットです。

RESETの生成ロジックの概要を下図に示します。

### 10.3. PCM0/WAIT-

PCM0/WAIT-端子は、READY信号として使用されています。

タイムオーバ・レディーは、バスサイクルが一定時間以上経過してもクローズしない場合と、GBUSのGMOTHER\_DETECT-信号がHigh(GBUSにボードが接続していない)の時、GBUSに割り当てられた空間へアクセスした場合に発生します。

タイムオーバ・レディーが発生した場合、ボード上のTOVER\_LEDが点灯し、PICに対し割り込みが入ります。TOVER\_LEDはタイムオーバ・レディーLEDクリア・パルスをソフト的に発生させるか、ボードがリセットされるまで点灯し続けます（「7.4.5 タイムオーバ・レディーLEDクリア・パルス(TOVRDY\_LED\_CLRPLS 680300H [Write Only])」参照）。

READYのドライブ部分の構成を下図に示します。

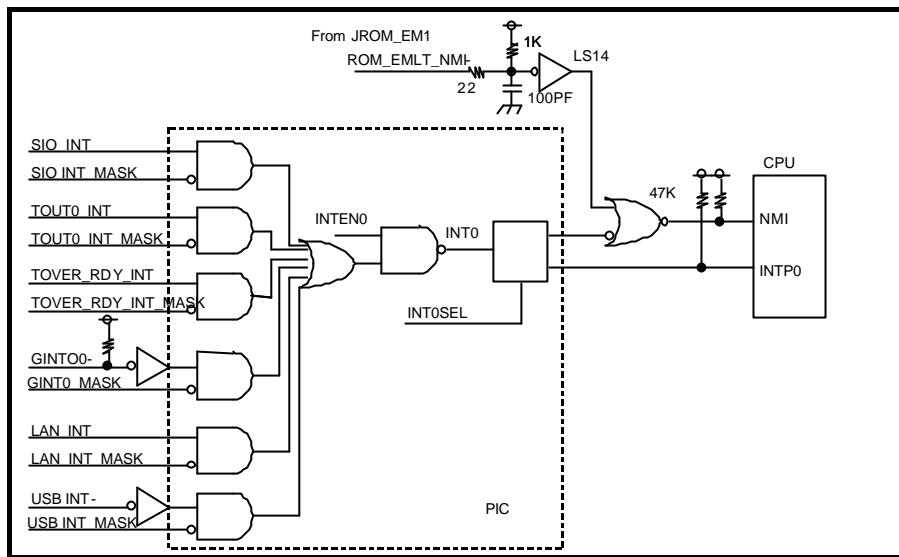

#### 10.4. P00/NMI, P01/INTP0/TI2

NMI, INTP0 の生成ロジックの概念図を下図に示します。下図の xxx\_MASK 信号は、PIC のレジスタへの設定を示します（「7.4.6 割り込みコントローラ(PIC:680400H - 680430H [Read/Write])」参照）。

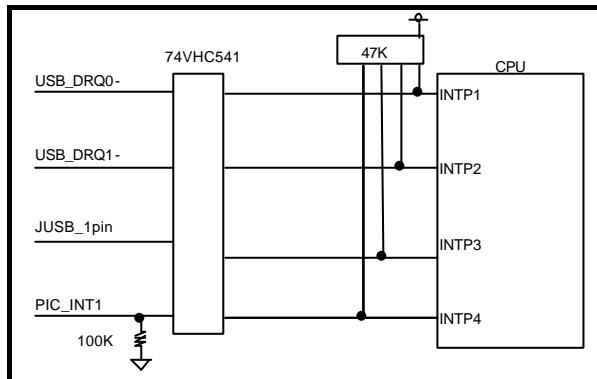

#### 10.5. P02/INTP1/TI3, P03/INTP2/TI4, P04/INTP3/TI5, P05/INTP4

P02/INTP1/TI3, P03/INTP2/TI4 は、USBC からの DMA 起動用の割込みとして使用し、P04/INTP3/TI5 は、USB-IF の電源モニタ、P05/INTP4 は PIC からの INT1 の割り込みとして使用します。

それぞれの接続の様子を下図に示します。

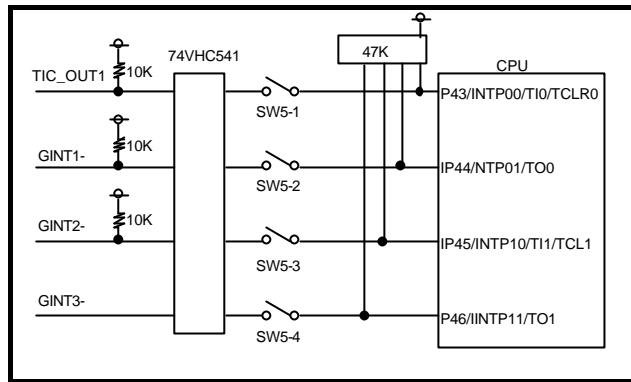

#### 10.6. P43/INTP00/TI0/TCLR0, P44/INTP01/TO0, P45/INTP10/TI1/TCLR1, P46/INTP11/TO1P46/INTP03/TO1

P43/INTP00/TI0/TCLR0, P44/INTP01/TO0, P45/INTP10/TI1/TCLR1, P46/INTP11/TO1P46/INTP03/TO1 は、割り込みとして使用し、GBUS-INT0,1,2、及び、TIC\_OUT1(タイマーCH#1 の出力)がスイッチを経由して接続されています。

それぞれの接続の様子を下図に示します。

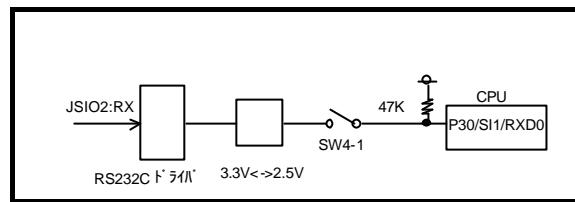

### 10.7. P30/SI1/RXD0

P30/SI1/RXD0 端子は、SIO2 の Rx を RS232C 受信ドライバを経由して接続されています。この様子を下図に示します。

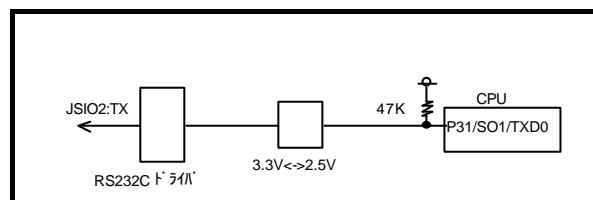

### 10.8. P31/SO1/TXD0

P31/SO1/TXD0 端子は、RS232C 送信ドライバを経て、SIO2 の Tx に使用されています。この様子を下図に示します。

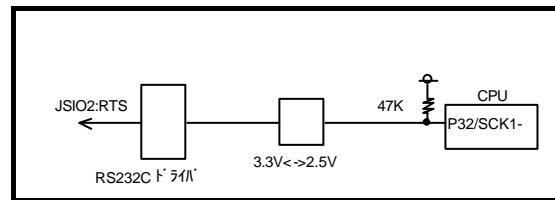

### 10.9. P32/SCK1-

P32/SCK1-端子は、RS232C 送信ドライバを経て、SIO2 の RTS に使用されています。この様子を下図に示します。

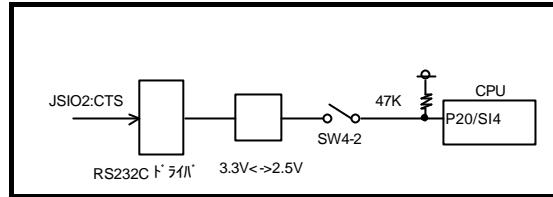

### 10.10.P20/SI4

P20/SI4 端子は、SIO2 の CTS を RS232C 受信ドライバ経由して接続されています。この様子を下図に示します。

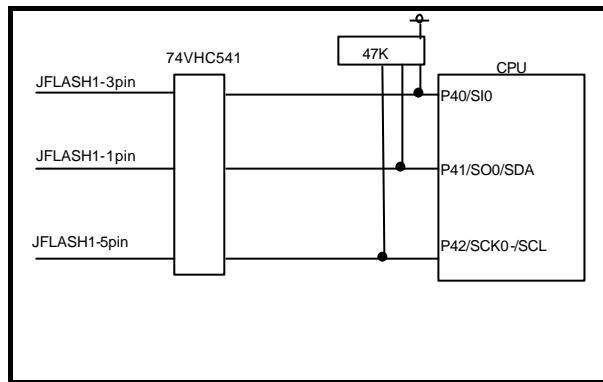

### 10.11.P40/SI0,P41/SO0/SDA,P42/SCK0-/SCL

P40/SI0,P41/SO0/SDA,P42/SCK0-/SCL は、フラッシュライタとの通信用に JFLASH1 コネクタに接続されています。

それぞれの接続の様子を下図に示します。

### 10.12.その他の信号

ボード内で使用していない信号は、一部を除き J3, J4 コネクタに接続しています。

## 11.GBUS 個別仕様

本章では、RTE-V850ES/SA3-CB での GBUS の使用状況を説明します。GBUS の一般的な仕様については「14 APPENDIX.C GBUS 共通仕様」を参照してください。

### 11.1. 概 要

RTE-V850ES/SA3-CB での GBUS の信号線使用状況を下表に示します。

| GBUS 信号名                          | 機能                                                         | 参照   |

|-----------------------------------|------------------------------------------------------------|------|

| GADDR[31:2]                       | アドレス線として使用。GADDR[26:31]は未接続。GADDR[25:24]は、Don't care。      |      |

| GDATA[31:0]                       | データ線として使用。リード・サイクル時は、VBCLK の立ち上がりでラッチされたものが CPU に供給される。    |      |

| GCS-[6:0]                         | 本ボードで生成して、チップ・セレクト線として出力。                                  |      |

| GCLK                              | CPU の BUSCLK とは、非同期の 33MHz 固定のクロックを出力。                     |      |

| GRESETI-                          | 本ボード上で発生したリセット要求を出力。                                       |      |

| GRESETO-                          | GBUS からのリセット要求として使用。                                       |      |

| GADS-, GREADY-,<br>GBLAST-, GW/R- | バス制御信号として使用。                                               |      |

| GWAITI-                           | 未接続                                                        |      |

| GBTERM-                           | 未接続                                                        |      |

| GRD-, GWR-                        | GBUS の制御信号から生成した、RD-, WR- 信号を接続。                           |      |

| GHOLD-, GHLDIA-                   | 未接続                                                        |      |

| GBREQ-                            | 未接続                                                        |      |

| GDMARQ-[3:0]                      | 未接続                                                        |      |

| GDMAAK-[3:0]                      | 未接続                                                        |      |

| GINTO-[3:0]                       | 割り込み要求信号として使用。                                             | 10.6 |

| GINTI-[1:0]                       | GINTI0- と GINTI1- へは、それぞれ TIC(μPD71054) の OUT0 と OUT1 を接続。 |      |

| GETC[7:0]                         | 未接続。                                                       |      |

| GAHI_EN-                          | 未接続                                                        |      |

| GMOTHER_DETECT-                   | タイムオーバ・レディー生成回路で使用。                                        |      |

| GUSE_DIRECT_ACC-                  | 未接続                                                        |      |

| GCLK_LOW-                         | 未接続                                                        |      |

| GLOCK-[1:0]                       | 未接続                                                        |      |

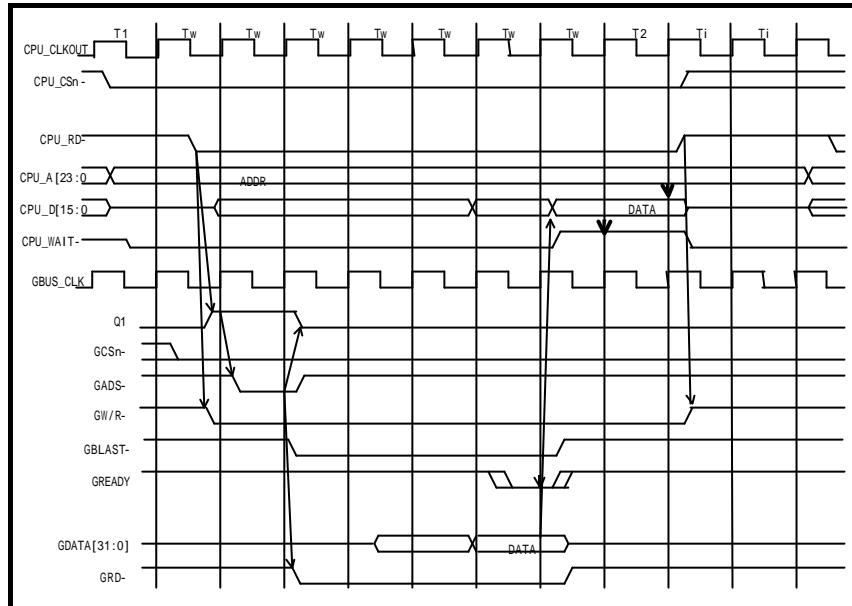

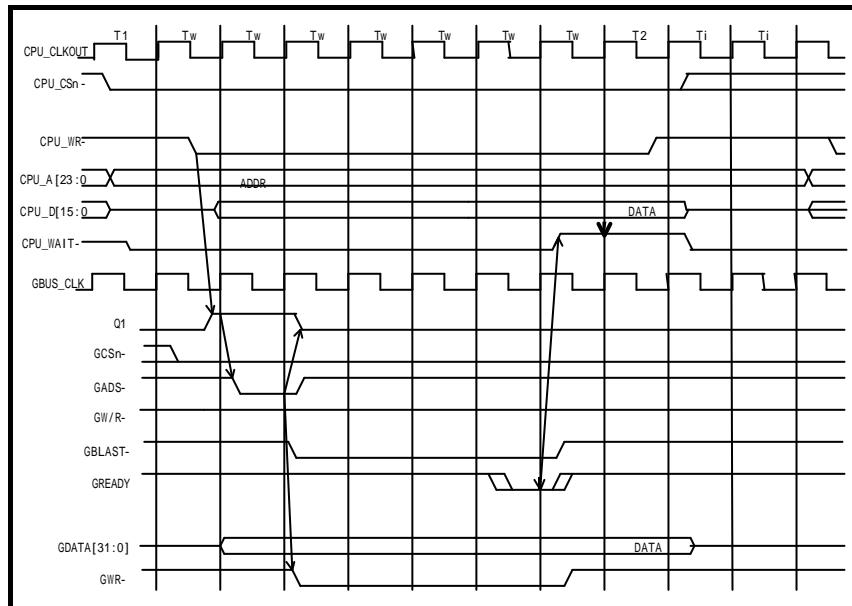

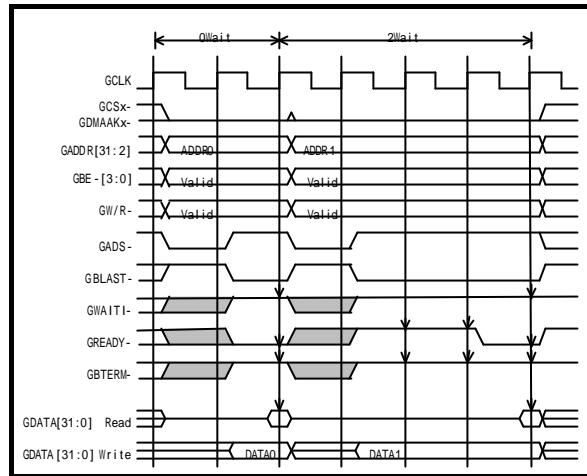

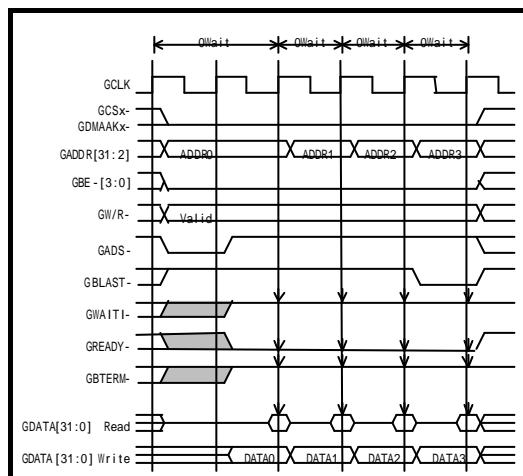

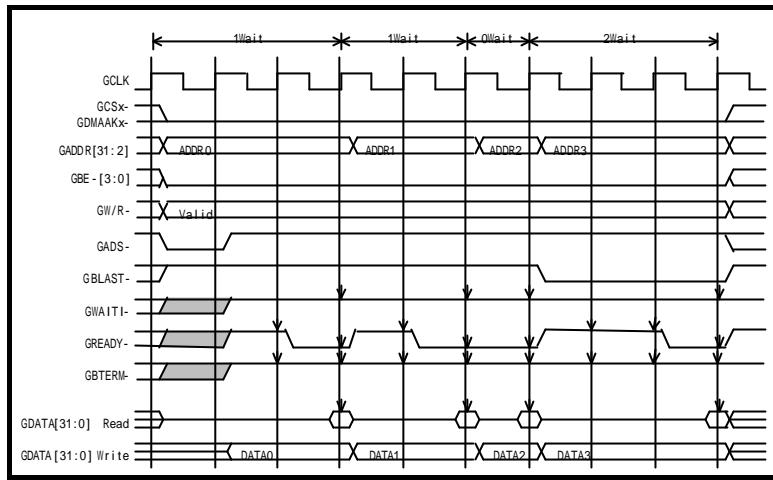

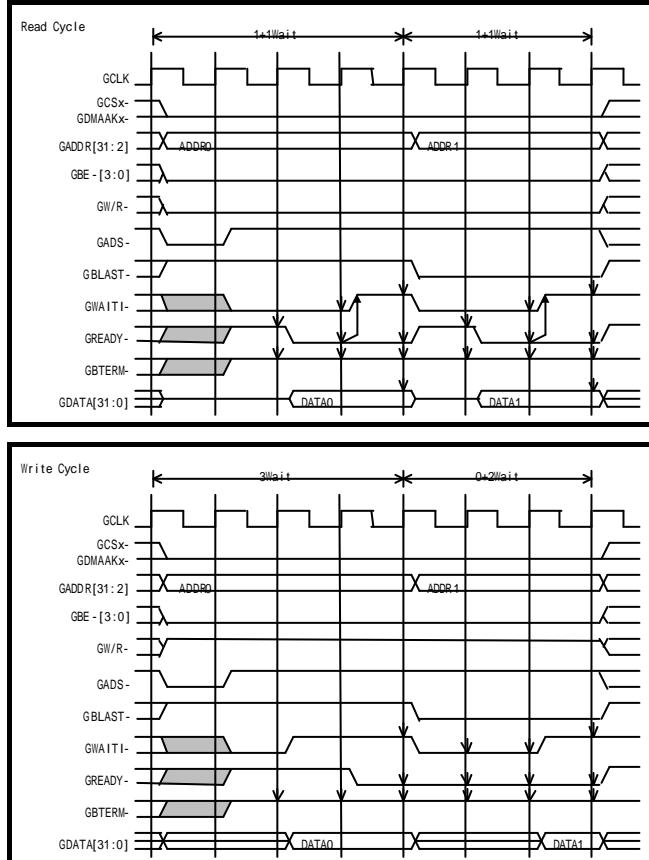

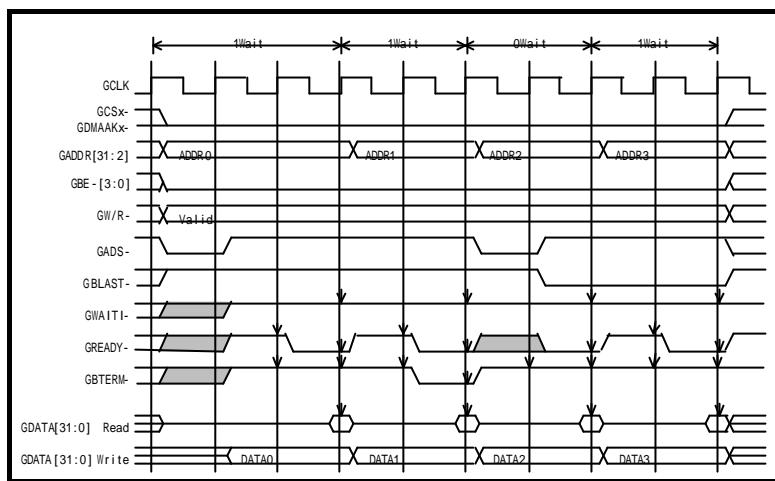

## 11.2. バス・サイクル

GBUS の GCLK へは、CPU のクロックを接続しています。GAHI\_EN-を未接続にしているので、GADDR[26:31]は未接続になっています。また、GADDR[24:25]は常に[0,0]です。

GBUS からのリード・サイクルは、GBUS 上で 0Wait 動作が可能です。

以下に示す波形で、CPU\_xxx 信号は CPU の信号です。また、Gxxx 信号は GBUS の信号です。

リード・サイクルの様子を下図に示します。

ライト・サイクルの様子を下図に示します。

### 11.3. チップセレクト

本ボードでは、GBUS の各チップセレクトには、下記の空間が割り当てられています。下記の全ての空間では、CPU 内蔵のバス・コンフィグレーション・レジスタの設定は、16 ビット・データバス幅、0 または 1Wait に設定してください（「7.2.1 CPU レジスタ」参照）。

| GBUS<br>信号名 | CPU<br>アドレス範囲                                          | 備考                                                                                                               |      |      | RTE-MB-A の資源  |

|-------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|---------------|

| GCS0-       | 700000 - 7FFFFF(*1)                                    | 7.4.8MB-SRAM High ADDR (680600H[Read/Write])                                                                     |      |      | 共有 SRAM(2M)   |

| GCS1-       | 400000 - 47FFFF<br>480000 - 5FFFFFF<br>600000 - 67FFFF | SW2-1:FBOOT=OFF 時にホット 512K<br>ホット 512K 以降の 1.5M-Byte<br>ホット 512K<br>7.4.9MB-FROM High ADDR (680610H[Read/Write]) |      |      | フラッシュ ROM(8M) |

| GCS2-       | 690000 - 69FFFF                                        |                                                                                                                  |      |      | IO レジスタ       |

| GCS3-       | 6C0000 - 6FFFFFF(*1)                                   | 7.4.11MB-EXTBUS-IO                                                                                               | High | ADDR | EXT-bus:メモリ空間 |

| GCS4-       | 6A0000 - 6AFFFFFF(*1)                                  | 7.4.11MB-EXTBUS-IO                                                                                               | High | ADDR | EXT-Bus:IO 空間 |

| GCS5-       | 800000 - FFFFFFF                                       |                                                                                                                  |      |      | PCI バス空間(MEM) |

| GCS6-       | 688000 - 688FFF                                        |                                                                                                                  |      |      | PCI-Cont レジスタ |

| GCS7-       | 6B0000 - 6BFFFFFF                                      |                                                                                                                  |      |      | PCI バス空間(IO)  |

補足：

\*1:これらの空間は CPU のアドレス範囲を越える資源が MB ボード上にあります。

本ボードでは、全ての資源をアクセスする為に上位アドレスを指定する為のポートがあります。

### 11.4. RTE-MB-A の初期設定

PCI バスに関する PLEX-9080 の設定は、下表のように設定してください

| レジスタ名                                                            | アドレス     | 設定値        |

|------------------------------------------------------------------|----------|------------|

| Local Range Register for Direct Master to PCI(9CH)               | 0x68809C | 0xFF800000 |

| Local Bus Address Register dor Direct Master to PCI Memory(A0h)  | 0x6880A0 | 0x00800000 |

| Local Base Address Register for Direct Master to PCI IO/CFG(A4h) | 0x6880A4 | 0x80000000 |

## 12. APPENDIX.A Multi モニタ

Multi 用のモニタ ROM を使用して、ホストの Multi デバッガと接続して使用する場合の設置方法と使用上の注意事項について説明します。

### 12.1. ボードの設置

#### 12.1.1. RTE for Win32 のインストール

Multi デバッガを使用する場合には、PC に通信用のソフトウェア（RTE for Win32）をインストールする必要があります。ソフトウェアのインストールとテストについては、添付の「RTE for Win32 インストール・マニュアル」を参照してください。

#### 12.1.2. SW1 の設定

SW1 は、汎用の入力ポートのスイッチですが、実装されている Multi 用のモニタでは、以下の通り使用しています。正しく設定してご使用ください。

| SW1 番号 | 1   | 2   | ポーレート                 |

|--------|-----|-----|-----------------------|

| 設定     | ON  | ON  | 115200 baud           |

|        | OFF | ON  | 38400 baud            |

|        | ON  | OFF | 19200 baud            |

|        | OFF | OFF | 9600 baud<br>(出荷時の設定) |

ポーレートの設定

| SW1 番号 | 3   | 4   | プロファイラ周期                  |

|--------|-----|-----|---------------------------|

| 設定     | ON  | ON  | タイムを使用しない                 |

|        | OFF | ON  | 200 Hz 5 ms               |

|        | ON  | OFF | 100 Hz 10 ms              |

|        | OFF | OFF | 60 Hz 16.67ms<br>(出荷時の設定) |

プロファイラ周期の設定

| SW1 番号 | 5   | デバッガのモード                |

|--------|-----|-------------------------|

| 設定     | ON  | INTP0 を使用します。           |

|        | OFF | NMI を使用します。<br>(出荷時の設定) |

モニタで使用する割込みの設定

| SW1 番号 | 8   | デバッガのモード            |

|--------|-----|---------------------|

| 設定     | ON  | テストモードでモニタを立ち上げます。  |

|        | OFF | 通常の使用状態<br>(出荷時の設定) |

デバッグモードの設定

SW1-6～7 は、Multi モニタでは使用していません。

SW1-8 を ON にした場合、立上げに時間がかかります。また、LED に対しモニタが表示を行います。

通常は、OFF の状態でご使用ください。

#### 12.1.3. ボードの接続

「6 ホスト PC との接続」を参照して、シリアルで PC と接続してください。

## 12.2. Multi モニタ

### 12.2.1. 起動時の 7Seg-LED

Multi 用の ROM モニタは、ボードの電源を入れると 7Seg-LED が次のように動きます（黒い部分が点灯部分）

1) 7Seg-LED のチェック動作（下図参照）

SW1-8 が OFF の場合：

SW1-8 が ON の場合：

2) SRAM の簡易メモリチェックによる数字のカウント

SW1-8 が OFF の場合は行いません。

3) 接続待ち状態（プロファイラのタイマを停止している場合は、ドットの点滅なし）

4) 接続状態（ドットの点灯は、接続した時のドットの点灯状態が保持される）

### 12.2.2. ROM モニタ・ワーク RAM

ROM モニタでは、SRAM の上位の 32KB (10-0000H – 10-7FFFH) をワーク用の RAM として使用しています。したがって、この空間とこの空間のイメージ領域は、ユーザ・プログラムで使用できません。

### 12.2.3. モニタ割り込み

モニタ通信、タイマ及び、強制ブレークで使用する割り込みは、SW2-5 で選択された割り込みを使用します。

### 12.2.4. \_INIT\_SP の設定

モニタで \_INIT\_SP ( スタック・ポインタの初期値 ) は、3F-7FF0H に設定されています ( Multi の環境で \_INIT\_SP で変更することもできます )。モニタでは、ユーザ・プログラムで設定したスタック領域を 32 バイト使用します。

### 12.2.5. タイマ割り込み

タイマ割り込みを禁止しますと、Multi のプロファイラ機能が使用できません（タイマ割り込みの設定については『12.1.2 SW1 の設定』を参照）。

### 12.2.6. ハードウェアの初期化

ROM モニタでは、ボード上の資源に対し、直にアクセスできるように初期化を行っています。

### 12.2.7. 特殊命令

以下の命令を、シングルステップ、ブレークポイント及びシスコール機能で使用しています。

BRKTRAP 命令 ( 0xnn40 )

ユーザ・プログラム内では、ブレーク命令と解釈されるコードは使用しないでください。

### 12.3. RTE コマンド

サーバと接続すると TARGET ウィンドウが開かれ、ここで RTE コマンドを発行することができます。表に RTE コマンドの一覧を示します。

| コマンド名   | 内容             |

|---------|----------------|

| HELP, ? | ヘルプ表示          |

| INIT    | イニシャライズ        |

| VER     | バージョン表示        |

| SFR     | 内部 I/O 表示 / 設定 |

RTE コマンド一覧

各コマンドには、パラメータを必要とするものがあります。アドレスやデータなど、数値のパラメータは、全て 16 進数とみなされます。以下の数値指定は誤りです。

0x1234 1234H \$1234

#### 12.3.1. HELP(?)

<書式> HELP [コマンド名]

HELP は、RTE コマンドの一覧や書式を表示します。また、"HELP"と入力するかわりに"??"としても同様です。コマンド名を省略すると、使用できるコマンド一覧を表示します。

<例> HELP SFR

SFR コマンドのヘルプを表示します。

#### 12.3.2. INIT

<書式> INIT

INIT は、RTE 環境の初期化を行ないます。通常、このコマンドを使用しないでください。

#### 12.3.3. VER

<書式> VER

VER は、RTE 環境のバージョンを表示します。

#### 12.3.4. SFR コマンド

<書式> SFR [レジスタ名 [=データ]]

レジスタ名を指定してデータを省略した場合は、そのレジスタからリードしたデータを表示します。レジスタ名と"="の後にデータを指定した場合には、そのレジスタにデータをライトします。データのサイズは、指定したレジスタの有効サイズで自動的に決定されます。内部 I/O レジスタの詳細については、V850ES/SA3-CPU のマニュアルを参照してください。

<例 1> SFR

レジスター一覧を表示します。

<例 2> SFR IMR

レジスタ IMR の内容を表示します。

<例 3> SFR IMR=55AA

レジスタ IMR にデータ 55AAH をライトします。

## 13.APPENDIX.B PARTNER モニタ

PARTNER 用のモニタ ROM を使用して、ホストの PARTNER と接続して使用する場合の設置方法と使用上の注意事項について説明します。

### 13.1. ボードの設置

#### 13.1.1. SW1 の設定

SW1 は、汎用の入力ポートのスイッチですが、実装されている PARTNER 用のモニタでは、以下の通り使用しています。正しく設定してご使用ください。

| SW1 番号 | 1   | 2   | ポーレート                 |

|--------|-----|-----|-----------------------|

| 設定     | ON  | ON  | 115200 Baud           |

|        | OFF | ON  | 38400 baud            |

|        | ON  | OFF | 19200 baud            |

|        | OFF | OFF | 9600 baud<br>(出荷時の設定) |

ポーレートの設定

| SW1 番号 | 3  | 4  | タイマ                                |

|--------|----|----|------------------------------------|

| 設定     | ON | ON | Partner では使用しませんので、常時この状態でご使用ください。 |

プロファイラ周期の設定

| SW1 番号 | 5         | デバッガのモード                                 |

|--------|-----------|------------------------------------------|

| 設定     | ON<br>OFF | INTP0 を使用します。<br>NMI を使用します。<br>(出荷時の設定) |

モニタで使用する割込みの設定

| SW1 番号 | 8         | デバッガのモード                                  |

|--------|-----------|-------------------------------------------|

| 設定     | ON<br>OFF | テストモードでモニタを立ち上げます。<br>通常の使用状態<br>(出荷時の設定) |

デバッグモードの設定

SW1-6 ~ 7 は、Partner モニタでは使用していません。

SW1-8 を ON にした場合、立上げに時間がかかります。また、LED に対しモニタが表示を行います。通常は、OFF の状態でご使用ください。

#### 13.1.2. ボードの接続

「6 ホスト PC との接続」を参照して、シリアルで PC と接続してください。

### 13.2. PARTNER モニタ

#### 13.2.1. 起動時の 7Seg-LED

Partner 用の ROM モニタが実装されている場合、ボードの電源を入れると 7Seg-LED が次のように動きます（黒い部分が点灯部分）。

1)7Seg-LED のチェック動作（下図参照）

SW1-8 が OFF の場合：

SW1-8 が ON 場合：

2)RAM の簡易メモリチェックによる数字のカウント

SW1-8 が OFF の場合は行いません。

3)接続待ち状態

4)接続状態

#### 13.2.2. ROM モニタ・ワーク RAM

ROM モニタでは、SRAM の上位の 32KB (10-0000H – 10-7FFFH) をワーク用の RAM として使用しています。したがって、この空間とこの空間のイメージ領域は、ユーザ・プログラムで使用できません。

#### 13.2.3. モニタ割り込み

モニタ通信及び、強制ブレーク（ESC ボタン）で使用する割り込みは、SW2-5 で選択された割り込みを使用します。

#### 13.2.4. SP の設定

モニタのスタック・ポインタの初期値は、3F-7FF0H に設定されています。（Partner 環境変数の INIT\_SP で変更することもできます）モニタでは、ユーザ・プログラムで設定したスタック領域を 32 バイト使用します。

#### 13.2.5. ハードウェアの初期化

ROM モニタでは、ボード上の資源に対し、直にアクセスできるように初期化を行っています。

#### 13.2.6. 特殊命令

モニタでは、以下の命令を、シングルステップ、ブレークポイント及びシスコール機能で使用しています。

BRKTRAP 命令 (0xnn40)

ユーザ・プログラム内では、ブレーク命令と解釈されるコードは使用しないでください。

## 14.APPENDIX.C GBUS 共通仕様

ここでは、ボードの品種に依存しないGBUSの仕様について説明します。

### 14.1. 用語

この章で用いる用語について説明します。

#### 14.1.1. CPU ボードとマザー・ボード

RTE-CB シリーズのボードのことを CPU ボード、CPU ボードの GBUS に接続する弊社製のボードをマザー・ボードと呼ぶことにします。

#### 14.1.2. バス・サイクル、マイクロ・サイクル

GBUS は、バースト・アクセス可能な一般的なバスです。

バス・サイクルとは、アクセスがバーストした場合も含み、一連のサイクルが終了するまでの区切りのことを示すものとします（1回のGADS-のアサートが必要とされる区切り）。

バス・サイクルには、シングル・サイクルとバースト・サイクルがあります。シングル・サイクルとは、1回のデータ転送しか発生しないバス・サイクルのことを示します。バースト・サイクルとは、複数回のデータの転送が発生するバス・サイクルのことを示します。

また、バースト・サイクルのデータ転送1回ごとのサイクルをマイクロ・サイクルと呼ぶことにします。

### 14.2. 信号

GBUS の信号の内容を下表に示します。GBUS の各信号の入出力方向は、マザー・ボード側を基準にして記述します。つまり、「入力」とある場合、CPU ボードから出力されマザー・ボードへ入力される信号を示します（信号名にもこの基準が適用されています）。

下表で「双方向」と記載されている信号はバス・サイクルの状態で信号の向きが切り替わることを示します。

また、「入力 / 出力」と記載されている信号はバス・マスタが CPU ボードなのかマザー・ボードなのかによって信号の向きが切り替わる事を示し、前に書かれているのが CPU ボードがバス・マスタの時の信号の方向、後に書かれているのがマザー・ボードがバス・マスタの時の信号の方向を示します。

GBUS の信号は、+5V の TTL レベルです。また、マザー・ボードは常にリトル・エンディアンです。

| 信号名      | 入出力 | 機能                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCLK     | 入力  | <ul style="list-style-type: none"> <li>GBUS の同期クロック。最高周波数は 33.33MHz。最低周波数は 10.0MHz。GBUS はこのクロックの立ち上がりに同期して動作する。</li> <li>マザー・ボード上では、+5V と GND に対してそれぞれ 330 でターミネーションされるため、CPU ボードの回路はこれをドライブできなければならない。</li> <li>GCLK が 16.67MHz より周波数が低い場合、GCLK_LOW-を Low にする。これにより、マザー・ボードはウェイト数の調整を行える。</li> <li>この信号は、PLL (Phase Lock Loop) によるゼロ・ディレイ・パッファが使用される場合があるので、GCLK の周波数を変更した場合は、PLL のロックのために周波数変更後最低でも 1m秒の間はマザー・ボードにアクセスしてはならない。</li> </ul> |

| GRESETI- | 入力  | <ul style="list-style-type: none"> <li>GBUS のリセット信号。CPU ボード上でリセットが発生した時に、この信号を Low にする。マザー・ボードはこの信号によってリセットされる（マザー・ボード上の他の要因によってマザー・ボードがリセットされる場合もある）。</li> </ul>                                                                                                                                                                                                                                                                           |