# *RTE-VR5432-CB*

ユーザーズ・マニュアル (Rev.2.01)

## 改定履歴

|    | 日付 |    | D    | 内容                                                                                                                                    |  |

|----|----|----|------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Y  | N  | D  | Rev  | rs <del>u</del>                                                                                                                       |  |

| 99 | 8  | 15 | 1.00 | 正式初版                                                                                                                                  |  |

| 99 | 9  | 15 | 1.01 | 消費電流を 2.5A(max)から 2.0A(max) に変更                                                                                                       |  |

| 99 | 12 | 29 | 2.00 | H/W のバージョン:Rev.2.00 の仕様変更(Big Endian におけるバスの仕様変更)に伴う変更。<br>変更した章、項は、以下の通り。それぞれに BigEndian に関する記述部分。<br>7.3 アドレス・マップ<br>9 ROM 化プログラミング |  |

| 00 | 4  | 12 | 2.01 | 誤記訂正<br>5.16 CPU コネクタ(JCP1,2)コネクタのメーカ名:KE ->ヒロセ<br>10.3 チップセレクト論理アドレス値                                                                |  |

## 注意事項

RTE-VR5432-CB は、Rev.2 において、Big Endian で使用する場合の仕様が変更になりました。

Rev.1:Byte-Swap を実施。

Rev.2:Byte Swap を廃止。

これに伴い、I/O 空間へのアクセスと ROM の書き込み方法が変更になり、この点について互換性がありません。ご注意ください。尚、Rev1 から Rev.2 へのバージョンアップは、無償で実施しております。

# 目次

| 1. la       | <b>まじめに</b>                                                | 1  |

|-------------|------------------------------------------------------------|----|

| 1.1.        | マニュアル表記について                                                | 1  |

| 2. 特        | <b>寺徴と機能</b>                                               | 2  |

| 3. ∄        | Eな特徴                                                       | 3  |

| 4. 基        | 基本仕様                                                       | 3  |

| 5. 才        | <b>ボードの構成</b>                                              | 4  |

| 5.1.        | リセット・スイッチ(SW_RESET)                                        | 4  |

| 5.2.        | 電源コネクタ(JPOWER)                                             | 4  |

| 5.3.        | スイッチ 1 ( SW1 )                                             | 4  |

| 5.4.        | スイッチ 2 ( SW2 )                                             | 5  |

| 5.5.        | スイッチ 3 ( SW3 )                                             | 5  |

| 5.6.        | スイッチ 4(SW4)                                                | 6  |

| 5.7.        | スイッチ 5 (SW5)                                               | 6  |

| 5.8.        | 7SEG-LED, xxx-LED                                          | 6  |

| 5.9.        | クロック・ソケット(OSC1)                                            | 7  |

| 5.10.       | ROM ソケット                                                   | 7  |

| 5.11.       | シリアル・コネクタ(JSIO1,2)                                         | 7  |

| 5.12.       | パラレル・コネクタ(JPRT )                                           | 8  |

| 5.13.       | ROM エミュレータ用テストピン(JROM-EML)                                 | 8  |

| 5.14.       | ICE コネクタ# 1 (JDCU1)                                        | 9  |

| 5.15.       | ICE コネクタ#2(JDCU2)                                          | 9  |

| 5.16.       | JGBUS コネクタ(JGBUS)                                          | 9  |

| 5.17.       | CPU コネクタ(JCP1,2)                                           | 10 |

| 6. オ        | 7スト PC との接続                                                | 11 |

| 6.1.        | RS-232C 接続                                                 | 11 |

| 7. <b>J</b> | \ードウェア・リファレンス                                              | 12 |

| 7.1.        | リセット                                                       | 12 |

| 7.2.        | 割込み                                                        | 12 |

| 7.3.        | アドレス・マップ                                                   |    |

| 7.3.        |                                                            |    |

| 7.3.        | 2. DRAM 空間 ( 0800-0000H ~ 0FFF-FFFFH )                     | 13 |

| 7.3.        | ,                                                          |    |

| 7.3.        | 4. I/O 空間(1800-0000H~1EFF-FFFFH)                           | 13 |

| 7.3.        | •                                                          |    |

| 7.4.        | I/O 詳細                                                     |    |

| 7.4.        | · · · · · · · · · · · · · · · · · · ·                      |    |

| 7.4.        |                                                            |    |

| 7.4.        |                                                            |    |

| 7.4.        | ·                                                          |    |

| 7.4.        |                                                            |    |

| 7.4.0       | 6. 7 セグメント LED 表示データ出力ポート(7SEG-LED B800-2000 [Write Only]) | 19 |

| 7.4.7.  | シリアル/パラレル I/O(SCC0/1, LPT B900-1000 ~ B900-4000[Read/Write]) | 20 |

|---------|--------------------------------------------------------------|----|

| 7.4.8.  | タイマ ( Timer B900-5000[Read/Write] )                          | 21 |

| 7.4.9.  | 割込みコントローラ(PIC B900-0000[Read/Write])                         | 22 |

| 7.4.10  | . DMA コントローラ                                                 | 23 |

| 8. バフ   | <b>マサイクル・タイミング</b>                                           | 27 |

| 8.1.    | SRAM アクセス                                                    | 27 |

| 8.2.    | DRAM アクセス                                                    | 29 |

| 8.3.    | ローカルバス・アクセス                                                  | 32 |

| 8.4.    | 所要クロック一覧                                                     | 34 |

| 8.4.1.  | SRAM のアクセス                                                   | 34 |

| 8.4.2.  | SDRAM のアクセス                                                  | 34 |

| 9. RO   | M 化プログラミング                                                   | 35 |

| 9.1.    | 初期化                                                          | 35 |

| 9.1.1.  | ROM データ配置                                                    | 35 |

| 10. GB  | US 個別仕様                                                      | 36 |

| 10.1.   | 概要                                                           | 36 |

| 10.2.   | バス・サイクル                                                      | 37 |

| 10.3.   | チップセレクト                                                      | 38 |

| 11. API | PEDIX.A MULTI モニタ                                            | 39 |

| 11.1.   | ボードの設置                                                       | 39 |

| 11.1.1  | RTE for Win32 のインストール                                        | 39 |

| 11.1.2  | . SW1 の設定                                                    | 39 |

| 11.1.3  | ボードの接続                                                       | 39 |

| 11.2.   | Multi モニタ                                                    | 40 |

| 11.2.1  | 起動時の 7Seg-LED                                                | 40 |

| 11.2.2  | モニタ・ワーク RAM                                                  | 40 |

| 11.2.3  | 割込み                                                          | 40 |

| 11.2.4  | _ INIT_SP の設定                                                | 40 |

| 11.2.5  | タイマ割込み                                                       | 40 |

| 11.2.6  | . ハードウェアの初期化                                                 | 41 |

| 11.2.7  | 特殊命令                                                         | 41 |

| 11.3.   | RTE コマンド                                                     | 41 |

| 11.3.1  | . HELP(?)                                                    | 41 |

| 11.3.2  | . INIT                                                       | 41 |

| 11.3.3  | . VER                                                        | 41 |

| 11.3.4  | . CACHEFLUSH                                                 | 41 |

| 11.3.5  | . SHOWTLB                                                    | 42 |

| 11.3.6  | . IOREAD                                                     | 42 |

| 11.3.7  | . IOWRITE                                                    | 42 |

| 12. API | PEDIX.B PARTNER モニタ                                          | 43 |

| 12.1.   | ボードの設置                                                       | 43 |

| 12.1.1  | . SW1 の設定                                                    | 43 |

| 12 1 2  | ボードの接続                                                       | 43 |

| 12.2.          | PARTNER モニタ                         | 44 |

|----------------|-------------------------------------|----|

| 12.2.          | 1. 起動時の 7Seg-LED                    | 44 |

| 12.2.          | 2. ROM モニタ・ワーク RAM                  | 44 |

| 12.2.          | 3. 割込み                              | 44 |

| 12.2.          | 4. INIT_SP の設定                      | 44 |

| 12.2.          |                                     |    |

| 12.2.          | 6. ハードウェアの初期化                       | 45 |

| 12.2.          |                                     |    |

| 13. AI         | PPEDIX.C 割込みプログラミング                 |    |

| 13.1.          | 割込みライブラリ                            | 46 |

| 13.1.          | 1. int InitIrqVect(void)            | 46 |

| 13.1.          | 2. int TermIrqVect(void)            | 46 |

| 13.1.          | 3. int SetIrqVect(int no, int func) | 46 |

| 13.1.          | 4. int GetIrqVect(int no)           | 46 |

| 13.1.          | 5. void SetIPnBit(int IPn)          | 46 |

| 13.1.          |                                     |    |

| 13.1.          |                                     |    |

| 13.1.          |                                     |    |

| 13.2.          | 割込みルーチン                             |    |

| 13.3.          | サンプルプログラム                           |    |

|                | PPEDIX.C GBUS 共通仕様                  |    |

| 14.1.          | 用語                                  |    |

| 14.1.          |                                     |    |

| 14.1.          |                                     |    |

| 14.2.          | 信号                                  |    |

| 14.3.          |                                     |    |

| 14.4.          | 未使用端子の処理                            |    |

| 14.5.          | GCS-[7:0]の割り付け                      |    |

| 14.6.          | バス・サイクル                             |    |

| 14.6.          |                                     |    |

| 14.6.          |                                     |    |

| 14.6.          |                                     |    |

| 14.6.<br>14.7  | 4. GBTERM タイミング                     |    |

| 14.7.<br>14.7. |                                     |    |

| 14.7.<br>14.7. |                                     |    |

| 14./.          | 4.                                  |    |

#### 1. はじめに

「RTE-VR5432-CB」は NEC 製の RISC プロセッサ VR5432 の評価を目的とした CPU ボードです。

ボードは最高 167MHz で動作する VR5432 CPU とメモリ、シリアル / パラレルインターフェース、拡張用のバスコネクタ等で構成されます。メモリは、高速の PB-SRAM と大容量の SDRAM を標準で実装しています。

これらの機能を使用して、プロセッサの性能評価、デモ、シミュレータの実行エンジン、アプリケーション・プログラムの初期段階の開発など、幅広くご利用頂けます。

本製品は開発用のソフトウェアツールとして、GHS 社の Multi と自社製の PARTNER のどちらかをソースレベルデバッガとしてご使用になれます。ご使用になるデバッガによって、ROM に搭載するモニタは異なります。

ROM は購入時にご指定頂いたモニタが搭載されています。デバッガを同時に購入されていない場合は、それぞれ別売りされていますので、別途お買い求めください。

# 1.1. マニュアル表記について

本書では、数字の表記については下表の表記を用います。16 進数や 2 進数の表記では、桁数が多くて読みにくい場合は、4 桁ごとに"-"(ハイフン)を入れてあります。また、数値で任意を示す場合には、"1FxxH"のように"x"で示します。

| 進数    | 表記規則           | 例                      |  |

|-------|----------------|------------------------|--|

| 10 進数 | 数字のみを示します      | "10"は 10 進数の"10"を示します  |  |

| 16 進数 | 数字の末尾に"H"を記します | "10H"は 10 進数の"16"を示します |  |

| 2 進数  | 数字の末尾に"B"を記します | "10B"は 10 進数の"2"を示します  |  |

数字表記規則

## 2. 特徴と機能

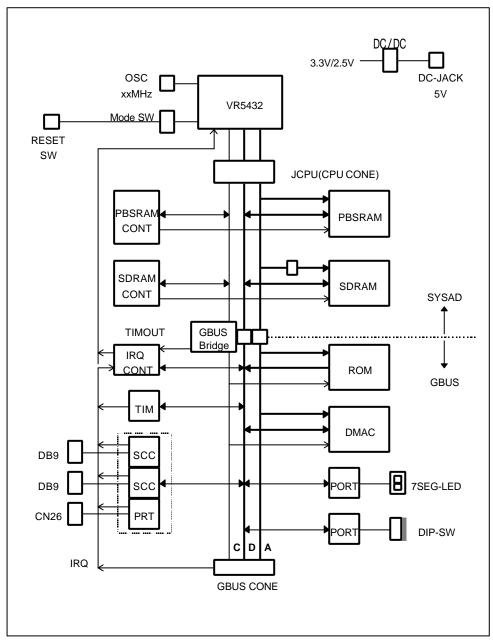

RTE-VR5432-CB の機能ブロックの概要を下図に示します。

ブロック図

## 3. 主な特徴

- ?? GreenHills 社の MULTI と自社製 PARTNER 用のモニタ ROM を用意しています。

- ?? 高級言語レベルでリアルタイム実行・評価が可能です。

- ?? PB-SRAM を 256K-Byte、SDRAM は 64M-Byte を標準搭載しています。

- ?? シリアル(2ch)、パラレル(IEE1284)のインタフェースを用意しています。

- ?? ROM エミュレータや N-Wire ツールが接続できます。

# 4. 基本仕様

| プロセッサ     | VR5432                                        |  |  |  |

|-----------|-----------------------------------------------|--|--|--|

| CPU クロック  | 150MHz (max.167MHz)                           |  |  |  |

| バスクロック    | 60MHz (max)                                   |  |  |  |

| 電源        | +5V, 2.0A (max)                               |  |  |  |

| メモリ       |                                               |  |  |  |

| EPROM     | 256KB 128K × 16bit (40pin-DIP) × 1(max.512KB) |  |  |  |

| PB-SRAM   | 256KB $32K \times 32bit \times 2$             |  |  |  |

| SDRAM     | 64MB $4M \times 4Bit \times 4Bank \times 8$   |  |  |  |

| I/O       |                                               |  |  |  |

| シリアルIF    | NS16550 相当 DB9 コネクタ × 2ch                     |  |  |  |

| パラレルIF    | IEEE1284 準拠 CON26 コネクタ                        |  |  |  |

| タイマ       | uPD71054 分解能 500nS                            |  |  |  |

| IO ポート    | LED(7seg)表示 / スイッチ入力                          |  |  |  |

| その他       |                                               |  |  |  |

| CPU コネクタ  | VR5432 全機能ピンを接続したコネクタ                         |  |  |  |

| GBUS コネクタ | RTE-CB 標準 32bit I/F(4GB,32bit バス,DMA 対応)      |  |  |  |

| リセット・スイッチ | Push 式                                        |  |  |  |

|           | ·                                             |  |  |  |

#### 5. ボードの構成

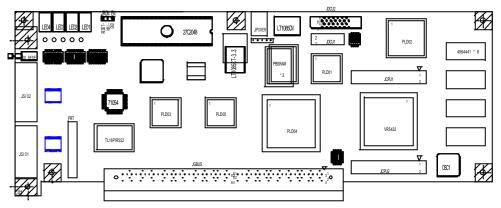

下図は RTE-VR5432-CB の主要な部品の物理的な配置です。ここでは、ボード上の主な構成部品について説明します。

ボード概観

## 5.1. リセット・スイッチ (SW\_RESET)

SW\_RESET は本ボード全体のリセット・スイッチです。このスイッチを押すと CPU を含む全ての回路がリセットされます。

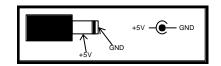

#### 5.2. 電源コネクタ (JPOWER)

JPOWER コネクタに供給する電源は、以下の通りです。

電圧:5V

電流: 2.0A(max)

適合コネクタ: Type A ( 5.5)

極性:

電源コネクタへは、付属の電源以外を接続しないでください。 また、JGBUS コネクタから電源を供給する場合は、JPOWER に電源を接続しないでください。

## 5.3. スイッチ1(SW1)

SW1 は、汎用の入力ポートのスイッチです。設定状態は、入力ポートから読み出すことが可能です(「7.4.4~SW1 読み出しポート(SW1 B800-0000H [Read Only])」参照)。ポートからの読み出し時、スイッチは、OFF で 1、ON で 0 の値になります。モニタ ROM を使用する場合には、一部を除き、割り当て済みです。モニタ ROM での割り付けは、以下の各章を参照し、使用環境に合わせて設定してご使用ください。

Multi を使用する場合、「11.1.2 SW1 の設定」を参照ください。

PARTNER を使用する場合、12.1.1 SW1 の設定」を参照ください。

# 5.4. スイッチ 2 (SW2)

SW2 は、本ボードの動作をハード的に切り替えるスイッチです。設定内容は入力ポートから 読み出すことが可能です (「7.4.5 SW2 読み出しポート(SW2 B800-1000H [Read Only])」を参照)。

| 番号 | 名称       | 出荷時の設定 | 機能                                                                                                                                  |  |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| 1  | FBOOT    | OFF    | CSO 空間に割り付ける資源を設定します。(通常:OFF)<br>OFF: CSO の空間はボード上の UV-EPROM が割り付けられす。<br>ON: CSO の空間は GBUS の GCS1-空間が割り付けられます。(「10.3 チップセレクト」参照)。  |  |

| 2  | TEST1    | OFF    | 常時、OFFに設定してください。                                                                                                                    |  |

| 3  | BCLK_LOW | OFF    | OSCI に実装されているオシレータの周波数を設定します。この設定値により ROM や I/O のウェイト数が切り替わります。<br>OFF:バスクロックが 33MHz を越える時に設定します。<br>ON:バスクロックが 33MHz 以下である時に設定します。 |  |

| 4  | DDDD     | OFF    | Write Data Rate を指定します。この設定に従って、VR54<br>の Config レジスタの設定が必要です。<br>OFF: DxxDxxDxxDxx<br>ON: DDDD                                     |  |

| 5  | TESET2   | OFF    | 常時、OFF に設定してください。                                                                                                                   |  |

| 6  | 未使用      | OFF    | 常時、OFFに設定してください。                                                                                                                    |  |

| 7  | 未使用      | OFF    | 常時、OFFに設定してください。                                                                                                                    |  |

| 8  | GCLK_LOW | OFF    | 常時、OFFに設定してください。                                                                                                                    |  |

## 5.5. スイッチ 3 (SW3)

SW3 は、ROM ソケットに搭載されている ROM の種類とバンクに関して設定します。

| 番号 | 信号名       | 出荷時の設定 | 機能                                                  |  |  |

|----|-----------|--------|-----------------------------------------------------|--|--|

| 1  | ROM_TYPE0 | OFF    | ROM の種類を設定します。                                      |  |  |

|    |           |        | [ROM_TYPE1,ROM_TYPE0 ]<br>[ OFF , OFF ]:モニタ ROM 使用時 |  |  |

| 2  | ROM_TYPE1 | OFF    | [ OFF , ON ]: 27C4096 使用時                           |  |  |

|    |           |        | [ ON , OFF ]:27C2048 使用時<br>[ ON , ON ]:27C1024 使用時 |  |  |

| 3  | BANK_DIS  | OFF    | ROM をバンクに分けて使用するかどうかを設定します。                         |  |  |

|    |           |        | モニタ ROM 使用時は、OFF に設定してください。<br>OFF: バンクに分けて使用       |  |  |

|    |           |        | ON: バンクに分けずに連続した領域として使用                             |  |  |

| 4  | 未使用       | OFF    | 常時、OFF に設定してください。                                   |  |  |

| 5  | 未使用       | OFF    | 常時、OFF に設定してください。                                   |  |  |

| 6  | 未使用       | OFF    | 常時、OFFに設定してください。                                    |  |  |

| 7  | MON64     | OFF    | モニタの種類を指定します。                                       |  |  |

|    |           |        | OFF: 32bit mode                                     |  |  |

|    |           |        | ON: 64bit mode                                      |  |  |

| 8  | LITTLE    | OFF    | ENDIAN を指定します。                                      |  |  |

|    |           |        | OFF: BIG                                            |  |  |

|    |           |        | ON: LITTLE                                          |  |  |

備考: ROM エミュレータを接続する場合は、BANK\_DIS を ON にして、ROM を連続して使用 する設定でご使用ください。

スイッチ 4 (SW4)

SW4 は、CPU のモードを設定するスイッチです。OFF で 1、ON で 0 です。

| SV  | W4  | DivMode[10] Ratio  | 備考(*は出荷時の設定) |  |

|-----|-----|--------------------|--------------|--|

| 1   | 2   | Divisione[10] Rano |              |  |

| ON  | ON  | 0: 2:1             |              |  |

| OFF | ON  | 1: 2.5:1           | *            |  |

| ON  | OFF | 2: 3:1             |              |  |

| OFF | OFF | 3: 4:1             |              |  |

SW4-3 は、常に OFF 固定です。

SW4-4 は、テスト用です。常に OFF でご使用ください。

# 5.6. スイッチ 5 (SW5)

SW5 は、CPU の端子に接続している本基板内の信号線を物理的にカットするためのスイッチです。出荷時全ての設定は、ON(接続された状態)になっています。通常は、出荷時の状態でご使用ください。

| 番号 | CPU 端子名 | 出荷時の設定 | 内部で使用している資源   |

|----|---------|--------|---------------|

| 1  | 未使用     | OFF    |               |

| 2  | INT2-   | ON     | GBUS O GINT1- |

| 3  | INT3-   | ON     | GBUS の GINT2- |

| 4  | INT4-   | ON     | GBUS Ø GINT3- |

## 5.7. 7SEG-LED, xxx-LED

LED は、各種の状態を示しています。表に内容を示します。4 つの 7SEG-LED は、起動時にモニタが使用しますが、その後、ユーザアプリケーションで自由に使用可能です。

| 名称    | 内容                       |

|-------|--------------------------|

| POWER | ボードに電源が供給されている時に点灯       |

| SRAM  | PB-SRAM 空間へのアクセス時に点灯します。 |

| DRAM  | SDARM 空間へのアクセス時に点灯します。   |

| LOCAL | LOCAL 空間へのアクセス時に点灯します。   |

| GBUS  | GBUS空間へのアクセス時に点灯します。     |

ボード LED ステータス

## 5.8. クロック・ソケット(OSC1)

OSC1 ソケットには、CPU に供給するクロック用のオシレータを実装します。OSC1 の出力は、3.3V にレベル変換されて、そのままの周波数が CPU に入力されています。(バスクロックに相当します) オシレータは、DIP8 ピンタイプ(ハーフタイプ)のものを使用します。

オシレータの足を切って実装する場合、足が短かすぎるとフレーム (外装)部分がソケットの端子とショートしてしまいますのでご注意願います。

#### 5.9. ROM ソケット

ROM ソケットには、標準で 256K バイト(128K × 16 ビット)の 40 ピン ROM が実装されています。変更する場合は、27C1024,27C2048,27C4096 タイプで、アクセス・タイムが 120ns 以下のものをご使用ください。ROM の種類を変更する場合や、ROM エミュレータを接続する場合は、SW3 の再設定が必要です。(「5.5 スイッチ 3 (SW3)」を参照)

# 5.10. シリアル・コネクタ (JSIO1,2)

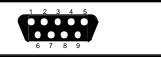

JSIO1,2 コネクタは、シリアル / パラレル・コントローラ ( TL16PIR552 ) によって制御される RS-232C 用のコネクタです。コネクタの形状は、PC/AT で用いられる一般的な D-SUB9 ピンの RS-232C コネクタ ( オス ) で、全ての信号は RS-232C レベルに変換されています。コネクタの ピン番号と内容は以下の通りです。また表には、ホストと接続する場合の接続信号について、ホスト側が D-SUB9 ピンの場合と D-SUB25 ピンの場合の布線をそれぞれ示してあります ( 一般的なクロスケーブルの布線です )。

JSIO1,2 ピン配置図

| JSIOx ピン | 信号名      | 入出力 | ホストの接続ピン番号 |         |

|----------|----------|-----|------------|---------|

| JSIOX C2 | поп      | ЛШЛ | D-SUB9     | D-SUB25 |

| 1        | DCD      | 入力  |            |         |

| 2        | RxD (RD) | 入力  | 3          | 2       |

| 3        | TxD (SD) | 出力  | 2          | 3       |

| 4        | DTR (DR) | 出力  | 1, 6       | 6, 8    |

| 5        | GND      |     | 5          | 7       |

| 6        | DSR (ER) | 入力  | 4          | 20      |

| 7        | RTS (RS) | 出力  | 8          | 5       |

| 8        | CTS (CS) | 入力  | 7          | 4       |

| 9        | RI       | 入力  |            |         |

JSIO1.2 コネクタ信号表

# 5.11. パラレル・コネクタ (JPRT)

JPRT コネクタは、シリアル / パラレル・コントローラ (TL16PIR552)によって制御されるプリンタ用のコネクタです。コネクタは 26 ピンのヘッダピンですので、一般的なプリンタ・コネクタとして使用するには変換ケーブルが必要です。コネクタのピン番号と内容は以下の通りです。

2

4

6

8

10

12

14

16

18

20

22

24

26

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

JPRT ピン配置図

| JPRT ピン                     | 信号名        | 入出力 | 備考        |

|-----------------------------|------------|-----|-----------|

| 1                           | STB-       | 出力  | 10K プルアップ |

| 2                           | AUTO_FD-   | 出力  | 10K プルアップ |

| 3                           | D0         | 出力  | 10K プルアップ |

| 4                           | ERROR-     | 入力  | 10K プルアップ |

| 5                           | D1         | 出力  | 10K プルアップ |

| 6                           | INIT-      | 出力  | 10K プルアップ |

| 7                           | D2         | 出力  | 10K プルアップ |

| 8                           | SELECT_IN- | 出力  | 10K プルアップ |

| 9                           | D3         | 出力  | 10K プルアップ |

| 11                          | D4         | 出力  | 10K プルアップ |

| 13                          | D5         | 出力  | 10K プルアップ |

| 15                          | D6         | 出力  | 10K プルアップ |

| 17                          | D7         | 出力  | 10K プルアップ |

| 19                          | ACK-       | 入力  | 10K プルアップ |

| 21                          | BUSY       | 入力  | 10K プルアップ |

| 23                          | PE         | 入力  | 10K プルアップ |

| 25                          | SELECT     | 入力  | 10K プルアップ |

| 26                          | NC         |     | 未使用       |

| 10,12,14,16,<br>18,20,22,24 | GND        |     |           |

JPRT コネクタ信号表

## 5.12. ROM エミュレータ用テストピン (JROM-EML)

JROM-EML は、ROM エミュレータを接続する際に使用するテストピンです。下記の制御信号が入力できます。表に信号名と機能を示します。

| 信号名           | 入出力 | 機能                                                                                |

|---------------|-----|-----------------------------------------------------------------------------------|

| RESET-<br>(1) | 入力  | Low レベル入力により、ボード全体がリセットされます。<br>ROM エミュレータからのリセット要求信号を接続します。<br>1K でブルアップされています。  |

| NMI-<br>(2)   | 入力  | Low レベル入力により、CPUに NMI が入ります。<br>ROM エミュレータからの NMI 要求信号を接続します。<br>1K でプルアップされています。 |

| GND(3)        |     | GND。ROM エミュレータの GND と接続します。                                                       |

JROM\_EM 端子の機能

# 5.13. ICE コネクタ#1 (JDCU1)

ICE を接続するためのコネクタです。以下の信号が接続されています。

| ピン番号 | 信号名      | ピン番号 | 信号名 |

|------|----------|------|-----|

| 1    | NC.      | 2    | GND |

| 3    | DDI      | 4    | GND |

| 5    | DDO      | 6    | GND |

| 7    | DMS      | 8    | GND |

| 9    | DCK      | 10   | GND |

| 11   | TRISTATE | 12   | GND |

| 13   | /BKTGIO  | 14   | GND |

| 15   | TRCDATA0 | 16   | GND |

| 17   | TRCDATA1 | 18   | GND |

| 19   | TRCDATA2 | 20   | GND |

| 21   | TRCDATA3 | 22   | GND |

| 23   | TRCEND   | 24   | GND |

| 25   | TRCCLK   | 26   | GND |

JDCU1 コネクタ信号

基板側のコネクタ : サムテック社 FTSH-113-01-L-DV

## 5.14. ICE コネクタ#2(JDCU2)

ICE を接続するためのコネクタで、RTE-TP 系の ICE が接続できます。以下の信号が接続されています。

| ピン番号 | 信号名      | ピン番号 | 信号名   |

|------|----------|------|-------|

| A1   | TRCCLK   | B1   | GND   |

| A2   | TRCDATA0 | B2   | GND   |

| A3   | TRCDATA1 | В3   | GND   |

| A4   | TRCDATA2 | B4   | GND   |

| A5   | TRCDATA3 | B5   | GND   |

| A6   | TRCEND   | В6   | GND   |

| A7   | DDI      | В7   | GND   |

| A8   | DCK      | В8   | GND   |

| A9   | DMS      | В9   | GND   |

| A10  | DDO      | B10  | GND   |

| A11  | /DRST    | B11  | NC.   |

| A12  | /BKTGIO  | B12  | NC.   |

| A13  | NC.      | B13  | +3.3V |

JDCU2 コネクタ信号

基板側のコネクタ : KEL 社 8830E-026-170S

## 5.15. JGBUS コネクタ (JGBUS)

拡張用の 32Bit データ幅のバスコネクタです。詳細は「10 GBUS 個別仕様」、14 APPEDIX.C GBUS 共通仕様」を参照してください。

# 5.16. CPU コネクタ(JCP1,2)

CPU コネクタの信号は、VR5432 と直結した信号です。各信号は、ボード内部で使用していますので、JCPU から信号を引き出す場合は、注意が必要です。

| JCPU<br>ピン番号 | 信号名     | JCPU<br>ピン番号 | 信号名     |

|--------------|---------|--------------|---------|

| 1            | +5V     | 2            | GND     |

| 3            | SYSAD31 | 4            | SYSAD30 |

| 5            | SYSAD29 | 6            | SYSAD28 |

| 7            | SYSAD27 | 8            | SYSAD26 |

| 9            | SYSAD25 | 10           | SYSAD24 |

| 11           | +5V     | 12           | GND     |

| 13           | SYSAD23 | 14           | SYSAD22 |

| 15           | SYSAD21 | 16           | SYSAD20 |

| 17           | SYSAD19 | 18           | SYSAD18 |

| 19           | SYSAD17 | 20           | SYSAD16 |

| 21           | +3.3V   | 22           | GND     |

| 23           | SYSAD15 | 24           | SYSAD14 |

| 25           | SYSAD13 | 26           | SYSAD12 |

| 27           | SYSAD11 | 28           | SYSAD10 |

| 29           | SYSAD9  | 30           | SYSAD8  |

| 31           | +3.3V   | 32           | GND     |

| 33           | SYSAD7  | 34           | SYSAD6  |

| 35           | SYSAD5  | 36           | SYSAD4  |

| 37           | SYSAD3  | 38           | SYSAD2  |

| 39           | SYSAD1  | 40           | SYSAD0  |

| 41           | +2.7V   | 42           | GND     |

| 43           | /NMI    | 44           | /INT0   |

| 45           | /INT1   | 46           | /INT2   |

| 47           | /INT3   | 48           | /INT4   |

| 49           | +2.7V   | 50           | GND     |

| 51           | no use  | 52           | no use  |

JCPU1 コネクタ

| JCPU<br>ピン番号 | 信号名      | JCPU<br>ピン番号 | 信号名        |

|--------------|----------|--------------|------------|

| 1            | +5V      | 2            | GND        |

| 3            | SYSCMD4  | 4            | SYSCMD3    |

| 5            | SYSCMD2  | 6            | SYSCMD1    |

| 7            | SYSCMD0  | 8            | no use     |

| 9            | no use   | 10           | no use     |

| 11           | +5V      | 12           | GND        |

| 13           | /EVALID  | 14           | /SYSRESET  |

| 15           | /EREQ    | 16           | /PMASTER   |

| 17           | /EOK     | 18           | /PVALID    |

| 19           | /PREQ    | 20           | no use     |

| 21           | +3.3V    | 22           | GND        |

| 23           | SYSADC3  | 24           | SYSAD2     |

| 25           | SYSADC1  | 26           | SYSADC0    |

| 27           | SYSCLK2  | 28           | no use     |

| 29           | +3.3V    | 30           | GND        |

| 31           | JTDO     | 32           | JTDI       |

| 33           | JTCK     | 34           | JTMS       |

| 35           | TRISTATE | 36           | /COLDRESET |

| 37           | ENDIAN   | 38           | no use     |

| 39           | +2.7V    | 40           | GND        |

| 41           | DIVMODE0 | 42           | DIVMODE1   |

| 43           | TRCEND   | 44           | TRCDATA3   |

| 45           | TRCDATA2 | 46           | TRCDATA1   |

| 47           | TRCDATA0 | 48           | /BKTGIO    |

| 49           | +2.7V    | 50           | TRCCLK     |

| 51           | no use   | 52           | no use     |

JCPU2

コネクタ: ヒロセ社 基板側 FX2-52P-1.27SV, 相手側 FX2-52S-1.27SV

#### 6. ホスト PC との接続

#### 6.1. RS-232C 接続

モニタ ROM を使用して、ホストマシンとシリアルで接続する際の手順は以下の通りです。 添付品の RS-232C ケーブルと、電源を用意してください。

ボード上のスイッチの設定と確認を行ってください。SW1のボーレイトの設定は、必ず実施ください。(「11.1.2 SW1の設定」、「12.1.1 SW1の設定」の各項を参照ください。)

JSIO1 コネクタ(CH0)とホストマシンを RS-232C ケーブルで接続し、JPOWER コネクタへ電源を供給してください。ボードの POWER-LED が点灯し、モニタの起動を示す 7seg-LED の表示がなされることを確認してください。

LED が点灯しない場合は、すぐに電源を切り接続を確認してください。

ホストマシンでデバッガを起動し、RS-232C 経由でコネクトします。エラーが発生する場合には、シリアル・ケーブルやスイッチ (特にボーレート)の設定等に間違いがないかを確認してください。デバッガの起動方法や手順は、各デバッガのマニュアルを参照ください。

ボードは絶縁物の上に設置してください。通電中に、導電物を 基板に接触させると故障の原因になります。

## 7. ハードウェア・リファレンス

ここでは、RTE-VR5432-CB ボードのハードウェア仕様について説明します。

#### 7.1. リセット

リセットは下記に示した要因で発生します。これらは CPU に対してコールドリセットとして扱われ、ボード上の制御回路へのシステム・リセットとなります。

- ・パワーオン・リセット:ボードの電源 ON 時に発生します。

- ・**リセット・スイッチ**:ボードに用意されているリセット・スイッチ(SW RST)により発生します。

- ・GBUS・リセット: JGBUS コネクタからのリセット要求です。

- ・JROM\_リセット: JROM\_EMLコネクタの1番端子(RESET-)からの入力です(「5.12 ROM エミュレータ用テストピン(JROM-EML)」を参照)。

- ・DCU・リセット: ICE からのリセット要求です。(「5.12 ROM エミュレータ用テストピン (JROM-EML)」参照)

#### 7.2. 割込み

CPU 外部からの割込み要因は、以下の通りです。

| 割込み   | 要因             | 参照 (章) |

|-------|----------------|--------|

| NMI-  | JROM_EML(NMI-) | 5.12   |

| INT0- | PIC INT0M      | 7.4.9  |

| INT1- | PIC INT1M      | 7.4.9  |

| INT2- | GBUS_INT1-     |        |

| INT3- | GBUS_INT2-     |        |

| INT4- | GBUS_INT3-     |        |

メモ】モニタ環境下で割込みを使用する場合のプログラミング方法は、「13 APPEDIX.C 割込みプログラミング」を参照してください。

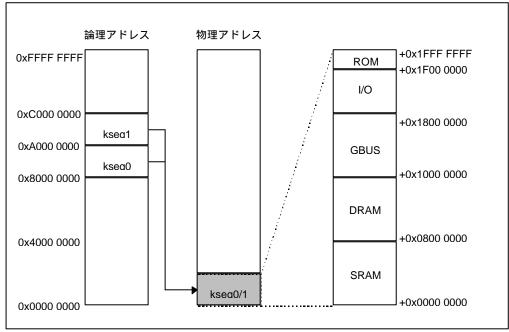

#### 7.3. アドレス・マップ

ボードのアドレス割り付けは、以下の通りです。

アドレス・マップ

リモート・モニタを使用してプログラム実行する場合には、TLB マップを使用しないカーネル空間 8000-0000H ~ BFFF-FFFFH で行ないます。キャッシュを使用する場合には 8000-0000H , 使用しない場合には A000-0000H を、物理アドレスに加算して論理アドレスを決定します。

#### 7.3.1. SRAM 空間 (0000-0000H~07FF-FFFFH)

SRAM 空間には、32K-byte \* 32bit の PB-SRAM を 2 個実装し、256K-Byte の容量を搭載しています。最大バスクロックまで 0 ウェイトでアクセス可能ですが、 $0 \sim 3$ clk のウェイトを入れてのウェイトエミュレーション可能です。(「7.4.1 SRAM コントローラ(SRAMC B800-6000[Read/Write])」を参照)。

空間内のアドレス線の上位ビットはデコードしていませんので、256K-Byte おきにイメージが発生します。キャッシュ/非キャッシュどちらの空間でもアクセスできます。

## 7.3.2. DRAM 空間 (0800-0000H~0FFF-FFFFH)

DARM 空間には、4M \* 4bit \* 4bank の SDRAM を 8 個実装し、64M-Byte の容量を搭載しています。使用に先立ち、SDRAM への設定が必要です。(「7.4.2 DRAM コントローラ ( DRAMC B800-5000[Read/Write] )」を参照 )。空間内のアドレス線の上位ビットはデコードしていませんので、64M-Byte おきにイメージが発生します。キャッシュ / 非キャッシュどちらの空間からでもアクセスできます。

# 7.3.3. GBUS 空間 (1000-0000H~17FF-FFFFH)

GBUS 空間は GBUS へのアクセス空間がマップされています。詳細には、「10~GBUS~@別仕様」を参照してください。本ボードからは、キャッシュ / 非キャッシュどちらの空間からでもアクセスできますが、アクセス先の資源によって使い分けください。

#### 7.3.4. I/O 空間(1800-0000H~1EFF-FFFFH)

I/O 空間はボード上の各機能を制御するための I/O デバイスが割り付けられている空間 (  $oldsymbol{arphi}$

モリ・マップド I/O )です。I/O マップなどの詳細については「7.4~I/O 詳細」を参照してください。非キャッシュ空間でアクセスします。

#### 7.3.5. ROM 空間 (1F00-0000H~1FFF-FFFFH)

ROM 空間は 128K バイト(64KWord×16Bit ) 256K バイト(128Kword×16Bit ) 512K バイト(256KWord×16Bit )のいずれかで、アクセスタイムを 120nS 以下の UV-EPROM が実装できます。搭載する ROM の種類と使用方法は、SW3 で設定します(「5.5 スイッチ 3(SW3)」参照)。 アドレス線の上位ビットはデコードしていませんので、ROM の容量おきにイメージが現れます。 ROM の Wait 数は、SW2-3(BCLK\_LOW)の設定により異なりますが、上限周波数において、120nS 以上のアクセスタイムを確保します。

キャッシュ/非キャッシュどちらの空間からでもアクセスできます。

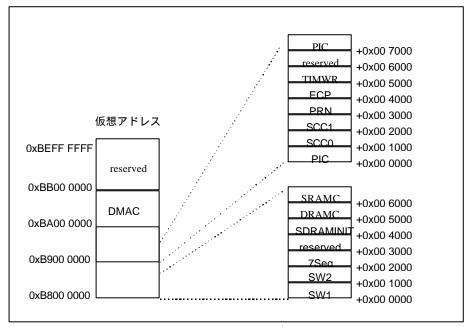

#### 7.4. I/O 詳細

メモリ空間にマップされた I/O デバイスで、メモリアクセスコントローラ、 DUART/LPT, TIMER、割込みコントローラなどがあります。各 I/O の割り付けは以下の通りです。

I/O マップ

これらの I/O はカーネル非キャッシュ空間でのアクセスを前提としているため、以降の説明では論理アドレスを用います。

【 メモ 】 I/O デバイスに接続されているデータバスは特に明記がない場合、D0 を LSB として接続されていますので、バイト、およびハーフワードのアクセス時にはエンディアンを考慮する必要があります。 ビッグ・エンディアンでバイトアクセスする場合には、バイト・オフセットとして+3 を、ハーフワードでアクセスする場合には、バイト・オフセットとして+2 をアドレスに加算してアクセスしてください。

## 7.4.1. SRAM コントローラ (SRAMC B800-6000 [Read/Write])

SWAIT レジスタは、SRAM 空間のウェイト制御を行ないます。このレジスタによってリードサイクルに 0~3 ウェイトが設定できます。レジスタ割り付けは下表の通りです。

| 論理アドレス             | レジスタ        | データバス |    |        |        |

|--------------------|-------------|-------|----|--------|--------|

|                    |             | D3    | D2 | D1     | D0     |

| <b>B800</b> -6000H | SRAMC SWAIT | 0     | 0  | SWAIT1 | SWAIT0 |

SWAIT[1..0]: SRAM リード時のウェイト数を設定します。

| SW<br>1 | AIT 0 | SRAM リード・ウェイト数 |         |

|---------|-------|----------------|---------|

| 0       | 0     | 0              | 推奨値     |

| 0       | 1     | 1              |         |

| 1       | 0     | 2              |         |

| 1       | 1     | 3              | (リセット値) |

# 7.4.2. DRAM コントローラ (DRAMC B800-5000[Read/Write])

DRAMC は SDRAM のアクセス条件の設定を行ないます。レジスタ割り付けは下表の通りです。

| 論理アドレス             | レジスタ      |    | デーク  | タバス  |      |

|--------------------|-----------|----|------|------|------|

|                    |           | D3 | D2   | D1   | D0   |

| <b>B800</b> -5000H | DRAMC RCD | 0  | 0    | RCD1 | RCD0 |

| -5010H             | DRAMC RP  | 0  | 0    | RP1  | RP0  |

| -5020H             | DRAMC RC  | 0  | RC2  | RC1  | RC0  |

| -5030H             | DRAMC RRC | 0  | RRC2 | RRC1 | RRC0 |

| -5040H             | DRAMC RAS | 0  | RAS2 | RAS1 | RAS0 |

| -5050H             | DRAMC LAT | 0  | 0    | LAT1 | LAT0 |

| -5060H             | DRAMC RSC | 0  | 0    | RSC1 | RSC0 |

| -5070H             | DRAMC AP  | 0  | 0    | 0    | AP   |

RCD[1..0]: SDRAM のパラメータ:tRCD(Delay ACT to READ/WRITE)を設定します。

| RO | CD | tRCD     |         |

|----|----|----------|---------|

| 1  | 0  | tkCD     | 備考      |

| 0  | 0  |          |         |

| 0  | 1  |          |         |

| 1  | 0  | 2 SYSCLK | 推奨値     |

| 1  | 1  | 3 SYSCLK | (リセット値) |

# 【メモ】 推奨値でご使用ください。推奨値以外の設定での動作は保証しません。

RP[1..0]: SDRAM のパラメータ:tRP(PRE to ACT/REF)を設定します。

| R | RP. | tRP         |         |

|---|-----|-------------|---------|

| 1 | 0   | tkr         | 備考      |

| 0 | 0   | <del></del> |         |

| 0 | 1   |             |         |

| 1 | 0   | 2 SYSCLK    | 推奨値     |

| 1 | 1   | 3 SYSCLK    | (リセット値) |

# 【メモ】 推奨値でご使用ください。推奨値以外の設定での動作は保証しません。

RC[2..0]: SDRAM のパラメータ:tRC(ACT to REF/ACT)を設定します。

| 2 | RC<br>1 | 0 | tRC      | 備考      |

|---|---------|---|----------|---------|

| 0 | 0       | 0 |          |         |

| 0 | 0       | 1 |          |         |

| 0 | 1       | 0 |          |         |

| 0 | 1       | 1 |          |         |

| 1 | 0       | 0 |          |         |

| 1 | 0       | 1 | 5 SYSCLK | 推奨値     |

| 1 | 1       | 0 | 6 SYSCLK |         |

| 1 | 1       | 1 | 7 SYSCLK | (リセット値) |

# メモ】 推奨値でご使用下さい。推奨値以外の設定での動作は保証しません。

RRC[2..0]: SDRAM のパラメータ:tRRC(REF to REF/ACT)を設定します。

|   | RRC |   | tRRC     |         |

|---|-----|---|----------|---------|

| 2 | 1   | 0 | IRRC     | 備考      |

| 0 | 0   | 0 |          |         |

| 0 | 0   | 1 |          |         |

| 0 | 1   | 0 | -        |         |

| 0 | 1   | 1 |          |         |

| 1 | 0   | 0 |          |         |

| 1 | 0   | 1 |          |         |

| 1 | 1   | 0 | 6 SYSCLK | 推奨値     |

| 1 | 1   | 1 | 7 SYSCLK | (リセット値) |

# メモ】 推奨値でご使用ください。推奨値以外の設定での動作は保証しません。

RAS[2..0]: SDRAM のパラメータ:tRC(ACT to PRE)を設定します。

|   | RAS |   | tRAS     |         |

|---|-----|---|----------|---------|

| 2 | 1   | 0 | tras     | 備考      |

| 0 | 0   | 0 |          |         |

| 0 | 0   | 1 |          |         |

| 0 | 1   | 0 |          |         |

| 0 | 1   | 1 |          |         |

| 1 | 0   | 0 | 4SYSCLK  | 推奨値     |

| 1 | 0   | 1 |          |         |

| 1 | 1   | 0 |          |         |

| 1 | 1   | 1 | 7 SYSCLK | (リセット値) |

# メモ】 推奨値でご使用ください。推奨値以外での設定での動作は保証しません。

LAT[1..0]: SDRAM のパラメータ:tLAT(/CAS latency)を設定します。

| 1 | AT<br>0 | tLAT     | 備考      |

|---|---------|----------|---------|

| 0 | 0       |          |         |

| 0 | 1       |          |         |

| 1 | 0       | 2 SYSCLK | 推奨値     |

| 1 | 1       | 3 SYSCLK | (リセット値) |

# 【メモ】 推奨値でご使用ください。推奨値以外の設定での動作は保証しません。

RSC[1..0]: SDRAM のパラメータ:tRSC(Mode Register Set Cycle Time)を設定します。

| R. | SC | tRSC     |         |

|----|----|----------|---------|

| 1  | 0  | iksc     | 備考      |

| 0  | 0  |          |         |

| 0  | 1  | -1       |         |

| 1  | 0  | 2 SYSCLK | 推奨値     |

| 1  | 1  | 3 SYSCLK | (リセット値) |

# 【メモ】 推奨値でご使用ください。推奨値以外の設定での動作は保証しません。

AP: SDRAM のオートプリチャージ機能を使用するかどうかを指定します。

| AP | オートプリチャージ | 備考    |  |  |

|----|-----------|-------|--|--|

| 0  | 使用する。     |       |  |  |

| 1  | 使用しない     | リセット値 |  |  |

# 7.4.3. DRAM 初期化ポート (DRAM\_INIT B800-4000H[Write Only])

DRAMCの設定値に基づき、SDRAM を初期化します。データは、Don't Care です。出力することで、SDARM の Mode Register Set Command を発行します。

このポートは、ポートへ設定したパラメータを SDRAM に書き込むためのものです。全てのパラメータをポートに設定した後、最後にこのポートへ出力してください。

## 7.4.4. SW1 読み出しポート(SW1 B800-0000H [Read Only])

SW1 の状態を読み出すためのポートです。データ・フォーマットを下表に示します。

| 加田マドレフ   | データバス  |         |         |        |        |        |        | 内容     |       |

|----------|--------|---------|---------|--------|--------|--------|--------|--------|-------|

| 物理アドレス   | D7     | D6      | D5      | D4     | D3     | D2     | D1     | D0     | 內谷    |

| В800000Н | SW1-8  | SW1-7   | SW1-6   | SW 1-5 | SW 1-4 | SW 1-3 | SW1-2  | SW 1-1 | 0=ON  |

| 入力       | 3W 1-0 | 3 W 1-7 | 3 W 1-0 | 3W 1-3 | 3W 1-4 | 3W 1-3 | 3W 1-2 | SW 1-1 | 1=OFF |

SW1-1 が SW1 の"1"のスイッチに、SW1-8 が SW1 の"8"のスイッチに対応しています。また、該当するビットのスイッチが ON で 0 が、OFF で 1 が読み出されます。SW3 は、モニタの動作設定用のスイッチとして使用しています。設定方法は、「11.1.2 SW1 の設定」、「12.1.1 SW1 の設定」の各項を参照してください。

## 7.4.5. SW2 読み出しポート(SW2 B800-1000H [Read Only])

SW2 の状態を読み出すためのポートです。データ・フォーマットを下表に示します。

| 4m TB - 7 10 1 - 7 | データバス |       |       |       |       |       |       | d 72  |               |

|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| 物理アドレス<br>         | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    | 内容            |

| B801000H<br>入力     | SW2-8 | SW2-7 | SW2-6 | SW2-5 | SW2-4 | SW2-3 | SW2-2 | SW2-1 | 0=ON<br>1=OFF |

SW2-1 が SW2 の"1"のスイッチに、SW2-8 が SW2 の"8"のスイッチに対応しています。また、該当するビットのスイッチが ON で 0 が、OFF で 1 が読み出されます。SW2 は、ハードウェアの動作を切り替えます。それぞれのスイッチの機能は、「5.4 スイッチ 2 (SW2)」を参照してください。

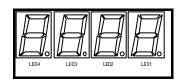

## 7.4.6. 7 セグメント LED 表示データ出力ポート(7SEG-LED B800-2000 [Write Only])

4 つの 7 セグメント LED に表示するデータを設定します。データ・フォーマットを下表に示します。該当するビットに 0 を設定すると対応するセグメントが点灯します。

| *^ TH - 1        | データ  |            |            |            |            |            |            | 4.8        |      |

|------------------|------|------------|------------|------------|------------|------------|------------|------------|------|

| 論理アドレス           | D731 | D630       | D529       | D428       | D327       | D226       | D125       | D024       | 内容   |

| B800-2000H<br>出力 | LED1 | LED1<br>-G | LED1<br>-F | LED1<br>-E | LED1<br>-D | LED1<br>-C | LED1<br>-B | LED1<br>-A |      |

| B800-2001H       | LED2 | LED2       | LED2       | LED2       | LED2       | LED2       | LED2       | LED2       | 0=点灯 |

| 出力               | -DP  | -G         | -F         | -E         | -D         | -C         | -B         | -A         |      |

| B800-2002H       | LED3 | LED3       | LED3       | LED3       | LED3       | LED3       | LED3       | LED3       | 1=消灯 |

| 出力               | -DP  | -G         | -F         | -E         | -D         | -C         | -B         | -A         |      |

| B800-2003H       | LED4 | LED4       | LED4       | LED4       | LED4       | LED4       | LED4       | LED4       |      |

| 出力               | -DP  | -G         | -F         | -E         | -D         | -C         | -B         | -A         |      |

7セグメント LED のビット対応は、下図の通りです。

# 7.4.7. シリアル / パラレル I/O(SCC0/1, LPT B900-1000 ~ B900-4000[Read/Write])

UART/PRINTER として TEXAS INSTRUMENTS 製の TL16PIR552(DUAL UART WITH 1284 PARALLEL PORT)LSI を使用しています。TL16PIR552 は、UART を 2 チャンネル、IEEE1284 準拠の双方向プリンタ・ポートを 1 チャンネル備えており、UART の送受信部には 16 キャラクタ分の FIFO バッファを持ち、RTS/CTS フローを自動的に制御する機能を備えているため、最小限の割込みでオーバーラン・エラーを押さえられます。

TL16PIR552 の各レジスタは、表のように割り付けられています。各レジスタの機能については、TL16PIR552 のマニュアルを参照してください(TL16PIR552 のマニュアルは米国 TEXAS INSTRUMENTS 社のホームページ(http://www.ti.com/)の TI&MEのコーナーで入手可能です)。

| アドレス                  | 機能              | 読み出し           | 書き込み          |

|-----------------------|-----------------|----------------|---------------|

| B900-1000             | UART-CH#0       | RBR/DLL        | THR/DLL       |

| B900-1010             |                 | IER/DLM        | IER/DLM       |

| B900-1020             |                 | IIR            | FCR           |

| B900-1030             |                 | LCR            | LCR           |

| B900-1040             |                 | MCR            | MCR           |

| B900-1050             |                 | LSR            | LSR           |

| B900-1060             |                 | MSR            | MSR           |

| B900-1070             |                 | SCR            | SCR           |

| B900-2000             | UART-CH#1       | RBR/DLL        | THR/DLL       |

| B900-2010             |                 | IER/DLM        | IER/DLM       |

| B900-2020             |                 | IIR            | FCR           |

| B900-2030             |                 | LCR            | LCR           |

| B900-2040             |                 | MCR            | MCR           |

| B900-2050             |                 | LSR            | LSR           |

| B900-2060             |                 | MSR            | MSR           |

| B900-2070             |                 | SCR            | SCR           |

| B900-3000             | PRINTER(PPCS-)  | DATA           | DATA/ECPAFIFO |

| B900-3010             |                 | DSR            |               |

| B900-3020             |                 | DCR            | DCR           |

| B900-3030             |                 | EPPADDR        | EPPADDR       |

| B900-3040 ~ B900-3070 |                 | EPPDATA        | EPPDATA       |

| B900-4000             | PRINTER(ECPCS-) | PPDATAFIFO/    | PPDATAFIFO/   |

|                       |                 | TESTFIFO/CNFGA | TESTFIFO      |

| B900-4010             |                 | CNFGB          |               |

| B900-4020             |                 | ECR            | ECR           |

TL16PIR552 レジスタ配置

TL16PIR552のXIN入力には16MHzのクロックが接続されています。

UART-CH#0、UART-CH#1、PRINTER の各割込みは PIC を介して、CPU の割込みに接続することが可能です。

UART-CH#0 はボードのリアパネルにある JSIO1 コネクタに、UART-CH#1 は JSIO2 コネクタ、PRINTER は JPRT に接続しています。また、UART-CH#0 はデバッガをシリアル通信で用いる場合に使用され、その時の割込みは、PIC を通して、INTO を使用します。

TL16PIR552は、システム・リセットによってリセットされます。

注意:モニタを使用中は、UART-CH#0の内容は変更しないでください。

## 7.4.8. タイマ (Timer B900-5000[Read/Write])

タイマは NEC 製の uPD71054 を使用しています。uPD71054 は Intel 製の i8254 と互換であり、3 つのタイマカウンタを持っています。これらのタイマにより、各種の制御を行なっています。uPD71054 の各レジスタは、表の通りに割り当てられています。

| 論理アドレス    | レジスタ  | 補足    |

|-----------|-------|-------|

| B900-5000 | PCNT0 | タイマ 0 |

| B900-5010 | PCNT1 | タイマ 1 |

| B900-5020 | PCNT2 | タイマ 2 |

| B900-5030 | PCNTL | 制御    |

各レジスタの機能については、 uPD71054 のマニュアルを参照ください。 タイマは以下のように使用されます。

| タイマ | クロック | モード | 用途          |         |

|-----|------|-----|-------------|---------|

| 0   | 2MHz | 2   | タイマ割込み 0    | モニタで使用  |

| 1   | 2MHz | 2   | タイマ割込み 1    | ユーザで使用可 |

| 2   | 2MHz | 2   | DRAM リフレッシュ |         |

**注意:**モニタを使用中は、タイマ O の内容は変更しないでください。

## 7.4.9. 割込みコントローラ (PIC B900-0000[Read/Write])

PIC は、割込みの制御を行ないます。レジスタ割り付けは下表の通りです。

| 論理アドレス         | レジスタ      | データバス |      |      |      |      |      |      |      |

|----------------|-----------|-------|------|------|------|------|------|------|------|

| <b>神程</b> クトレス |           | D7    | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| B900-0000      | PIC INTOM | IM07  | IM06 | IM05 | IM04 | IM03 | IM02 | IM01 | IM00 |

| B900-0010      | PIC INT1M | IM17  | IM16 | IM15 | IM14 | IM13 | IM12 | IM11 | IM10 |

| B900-0020      | PIC INTR  | IR7   | IR6  | IR5  | IR4  | IR3  | IR2  | IR1  | IR0  |

| B900-0030      | PIC INTEN | 0     | 0    | 0    | 0    | 0    | 0    | INT1 | INT0 |

|                |           |       |      |      |      |      |      | EN   | EN   |

INTOM,INT1M レジスタはそれぞれINTO,INT1に入力する割込みをマスクします。IM0x, IM1xのビットが"1"の時にイネーブルとなり、複数ビットを選択した場合にはそれぞれの OR で割込みがアクティブとなります。

INTR レジスタは割込みステータスで、割込み要求がある場合に"1"が読み出せます。これはマスク状態に関係ありません。またエッジ割込み要求の解除(クリア)には、このレジスタの対応ビットに"1"を書き込みます。

IM0[0..7],IM1[0..7].IR[0..7]の各ビットに割り付けられている割込み要因は以下の通りです。

| IM0,IM1,IR | 割込み要因         | 要求レベル       |

|------------|---------------|-------------|

| 0          | タイマ0(モード2)    | エッジ (立ち上がり) |

| 1          | シリアル 0        | レベル (High)  |

| 2          | GBUS-INT0-    | レベル (Low)   |

| 3          | BUS ERROR     | レベル (Low)   |

| 4          | タイマ1(モード2)    | エッジ (立ち上がり) |

| 5          | シリアル 1        | レベル (High)  |

| 6          | パラレル ( プリンタ ) | エッジ (立ち上がり) |

| 7          | DMAC INTREQ-  | レベル(Low)    |

INTEN レジスタは、INTO,INT1への割込みの有効/禁止を制御します。

INTENO: INTO を制御します。このビットでINTOをハード的に禁止することができます。この時、INTO端子の状態はHigh レベルとなります。

| INTEN0 | INT0  |         |

|--------|-------|---------|

| 0      | 禁止する  | (リセット値) |

| 1      | 有効にする |         |

INTEN1: INT1 を制御します。このビットで INT0 をハード的に禁止することができます。この時、INT1 端子の状態は High レベルとなります。

| INTEN 1 | INT1  |         |

|---------|-------|---------|

| 0       | 禁止する  | (リセット値) |

| 1       | 有効にする |         |

**注意:**モニタを使用中は、INT0関連の内容は変更しないでください。

## 7.4.10. DMA コントローラ

GBUS からの DMA 要求に対し、GBUS 資源間で DMA 転送を行うコントローラです。全部で 4 チャンネルの DMA コントローラがあります。

DMA 転送は常に 2 サイクル( 読みだしサイクルと書き込みサイクル )で行われます。また、バースト・サイクルはサポートしていません。

7.4.10.1.DMA チャンネル 0 制御ポート ( DMACNT0 BA00-0000[Read/Write] )

7.4.10.2.DMA チャンネル 1 制御ポート ( DMACNT1 BA00-0080[Read/Write] )

7.4.10.3.DMA チャンネル 2 制御ポート ( DMACNT2 BA00-0100[Read/Write] )

7.4.10.4.DMA チャンネル 3 制御ポート ( DMACNT3 BA00-0180[Read/Write] )

| Bit | 信号名                  | RST | 機能                                                                       |

|-----|----------------------|-----|--------------------------------------------------------------------------|

| 0   | DMA_EN <sup>*1</sup> | 0   | 0:DMA 停止                                                                 |

|     |                      |     | 1:DMA 実行                                                                 |

| 1   | $TC^{*2}$            | 0   | 0:DMA 転送未終了                                                              |

| -   |                      |     | 1:DMA 転送終了                                                               |

| 2   | DMA_SINGLE*3         | х   | 0:連続して GBUSを使用する                                                         |

| 3   | *4                   |     | 1:1 転送ごとに GBUS を一旦手放す<br>0:ハードウェアの DMA 要求線に従って DMA 転送を行う                 |

| 3   | SOFT_DREQ*4          | х   | 1:ハードウェアの DMA 要求線に促って DMA 転送を行う<br>1:ハードウェアの DMA 要求線がインアクティブでも DMA 転送を行う |

| 4   | DATA_SIZE[0] *5      | х   | DATA_SIZE[1:0]で転送するデータのサイズを設定します                                         |

| 5   | DATA_SIZE[1] *5      | х   |                                                                          |

| 6   | 未使用                  | х   |                                                                          |

| 7   | 未使用                  | x   |                                                                          |

| 8   | DST_CD[0] *6         | х   | DST_CD[1:0]で、転送先アドレスの増減を設定します                                            |

| 9   | DST_CD[1] *6         | х   |                                                                          |

| 10  | 未使用                  | х   |                                                                          |

| 11  | 未使用                  | х   |                                                                          |

| 12  | SRC_CD[0] *6         | х   | SRC_CD[1:0]で、転送元アドレスの増減を設定します。                                           |

| 13  | SRC_CD[1] *6         | х   |                                                                          |

| 14  | 未使用                  | х   |                                                                          |

| 15  | 未使用                  | х   |                                                                          |

| 16  | DST_CS[0] *7         | х   | DST_CS[1:0]で、転送先アドレスの GBUS のチップセレクト空間を指定                                 |

| 17  | DST_CS[1] *7         | х   | します。                                                                     |

| 18  | DST_CS[2] *7         | х   |                                                                          |

| 19  | 未使用                  | х   |                                                                          |

| 20  | SRC_CS[0] *7         | х   | SRC_CS[1:0]で、転送元アドレスの GBUS のチップセレクト空間を指定                                 |

| 21  | SRC_CS[1] *7         | х   | します。                                                                     |

| 22  | SRC_CS[2] *7         | х   |                                                                          |

| 23  | 未使用                  | х   |                                                                          |

| 24  | 未使用                  | х   |                                                                          |

| 25  | 未使用                  | х   |                                                                          |

| 26  | 未使用                  | х   |                                                                          |

| 27  | 未使用                  | х   |                                                                          |

| 28  | 未使用                  | x   |                                                                          |

| 29  | 未使用                  | х   |                                                                          |

| 30  | 未使用                  | х   |                                                                          |

| 31  | 未使用                  | X   |                                                                          |

#### 《注意事項》

- 1. DMA\_EN は、他のビット設定が終わってから"1"に設定してください。他のビットの操作と同時に DMA\_EN を"0"から"1"に設定しないでください。

- また、DMA\_EN が"1"の時は、DMA コントローラ内の他のビットを書き換えないでください。書き換えた場合の動作は不定です。

- 2. TC は、バイト・カウント・レジスタに設定したバイト数分の転送が終了すると"1"にな

ります。TC をクリアするためには、このビットに"1"を書き込んでください。また、TC をクリアする前に  $DMA\_EN$  を"0"に設定してください。 $DMA\_EN$  が"1"の時に TC をクリアすると、クリアした途端に再度 DMA が開始してしまいます。

- 3. DMA\_SINGLE を"1"に設定すると、DMA コントローラは 1 回の DMA 転送が終わるたびに GBUS の使用権を放棄し、CPU が GBUS を使用できるようにします。DMA\_SINGLEを"0"に設定すると、DMA コントローラは GBUS の使用権を確保したまま DMA を継続し、DMA 転送が終了するまで CPU は GBUS の使用権を取ることができなくなります。詳しくは、『7.4.10.20 シングル転送と非シングル転送』を参照してください。

- 4 . SOFT\_DREQ を"1"に設定すると、ハード的な DMA 要求を必要とせずに DMA 転送が行われます。ただし、SOFT\_DREQ が"1"の場合でも、GBUS の DMAAK-信号が DMA サイクル時にアクティブになります。

- 5 . DATA\_SIZE[1:0]は、次のフォーマットです。

[0,0]:8Bit 転送 [0,1]:16Bit 転送

[1,0]:32Bit 転送

[1,1]:設定禁止

6. DST\_CD[1:0]と SRC\_CD[1:0]は、次のフォーマットです。転送アドレスの増加 / 減少の単位は DATA\_SIZE[1:0]で設定された内容で決定します。

[0,0]:固定

[0,1]:増加

[1,0]:減少

[1,1]:設定禁止

7. DST\_CS[2:0]と SRC\_CS[2:0]は、次のフォーマットです。

[0,0,0]:GCS0-空間

[0,0,1]:GCS1-空間

[0,1,0]:GCS2-空間

[0,1,1]: GCS3-空間

[1,0,0]:GCS4-空間

[1,0,1]: GCS5-空間

[1,1,0]: GCS6-空間

7.4.10.5.DMA チャンネル 0 転送元アドレスポート(DMASRCADDR0 BA00-0010[Read/Write]) 7.4.10.6.DMA チャンネル 1 転送元アドレスポート(DMASRCADDR1 BA00-0090[Read/Write]) 7.4.10.7.DMA チャンネル 2 転送元アドレスポート(DMASRCADDR2 BA00-0110[Read/Write]) 7.4.10.8.DMA チャンネル 3 転送元アドレスポート(DMASRCADDR3 BA00-0190[Read/Write])

DMA の転送元アドレスを設定するポートです。アドレスは  $A0 \sim A23$  の 24Bit が有効です。転送アドレスは、各チャンネルの DMA 制御ポートに設定した  $DATA\_SIZE[1:0]$ のデータ・サイズにアラインされたアドレスでなければなりません。設定アドレスがアラインされていない場合の動作は不定です。

また、DMA 転送中もしくは転送終了後には、このポートからは次に DMA 転送を行うアドレスの内容が読み出せます。

7.4.10.9.DMA チャンネル 0 転送先アドレスポート(DMADSTADDR0 BA00-0020[Read/Write]) 7.4.10.10.DMA チャンネル 1 転送先アドレスポート(DMADSTADDR1 BA00-00A0[Read/Write]) 7.4.10.11.DMA チャンネル 2 転送先アドレスポート(DMADSTADDR2 BA00-0120[Read/Write]) 7.4.10.12.DMA チャンネル 3 転送先アドレスポート(DMADSTADDR3 BA00-01A0[Read/Write])

DMA の転送先アドレスを設定するポートです。アドレスは  $A0 \sim A23$  の 24Bit が有効です。転送アドレスは、各チャンネルの DMA 制御ポートに設定した  $DATA\_SIZE[1:0]$ のデータ・サイズにアラインされたアドレスでなければなりません。設定アドレスがアラインされていない場合の動作は不定です

また、DMA 転送中もしくは転送終了後には、このポートからは次に DMA 転送を行うアドレスの内容が読み出せます。

7.4.10.13.DMA チャンネル 0 バイトカウントポート ( DMABYTECNT0 BA00-0030[Read/Write] ) 7.4.10.14.DMA チャンネル 1 バイトカウントポート ( DMABYTECNT1 BA00-00B0[Read/Write] ) 7.4.10.15.DMA チャンネル 2 バイトカウントポート ( DMABYTECNT2 BA00-0130[Read/Write] ) 7.4.10.16.DMA チャンネル 3 バイトカウントポート ( DMABYTECNT3 BA00-01B0[Read/Write] )

DMA 転送する $\underline{\mathit{NT}}$ ト数 - 1 を設定するポートです。データは Bit0 ~ Bit23 の 24Bit が有効です。 DMA コントローラは、1 回の DMA 転送が終わるごとに、このポートの内容を各チャンネルの DMA 制御ポートに設定した DATA\_SIZE[1:0]のデータ・サイズに従って 1,2 もしくは 4 減少させます。この減算の結果キャリーが発生すると、DMA が終了します ( TC が"1"になります )。 また、DMA 転送中もしくは転送終了後には、現在のバイトカウンタの値が読み出せます。

#### 7.4.10.17.DMA 割り込み制御ポート (DMAINTCNT BA00-0200[Read/Write])

| Bit | 信号名       | RST | 機能                                                   |

|-----|-----------|-----|------------------------------------------------------|

| 0   | INT_EN[0] | 0   | $0$ :チャンネル $0$ の $TC$ ビットが $^*1$ $^*$ の時に割り込みを要求しない。 |

|     |           |     | 0:チャンネル 0 の TC ビットが"1"の時に割り込みを要求する。                  |

| 1   | INT_EN[1] | 0   | $0$ :チャンネル $1$ の $TC$ ビットが $^*1$ $^*$ の時に割り込みを要求しない。 |

|     |           |     | 0:チャンネル 1 の TC ビットが"1"の時に割り込みを要求する。                  |

| 2   | INT_EN[3] | 0   | $0$ :チャンネル $2$ の $TC$ ビットが $^*1$ $^*$ の時に割り込みを要求しない。 |

|     |           |     | 0:チャンネル2の TCビットが"1"の時に割り込みを要求する。                     |

| 3   | INT_EN[4] | 0   | $0$ :チャンネル $3$ の $TC$ ビットが $^*1$ $^*$ の時に割り込みを要求しない。 |

|     |           |     | 0:チャンネル 3 の TC ビットが"1"の時に割り込みを要求する。                  |

| 4   | TC[0] *1  | 0   | チャンネル 0 の TC ビットの内容の読みだし                             |

| 5   | TC[1] *1  | 0   | チャンネル l の TC ビットの内容の読みだし                             |

| 6   | TC[2] *1  | 0   | チャンネル <sup>2</sup> の TC ビットの内容の読みだし                  |

| 7   | TC[3] *1  | 0   | チャンネル 3 の TC ビットの内容の読みだし                             |

#### 《注意事項》

TC[3:0]は、各チャンネルの DMA 制御ポートの Bit1 の内容がそのまま読み出せます。このビットにより、どのチャンネルが割り込み要求をしているかが判断できます。このポートの TC[3:0]は読みだし専用であり、TC をクリアするには各チャンネルの制御ポートの TC を操作する必要があります。

| Bit | 信号名         | RST | 機能        |

|-----|-------------|-----|-----------|

| 0   | BIG-/LITTLE | 1   | 0: BIG    |

|     |             |     | 1: LITTLE |

| 1   |             | X   | 未使用       |

| 2   |             | X   | 未使用       |

| 3   |             | X   | 未使用       |

| 4   |             | Xv  | 未使用       |

| 5   |             | X   | 未使用       |

| 6   |             | X   | 未使用       |

| 7   |             | X   | 未使用       |

## 7.4.10.18.DMA エンディアン指定ポート (DMAENDIAN BA00-0280[Read/Write])

#### 《注意事項》

CPU の動作中のエンディアンと同じに設定にしてください。この設定は全 DMA チャンネルに

共通です。

#### 7.4.10.19.優先順位

各チャンネルは、チャンネル $_0$ が最も優先順位が高く、チャンネル $_3$ が最も低い優先順位となっています。複数の  $_{

m DMA}$  要求が競合した場合に、どのチャンネルの  $_{

m DMA}$  転送が行われるかは、GBUS 使用権を取得後のバス・サイクル開始直前の  $_{

m DMA}$  要求の状態で判断します。

#### 7.4.10.20.シングル転送と非シングル転送

DMA 制御ポートの DMA\_SINGLE への設定は、各チャンネルの 1 サイクル分の DMA 転送終了後に、GBUS 使用権を手放すかどうかを決定します。各チャンネルの DMA\_SINGLE の設定は、対応するチャンネルの DMA 転送サイクル後の状態を決定します。

DMA\_SINGLE を"1"に設定すると、DMA コントローラは 1 回の転送を終了するたびに GBUS の使用権を放棄し、CPU が GBUS を使用する余地を与えます。引き続き DMA 要求がアクティブであれば、DMA コントローラは改めて GBUS の使用権を要求します。

DMA 制御ポートの DMA\_SINGLE を"0"に設定すると、DMA 要求がアクティブであると(もしくは SOFT\_DREQ が"1"の場合)、転送が終了後も GBUS の使用権を手放さずに、続けて DMA 転送を行います。 ただし、チャンネル間の優先順位の調停は行われるため、同じチャンネルの DMA 転送が継続して起きるとは限りません。

#### 7.4.10.21.非シングル転送時の DMA 要求サンプル・タイミング

非シングル転送時に継続して DMA サイクルを行うかどうかは、転送先への書き込みサイクルがレディーになる(GREADY-が Low、GWAITI-が High)タイミングの DMA 要求の状態によります。このタイミングで、DMA 要求がアクティブであれば、GBUS の使用権を確保したままで継続的に DMA 転送を行います。

#### 8. パスサイクル・タイミング

RTE-VR5432-CB では、SRAM, DRAM, ROM, I/O などの各デバイスに合わせて、SYSAD バスからブリッジを介しアクセスしています。ここでは、各アクセス・サイクルの基本的な制御タイミングについて説明します。

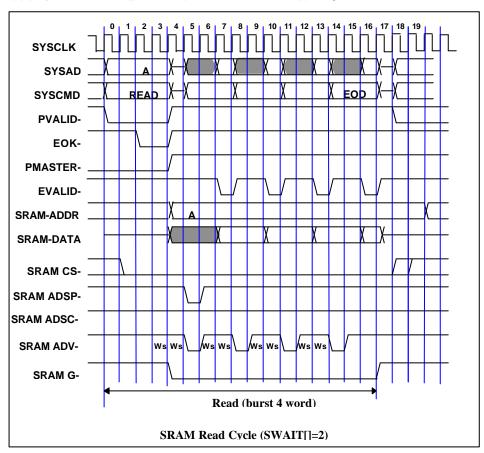

# 8.1. SRAM アクセス

SRAM リードサイクルは、SRAMC-SWAIT レジスタの設定により 0~3 ウェイトのアクセスとなります (「7.4.1 SRAM コントローラ (SRAMC B800-6000[Read/Write])」参照)。

下図は、2ウェイトを設定した時のバーストリードの例です。

クロックの番号に添って状態を説明します。

0~1: CPU の外部リードサイクルの始まりです。通常 EOK-はインアクティブです。

2~3:SRAM のリードサイクルが確定し、EOK-がアクティブになります。

3~4: SWAIT で設定したウェイトサイクル (この例では2ウェイト)が挿入されます。

5: PBSRAM ヘリードコマンドを与えます。

7:PBSRAM からデータが出力されます。これに合わせ EVALID-を返します。

8~16: 最後のデータ(EOD)となるまで、サイクルをくり返します。

(6~8): SWAIT で設定したウェイトサイクル (この例では 2 ウェイト) が挿入された後、 SRAM ADV-をアクティブにし、PBSRAM の内部アドレスを加算させます。

補足:8word のバーストサイクルの場合は、16 で SRAM ADSP-信号をアクティブにし、外部からアドレスを与え、バーストを継続します。

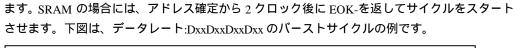

SRAM のライトサイクルは、CPU の出力データレート(DDDD または、DxxDxxDxxDxx)に従い

クロックの番号に添って状態を説明します。

- 0~1: CPU の外部ライトサイクルの始まりです。通常 EOK-はインアクティブです。

- 2~3: SRAM のライトサイクルが確定し、EOK-がアクティブになります。

- 4: 最初のデータ出力です。この時のデータを PBSRAM に直接ラッチさせ、ライト動作を開始します。アドレスは予めラッチしており、この時に同時に与えます。

- $5 \sim 13$ : ライト動作を繰り返します。 2番目以降のライトサイクルは、PBSRAM 内部のアドレスカウンタをインクリメントして使用します。 SRAM ADV-, SRAM W-は、データレートに合わせてタイミングをとっています。(データレート:DDDD の時は、連続してアクティブになります)

#### 8.2. DRAM アクセス

DRAM は、DRAM コントローラの設定が必要です。(「7.4.2 DRAM コントローラ (DRAMC B800-5000[Read/Write])」参照)。以下は、全て推奨値に設定した場合のものです。

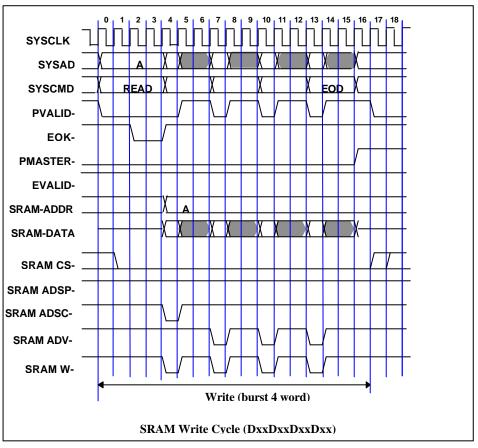

PAGE=0 (オートプリチャージ ON) の場合の DRAM リードサイクルを下図に示します。ただし、これはサイクルの開始にあたって、リフレッシュやプリチャージと重ならなかった場合のものです。重なった場合は、それらのサイクルが終了するまで待たされます。

クロックの番号に添って状態を説明します。

0~1: CPU の外部リードサイクルの始まりです。通常、EOK-は、インアクティブです。

$2\sim3$ :DRAM へのアクセスが確定し、 EOK-がアクティブになり、3 で SDRAM に対し、アクティブコマンドを発行します。この時 DRAM ADDR には、ロー(Raw)アドレスを与えます。

**4~5**: tRCD を待って、SDRAM に対し、5 で Read コマンドを与えます。この時、DRAM ADDR には、カラム(Column)アドレスを与えます。

7: 最初のリードデータ確定です。EVALID-をアクティブにして、このデータを直接 CPU に読み込ませます。

$8 \sim 14$ : 連続バーストで SDRAM からデータを読み出します。この間、CPU に対し EVALID-をアクティブにします。SDRAM に対しては、13 でバーストストップコマンドを与え、14 でプリチャージコマンドを与えます。

補足:AP=1(オートプリチャージ OFF)の場合は、14 でプリチャージコマンドは発行しません。

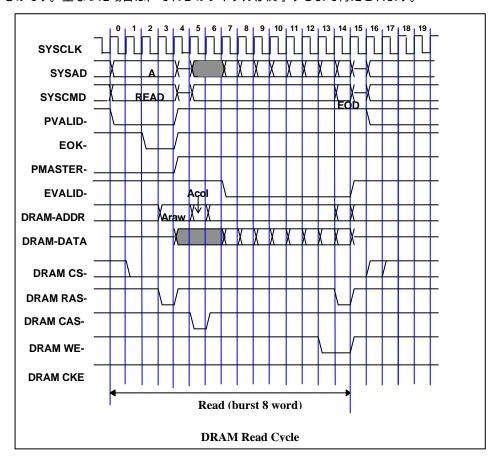

DRAM のライトサイクルは、CPU の出力データレート(DDDD または、DxxDxxDxxDxx)に従います。DRAM の場合には、アドレス確定から 3 クロック後にアクティブコマンドを発行し、その 1 クロック後に EOK-を返してサイクルをスタートさせます。下図は、データレート:DxxDxxDxxDxxのバーストサイクルの例です。

クロックの番号に添って状態を説明します。

$0\sim1$ : CPU の外部ライトサイクルの始まりです。通常 EOK-はインアクティブとなっています。  $2\sim3$ : DRAM のライトサイクルが確定し、3 で SDRAM に対しアクティブコマンドを発行します。 この時、DRAM ADDR には、ロウ(Row)アドレスを与えます。

**4~6**: アクティブコマンドから 1 クロック後に EOK-をアクティブとし、EOK-から 2 クロック後に CPU の外部ライトサイクルが始まります。

7: 最初のデータ出力です。SDRAM に対し、このデータを直接書き込むためにライトコマンドを発行します。この時、DRAM ADDR には、カラム (Column) アドレスを与えます。

**8~16**: ライト動作を繰り返します。 2 番目以降のライトはデータレイトに合わせるために DRAM CKE でタイミングを取っています。

17: バーストストップコマンドを SDRAM に対し、発行します。

18:プリチャージコマンドを SDRAM に対し、発行します。

補足:AP=1(オートプリチャージ OFF)の場合は、18 でプリチャージコマンドは発行しません。

AP=1 (オートプリチャージ OFF) の場合には、プリチャージが発行される迄の間、SDRAM の内部でローアドレスが一時的にホールドされます。この状態で同一のロウ・アドレス空間へアクセスした場合(ヒット) アクティブコマンドが省略されますので、リードサイクル、ライトサイクル共に、2クロックサイクル分少ないクロックで、SDRAM のアクセスが開始します。但し、不一致の場合(アンヒット)には、目的のアクセスに先立ち、プリチャージを行う必要がありますので、オーバーヘッドが多くなります。

SDRAM のリフレッシュは、CBR(auto)リフレッシュコマンドを使用し、タイマ 2 の設定によ約  $15 \mu$  秒ごとに行っています。

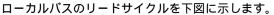

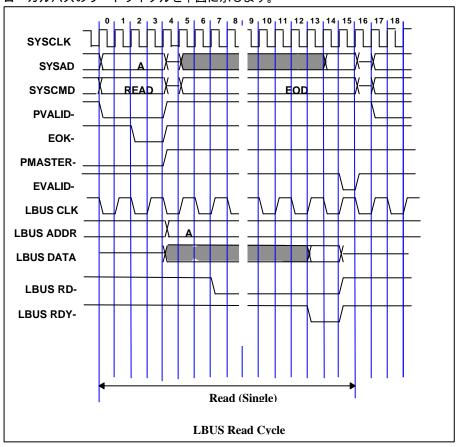

### 8.3. ローカルパス・アクセス

ローカルバスは SYSCLK の 1/2 で動作する 32 ビットのデータ幅を持つ同期バスです。

クロックの番号に添って状態を説明します。

0~1: CPU の外部リードサイクルの始まりです。通常 EOK-はインアクティブです。

2~3:LBUSへのリードサイクルが確定し、EOK-がアクティブになります。

6: LBUSへのリードサイクルが開始します。

8~9:アクセスする資源によってこの間のクロックは異なります。

**13~15**:LBUS RDY でアクティブになることで LBUS 上にデータが用意されたことを示します。 LBUS からのデータは、SYSCLK で同期を取って、SYSAD に出力します。LBUS RDY-をみて、 **15** で CPU へ EVALID-を返し、バスを終了します。

32

クロックの番号に添って状態を説明します。

- 0~1: CPU の外部ライトサイクルの始まりです。通常 EOK-はインアクティブです。

- 2~3: LBUS のライトサイクルが確定し、EOK-がアクティブになります。

- 4: データ出力です。LBUS コントローラは、この時のデータをラッチします。CPU のサイクルはこれで終了しますが、実際のライトサイクルは、これ以降に行われます。

- 6: LBUS へのライトサイクルが開始します。

- 8~9:アクセスする資源によってこの間のクロックは異なります。

- 13~14:LBUS RDY がアクティブになることで LBUS のライトサイクルが終了します。

## 8.4. 所要クロック一覧

メモリアクセスの所要クロック数を以下に示します。

# 8.4.1. SRAM のアクセス

| J            |       |       |       |       |       |       |       |       |          |             |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|----------|-------------|

| サイクル種別       | 1st   | 2nd   | 3rd   | 4th   | 5th   | 6th   | 7th   | 8th   | total    | 備考          |

| SingleRead   | 6 + n |       |       |       |       |       |       |       | 6 + n    | SWAIT[] = n |

| SingleWrite  | 5     |       |       |       |       |       |       |       | 5        | DDDD        |

| 8 BurstRead  | 6 + n | 1 + n | 1 + n | 1 + n | 1 + n | 1 + n | 1 + n | 1 + n | 13 + 8*n | SWAIT[] = n |

| 4 BurstWrite | 5     | 1 + n | 1 + n | 1 + n |       |       |       |       | 8 + 3 *n | DDDD        |

補足: 1.リードサイクルでは、n = SWAIT[]。 ライトサイクルでは、DxxDxx の時、n=2。

#### 8.4.2. SDRAM のアクセス

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |       |       |       |     |     |     |     |           |      |

|----------------------------------------|-----|-------|-------|-------|-----|-----|-----|-----|-----------|------|

| サイクル種別                                 | 1st | 2nd   | 3rd   | 4th   | 5th | 6th | 7th | 8th | total     | 備考   |

| SingleRead                             | 8   |       |       |       |     |     |     |     |           |      |

| SingleWrite                            | 8   |       |       |       |     |     |     |     |           | DDDD |

| 8 BurstRead                            | 8   | 1     | 1     | 1     | 1   | 1   | 1   | 1   | 15        |      |

| 4 BurstWrite                           | 8   | 1 + n | 1 + n | 1 + n |     |     |     |     | 11 + 3 *n | DDDD |

補足:1.ライトサイクルでは、DxxDxx の時、n=2。

- 2.オートプリチャージが ON の場合、最終サイクル後プリチャージ時間が加算されますが、最終サイクルから次サイクルの開始までに 2CLK 以上のアイドルサイクルがある場合、ペナルティはありません。

- 3.オートプリチャージが OFF の場合で、 $R_{aw}$  アドレスがヒットしたサイクルの  $1^{st}$  サイクルは、2clk 短縮されます。逆にヒットしなかった場合、 $1^{st}$  サイクルの直前にプリチャージサイクルが入りますので、2clk 加算されます。

### 9. ROM 化プログラミング

本ボード用に ROM 化するプログラムを作成する場合、以下を参考にしてください。。

### 9.1. 初期化

リセット処理ルーチンではプロセッサ・レジスタの初期化を行った後、メモリアクセスコントローラと DRAM のリフレッシュ用のタイマ 2 を設定してください。

以下では、ボード固有の事項に関してのみ記述します。その他に関しては、CPU のマニュアル等を参照してください。

```

<プロセッサの内部初期化>

Config Reg

... SW2-4 = OFF >> EP = 0x6(DxxDxx)

SW2-4= ON >>EP = 0x0(DDDD)

< SRAM ウェイトの初期化>

... SRAM Wait >> 0 ウェイト

[0xB8006000+offset].b \le 0

<SDRAM コントローラの初期化>

[0xB8005000+offset].b \le 2

... SDRAM tRCD >> 2 クロック

... SDRAM tRP >> 2 クロック

[0xB8005010+offset].b \le 2

... SDRAM tRC

>> 5 クロック

[0xB8005020+offset].b \le 5

... SDRAM tRRC >> 6 クロック

[0xB8005030+offset].b \le 6

[0xB8005040 + offset ].b \le 4

... SDRAM tRAS >> 4 クロック

... SDRAM tLAT >> 2 クロック

[0xB8005050+offset].b \le 2

[0xB8005060+offset].b \le 2

... SDRAM tRSC >> 2 クロック

>>オートプ リチャーシ :OFF(任意)

[0xB8005070+offset].b <= 1

... SDRAM AP

[0xB8004000+offset].b \le 0

... SDRAM Mode Reg Set

<リフレッシュ用タイマの初期化>

... タイマ 2 モード 2 (約 15 µ 秒周期に設定)

[0xB9005030+offset].b \le 0xb4

... タイマ2下位カウント

[0xB9005020+offset].b \le 0x1f

... タイマ 2 上位カウント

[0xB9005020+offset].b \le 0x00

```

【メモ】バイトアクセスにおける Big Endiab 時の offset は、3 です。

# 9.1.1. ROM データ配置

リモートモニタの ROM は、4つのバンクにわけて使用していますが、通常は、SW3-3 を ON にして、連続した空間としてご使用ください。

また 16 ビット・データバスの ROM の書き込みの際には、エンディアンによりデータのバイト並びが ROM ライタの形式と異なる場合があります(たとえば、プログラム・コードはビッグ・エンディアンで ROM ライタでのサポートがリトル・エンディアン形式)。このような場合 16 ビットデータの上位 / 下位 8 ビットのスワップをサポートしている ROM ライタで、その機能を使用してデータ書き込みを行います。

【メモ】ROM エミュレータを使用する場合は、必ず ROM のバンクを禁止(SW3-3-ON)してご使用ください。

# 10.GBUS 個別仕様

本章では、RTE-VR5432-CB での GBUS の使用状況を説明します。GBUS の一般的な仕様については「14 APPEDIX.C GBUS 共通仕様」を参照してください。

# 10.1. 概要

RTE-VR5432-CB での GBUS の信号線使用状況の概要を下表に示します。

| GBUS信号名                              | 機能                                                       | 参照     |

|--------------------------------------|----------------------------------------------------------|--------|

| GADDR[31:2]                          | アドレス線として使用。GADDR[26:31]は未接続。                             |        |

| GDATA[31:0]                          | データ線として使用。リード・サイクル時は、SYSCLKで一度ラッチされたものが CPU に供給される。      |        |

| GCS-[6:0]                            | チップ・セレクト線として使用。                                          | 10.3   |

| GCLK                                 | CPU の SYSCLK を 2 分周したクロックを接続。                            |        |

| GRESETI-                             | 本ボード上で発生したリセット要求を出力。                                     | 7.1    |

| GRESETO-                             | ボード上のリセット信号とオアして ColdReset*に接続。                          | 7.1    |

| GADS- , GREADY- ,<br>GBLAST- , GW/R- | バス制御信号として使用。                                             |        |

| GWAITI-                              | バス制御信号として使用。                                             |        |

| GBTERM-                              | バス制御信号として使用。                                             |        |

| GRD-, GWR-                           | GBUSの制御信号から生成した、RD-,WR-信号を接続。                            |        |

| GHOLD-, GHLDA-                       | 未接続                                                      |        |

| GBREQ-                               | 未接続                                                      |        |

| GDMARQ-[3:0]                         | DMA リクエスト信号として使用。                                        | 7.4.10 |

| GDMAAK-[3:0]                         | DMA アクノリッジ信号として使用。                                       | 7.4.10 |

| GINTO-[3:0]                          | 割込み要求信号として使用。                                            | 7.2    |

| GINTI-[1:0]                          | GINTI0-と GINTI1-へは、それぞれ TIC(μ PD71054)の OUT0 と OUT1 を接続。 |        |

| GETC[7:0]                            | 未接続。                                                     |        |

| GAHI_EN-                             | 未接続                                                      |        |

| GMOTHER_DETECT-                      | JGBUS未接続時に GBUS ヘアクセスした場合のレディー生成に使用。                     |        |

| GUSE_DIRECT_ACC-                     | 未接続                                                      |        |

| GCLK_LOW-                            | SW2-8 (BGCLK_LOW-)が、OFFの時 High、ONの時 Low。                 | 5.4    |

| GLOCK-[1:0]                          | 未接続                                                      |        |

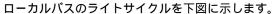

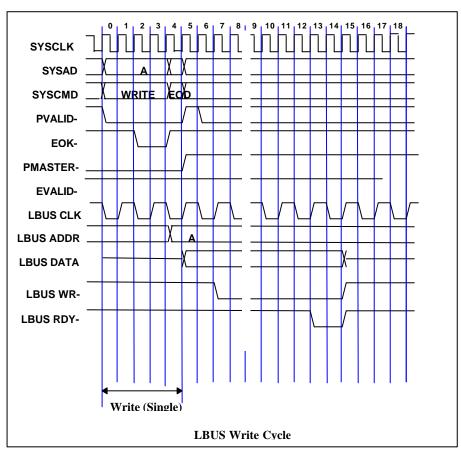

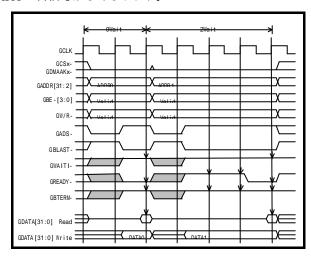

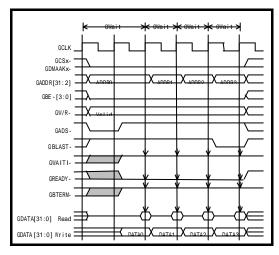

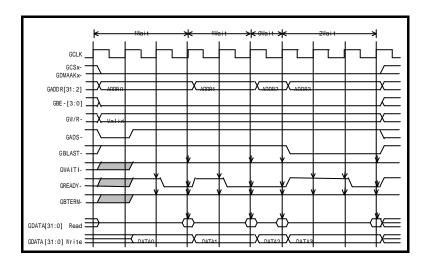

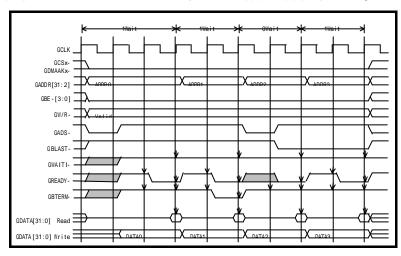

## 10.2. パス・サイクル

GBUS の GCLK へは、CPU の CLK を 2 分周したクロックを接続しています。また、GAHI\_ENを未接続にしているので、GADDR[26:31]は未接続になっています。

GBUS へのアクセスは、シングルサイクル、バーストサイクルの両方に対応しています。

以下に示す波形で、Gxxx 信号は GBUS の信号です。

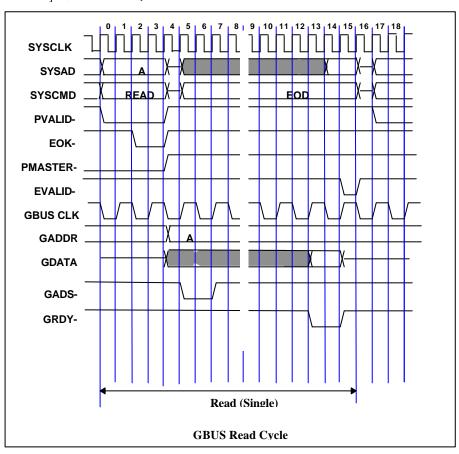

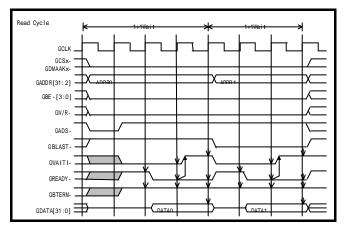

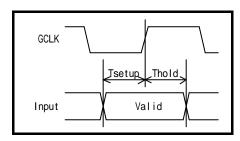

リード・サイクル (シングル)の様子を下図に示します。(バーストサイクルは、[14.6.2バースト・サイクル]を参照ください)

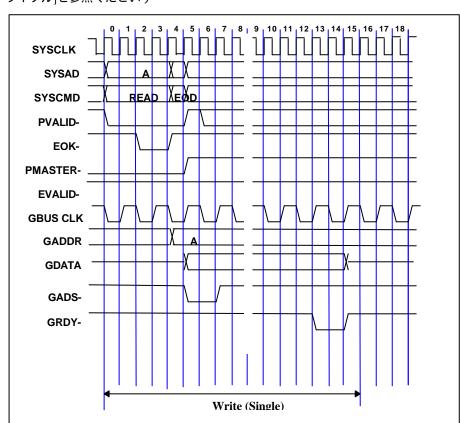

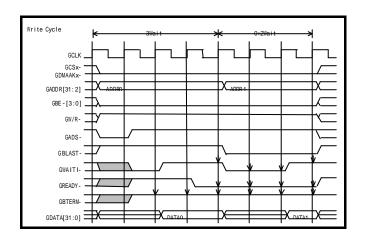

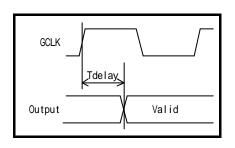

ライト・サイクル (シングル) の様子を下図に示します。(バーストサイクルは、[14.6.2バースト・サイクル]を参照ください)

# 10.3. チップセレクト

本ボードでは、GBUSの各チップセレクトには、下記の空間が割り当てられています。

**GBUS Write Cycle**

| GBUS信号名 | 論理アドレス範囲                | 物理アドレス空間                | 備考(RTE-MB-A の資源)     |

|---------|-------------------------|-------------------------|----------------------|

| GCS0-   | 0xB0000000 - 0xB0FFFFFF | 0x10000000 - 0x10FFFFFF | (MB-SRAM)            |

| GCS1-   | 0xB1000000 - 0xB1FFFFFF | 0x11000000 - 0x11FFFFFF | FBOOT=OFF (MB-FLASH) |

|         | 0xBF000000 - 0xBFFFFFF  | 0x1F000000 - 0x1FFFFFF  | FBOOT=ON (MB-FLASH)  |

| GCS2-   | 0xB2000000 - 0xB2FFFFFF | 0x12000000 - 0x12FFFFFF | (MB-Peri)            |

| GCS3-   | 0xB3000000 - 0xB3FFFFFF | 0x13000000 - 0x13FFFFFF | (MB-EXT-MEM)         |

| GCS4-   | 0xB4000000 - 0xB4FFFFFF | 0x14000000 - 0x14FFFFFF | (MB-EXT-IO)          |

| GCS5-   | 0xB5000000 - 0xB5FFFFFF | 0x15000000 - 0x15FFFFFF | (MB-PCI Bus)         |

| GCS6-   | 0xB6000000 - 0xB6FFFFFF | 0x16000000 - 0x16FFFFFF | (MB-PCI9080 Reg)     |

物理アドレスは、アンキャッシュ領域を記しています。キャッシュ領域としてアクセスする場合は、0x20000000 をマイナスしてください。尚、本ボードは、これらのいずれの資源に対してもキャッシュ領域としてバーストアクセスすることが可能ですが、IO 空間や共有メモリ空間はアンキャッシュでご使用ください。

## 11. APPEDIX.A MULTI モニタ

MULTI用のモニタ ROM を使用して、ホストの MULTI デバッガと接続して使用する場合の 設置方法と使用上の注意事項について説明します。

### 11.1. ボードの設置

# 11.1.1. RTE for Win32 のインストール

MULTI デバッガを使用する場合には、PC に通信用のソフトウェア (RTE for Win32)をインストールする必要があります。ソフトウェアのインストールとテストについては、添付の「RTE for Win32 インストール・マニュアル」を参照してください。

# 11.1.2. SW1 の設定

SW1 は、汎用の入力ポートのスイッチですが、実装されている MULTI 用のモニタでは、以下の通り使用しています。正しく設定してご使用ください。

| SW1 番号 | 1   | 2   | ボーレート              |

|--------|-----|-----|--------------------|

| 設定     | ON  | ON  | 115200 baud        |

|        | OFF | ON  | 38400 baud         |

|        | ON  | OFF | 19200 baud         |

|        | OFF | OFF | 9600 baud (出荷時の設定) |

ボーレートの設定

| SW1 番号 | 3   | 4   | プロファイラ周期               |

|--------|-----|-----|------------------------|

| 設定     | ON  | ON  | タイマを使用しない              |

|        | OFF | ON  | 200 Hz 5 ms            |

|        | ON  | OFF | 100 Hz 10 ms           |

|        | OFF | OFF | 60 Hz 16.67ms (出荷時の設定) |

プロファイラ周期の設定

| SW1 番号 | 8   |                 | デバッグモード  |

|--------|-----|-----------------|----------|

| 設定     | ON  | 7segLED をモニタが使用 |          |

|        | OFF | 通常の使用状態         | (出荷時の設定) |

デバッグモードの設定

SW1-5~7は、MULTIモニタでは使用していません。

# 11.1.3. ボードの接続

「6 ホスト PC との接続」を参照して、シリアルで PC と接続してください。

### 11.2. Multi モニタ

Multi 用の ROM モニタは、32Bit BigEndean/LittleEndian、64Bit BigEndean/LittleEndian の 4 つ動作 モードで実行可能です。モニタの動作モードは SW3-7:8 の設定に依存します。

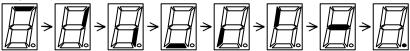

### 11.2.1. 起動時の 7Seg-LED

Multi 用の ROM モニタは、ボードの電源を入れると 7Seg-LED が次のように動きます (黒い部分が点灯部分)。

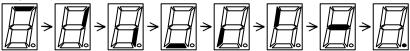

1)7Seg-LED のチェック動作(下図参照)

SW1-8 が OFF の場合:

SW1-8 が ON 場合

2)SRAM の簡易メモリチェックによる数字のカウント

SW1-8 が OFF の場合は行いません。

3)接続待ち状態(プロファイラのタイマを停止している場合は、ドットの点滅なし)

4)接続状態(ドットの点灯は、接続した時のドットの点灯状態が保持される)

# 11.2.2. モニタ・ワーク RAM

モニタでは、SRAM(Uncache)の先頭から 10000H ( 64KB ) をワーク用の RAM として使用 ( 予約 ) しています。すなわち、論理アドレス  $8000-0000H \sim 8000-FFFFH$  . $A000-0000H \sim A000-FFFFH$  はユーザ・プログラムでは使用できません。また、これのイメージ領域も同様です。

# 11.2.3. 割込み

モニタでは INTO 割込みを使用しています。この割込みに対するベクタは、ブートストラップ (BEV=1)の設定で ROM の BFCO-0380H です。したがって、ベクタを書き換えることができません。そこでモニタでは、SRAM(Uncache)の A000-0180H に確保した代替えベクタに 1 度分岐する 方法で書き換えを可能にしています。

### 11.2.4. \_INIT\_SP の設定

モニタで\_INIT\_SP(スタック・ポインタの初期値)は、A003-FFFCH(SRAM の最上位)に 設定されています(MULTIの環境で\_INIT\_SP を変更することもできます)。モニタでは、ユー ザ・プログラムで設定したスタック領域を 32 バイト使用します。

# 11.2.5. タイマ割込み

タイマ割込みを禁止しますと、Multiのプロファイラ機能が使用できません(タイマ割込みの設定については『11.1.2~SW1の設定』を参照)。

### 11.2.6. ハードウェアの初期化

ROM モニタでは、ボード上の資源に対し、直にアクセスできるように初期化を行っています。

## 11.2.7. 特殊命令

以下の命令を、シングルステップ、ブレークポイント及びシスコール機能で使用しています。

BREAK 命令(0xxxxxxdH)

ユーザプログラム内では、ブレーク命令と解釈されるコードは使用しないでください。

### 11.3. RTE コマンド

MULTI デバッガでモニタと MIDAS サーバ (RTESERV) と接続すると TARGET ウィンドウが 開かれ、ここから RTE コマンドを発行することができます。下表に RTE コマンドの一覧を示します。

| コマンド名      | 内容               |

|------------|------------------|

| HELP, ?    | ヘルプ表示            |

| INIT       | イニシャライズ          |

| VER        | バージョン表示          |

| CACHEFLUSH | キャッシュのフラッシュ      |

| SHOWTLB    | TLB 内容表示         |

| IOREAD     | I/O リード (サイズ指定 ) |

| IOWRITE    | I/O ライト(サイズ指定)   |

RTE コマンド一覧

各コマンドには、パラメータを必要とするものがあります。アドレスやデータなど、数値のパラメータは、全て16進数とみなされます。以下の数値指定は<u>誤り</u>です。

0x1234 1234H \$1234

## 11.3.1. HELP(?)

<書式> HELP [コマンド名]

HELP は、RTE コマンドの一覧や書式を表示します。また、"HELP"と入力するかわりに"?"としても同様です。コマンド名を省略すると、使用できるコマンド一覧を表示します。

<例> HELP INIT

INIT コマンドのヘルプを表示します。

# 11.3.2. INIT

<書式> INIT

INIT は、RTE環境の初期化を行ないます。通常、このコマンドは使用しないでください。

## 11.3.3. VER

<書式> VER

VER は、RTE 環境のバージョンを表示します。

### 11.3.4. CACHEFLUSH

<書式> CACHEFLUSH

CACHEFLUSH は、CPU のキャッシュ内容をフラッシュします。

## 11.3.5. SHOWTLB

<書式> SHOWTLB

SHOWTLB は、CPU の TLB 内容の一覧を表示します。

### 11.3.6. IOREAD

<書式> IOREAD [BYTE | SHORT | LONG] [アドレス]

IOREAD コマンドは、指定されたサイズでアドレスのメモリをリードし、そのデータを表示します。サイズは BYTE, SHORT, LONG で、8, 16, 32 ビットを指定します。このコマンドは、メモリマップド I/O のアクセスに使用します。

<例> IOREAD BYTE 0xBC000100 BC000100: 1A

## 11.3.7. IOWRITE

<書式> OWRITE [BYTE | SHORT | LONG] [データ] [アドレス]

IOWRITE コマンドは、指定されたサイズでアドレスのメモリにデータを書き込みます。サイズは BYTE, SHORT, LONG で、8, 16, 32 ビットを指定します。このコマンドは、メモリマップド I/O のアクセスに使用します。

<例> OWRITE SHORT 0x30F0 0xBC00F000 できます)。

# 12. APPEDIX.B PARTNER モニタ

PARTNER 用のモニタ ROM を使用して、ホストの PARTNER と接続して使用する場合の設置方法と使用上の注意事項について説明します。

## 12.1. ボードの設置

# 12.1.1. SW1 の設定

SW1 は、汎用の入力ポートのスイッチですが、実装されている PARTNER 用のモニタでは、 以下の通り使用しています。正しく設定してご使用ください。

| SW1 番号 | 1   | 2   | ポーレート              |

|--------|-----|-----|--------------------|

| 設定     | ON  | ON  | 115200 baud        |

|        | OFF | ON  | 38400 baud         |

|        | ON  | OFF | 19200 baud         |

|        | OFF | OFF | 9600 baud (出荷時の設定) |

ボーレートの設定

| SW1 番号 | 3  | 4  | タイマ             |

|--------|----|----|-----------------|

| 設定     | ON | ON | 常時この状態でご使用ください。 |

| SW1番号 | 8   | デバッグモード          |

|-------|-----|------------------|

| 設定    | ON  | 7segLED をモニタが使用  |

|       | OFF | 通常の使用状態 (出荷時の設定) |

デバッグモードの設定

SW1-5~7は、PARTNERでは使用していません。

## 12.1.2. ボードの接続

「6 ホストPCとの接続」を参照して、シリアルでPCと接続してください。

#### 12.2. PARTNER モニタ

Partner 用の ROM モニタは、32Bit BigEndean/LittleEndian の 2 つ動作モードで実行可能です。モニタの動作モードは SW3-7:8 の設定に依存します。

## 12.2.1. 起動時の 7Seg-LED

Partner 用の ROM モニタが実装されている場合、ボードの電源を入れると  $7Seg ext{-}LED$  が次のように動きます (黒い部分が点灯部分)。

1)7Seg-LED のチェック動作(下図参照)

SW1-8 が OFF の場合:

SW1-8 が ON 場合

2)RAM の簡易メモリチェックによる数字のカウント

SW1-8 が OFF の場合は行いません。

## 3)接続待ち状態

### 4)接続状態

# 12.2.2. ROM モニタ・ワーク RAM

ROM モニタでは、SRAM のの先頭から 10000H(64KB)をワーク用の RAM として使用(予約)しています。すなわち、論理アドレス 8000-0000H~8000-FFFFH ,A000-0000H~A000-FFFFH はユーザ・プログラムでは使用できません。また、これらのイメージ領域も同様です。

### 12.2.3. 割込み

モニタの通信および、強制ブレーク(ESC ボタン)で使用する割込みは、INTO を使用します。 この割込みに対するベクタは、ブートストラップ(BEV=1)の設定で ROM の BFC0-0380H です。 したがって、ベクタを書き換えることができません。そこでモニタでは、SRAM(Uncache)の A000-0180H に確保した代替えベクタに1度分岐する方法で書き換えを可能にしています。

#### 12.2.4. INIT\_SP の設定

モニタのスタック・ポインタの初期値は、A003-FFFOH(SRAM の最上位)に設定されていす。 この値は、PARTNER のコンフィギュレーションファイルで定義する INIT\_SP コマンドで変更で きます。モニタでは、ユーザ・プログラムで設定したスタック領域を 32 バイト使用します。

## 12.2.5. リモート接続

デバッガとの接続はシリアルです。SW1 の通信速度の設定と RPTSETUP で通信路と通信速度の設定を正しく行ってください。

# 12.2.6. ハードウェアの初期化

ROM モニタでは、ボード上の資源に対し、直にアクセスできるように初期化を行っています。

# 12.2.7. 特殊命令

モニタでは、以下の命令を、シングルステップ、ブレークポイント及びシスコール機能で使用 しています。

BREAK 命令 ( 0xxxxxxdH )

ユーザプログラム内では、ブレーク命令と解釈されるコードは使用しないでください。

### 13. APPEDIX.C 割込みプログラミング

モニタを使用してユーザプログラムで割込み処理を行なう場合について説明します。

#### 13.1. 割込みライブラリ

VR5432 では、一般例外割込みをまとめてベクタが割当てられており、モニタでも割込みを使用していることから、このベクタを共有することになります。そこで、割込みライブラリ(添付のサンプルプログラム: Intyect.c, IntHdr.s/mip )が用意されています。

ライブラリは、ベクタをフックし各例外ごとにテーブル管理をして、例外処理ルーチンを実行させます。以下に用意されている8つのライブラリ関数について説明します。

### 13.1.1. int InitIrqVect(void)

割込みベクタのフックとテーブルの初期化を行ないます。正常終了の場合には 0、エラーが発生した場合には、負のエラー番号を返します。

### 13.1.2. int TermIrqVect(void)

割込みベクタを元に戻します。正常終了の場合には<sub>0</sub>、エラーが発生した場合には、負のエラー番号を返します。

# 13.1.3. int SetIrqVect(int no, int func)

引数 no で指定される割込み処理テーブルに、関数 func を(int 型でキャストして)登録します。 no には intvect.h ファイルに"VECT IPn"の形式でマクロ化されているものを使用します。

また func に 0 を指定すると、前に設定されていた処理ルーチンを無効にできます。正常終了の場合には 0、エラーが発生した場合には、負のエラー番号を返します。

### 13.1.4. int GetlrqVect(int no)

引数 no で指定される割込み処理テーブルに登録されている関数アドレスを返します。0 の場合には登録されている関数がないことを示します。エラーが発生した場合には、負のエラー番号(奇数)を返します。

## 13.1.5. void SetIPnBit(int IPn)

引数 IPn で指定される割込みを許可します(ステータスレジスタの該当ビットを 1 にします)。

### 13.1.6. void ResIPnBit(int IPn)

引数 IPn で指定される割込みを禁止します(ステータスレジスタの該当ビットを () にします)。

#### 13.1.7. void ei(void)

すべての割込みを許可します。

### 13.1.8. void di(void)

NMIを除くすべての割込みを禁止します。

# 13.2. 割込みルーチン

ユーザの記述する割込み処理ルーチンは int 型の C 関数 (\_\_interrupt 修飾子をつけない)を想定しています。また、割込み処理ルーチンを正しくデバッグするために、割込み処理ルーチンの 先頭で該当する割込みを禁止、終了する前に割込みを許可してください。また、処理を完結する時には 0、モニタに戻す場合には 0 以外の値でリターンします。

### 13.3. サンプルプログラム

ユーザ割込み INT1(IP3)を使用して割込み処理を行う場合のサンプルプログラムを以下に示します。

```

#include "intvect.h"

int main( void )

/* --- can not Break & Step --- */

di();