***RTE-V850E2/MN4-EB-x***

**ユーザーズ・マニュアル (Rev.1.1)**

***Midas lab***

## 改訂履歴

| 実施日        | Revision | 章           | 内容              |

|------------|----------|-------------|-----------------|

| 2010.09.01 | 1.0      |             | 初版              |

| 2011.06.14 | 1.1      | Appendix. A | Appendix. A を追加 |

|            |          |             |                 |

|            |          |             |                 |

|            |          |             |                 |

|            |          |             |                 |

## 目次

|                                          |    |

|------------------------------------------|----|

| 1. はじめに.....                             | 6  |

| 1.1. マニュアル表記について.....                    | 6  |

| 1.2. 製品型番について.....                       | 6  |

| 2. 機能概要 .....                            | 7  |

| 3. 基本的な仕様.....                           | 8  |

| 4. ボードの説明.....                           | 10 |

| 4.1. リセットスイッチ(SW10).....                 | 11 |

| 4.2. 電源コネクタ(CN23,CN24,CN25).....         | 11 |

| 4.3. スイッチ 1 (SW1).....                   | 12 |

| 4.4. スイッチ 2 (SW2).....                   | 13 |

| 4.5. スイッチ 3 (SW3).....                   | 13 |

| 4.6. スイッチ 4 (SW4).....                   | 14 |

| 4.7. スイッチ 5 (SW5).....                   | 14 |

| 4.8. スイッチ 6,7 (SW6,SW7).....             | 15 |

| 4.9. スイッチ 8,9 (SW8,SW9).....             | 15 |

| 4.10. クロック .....                         | 16 |

| 4.11. デバッグ用コネクタ(CN1).....                | 16 |

| 4.12. MINICUBE 用コネクタ(CN2).....           | 17 |

| 4.13. アナログ信号入力コネクタ(CN3) .....            | 17 |

| 4.14. フラッシュプログラミングツール用コネクタ(CN4).....     | 18 |

| 4.15. プライマリバス拡張用コネクタ(CN5,CN6) .....      | 18 |

| 4.16. テストピン用コネクタ(CN7).....               | 20 |

| 4.17. PLD プログラム用コネクタ(CN8).....           | 20 |

| 4.18. LCD パネルモジュール IF コネクタ(CN9) .....    | 21 |

| 4.19. LCD パネルバックライト用コネクタ(CN10) .....     | 21 |

| 4.20. ステレオジャックコネクタ(CN11,CN12,CN13) ..... | 22 |

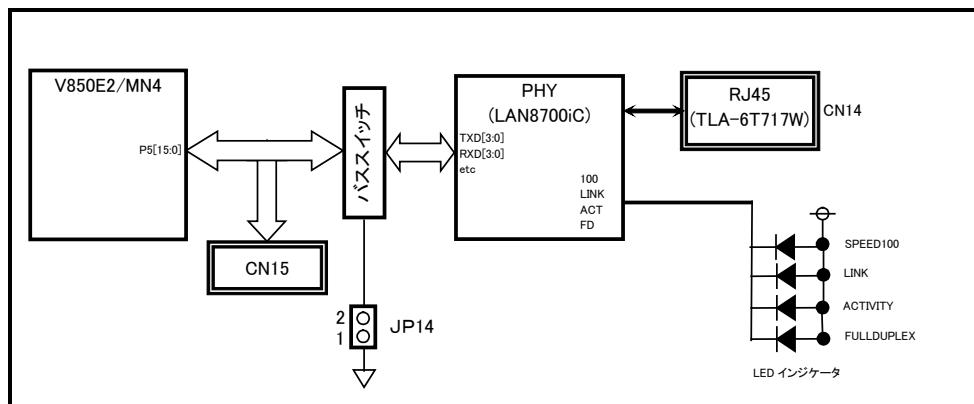

| 4.21. LAN コネクタ(CN14) .....               | 22 |

| 4.22. PHY ドータカードコネクタ(CN15) .....         | 23 |

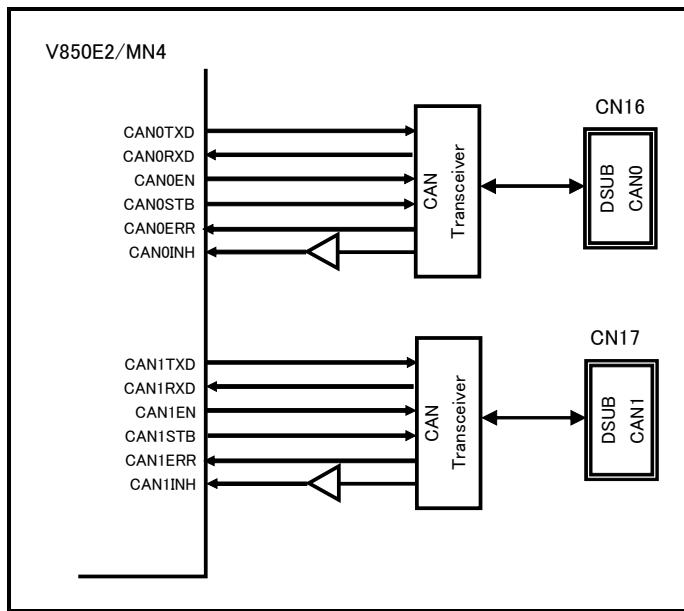

| 4.23. CAN コネクタ(CN16,CN17) .....          | 23 |

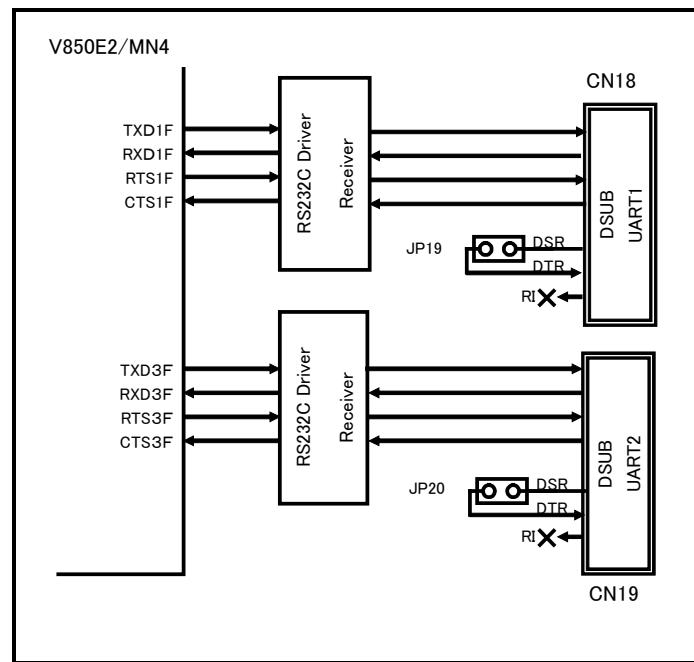

| 4.24. UART コネクタ(CN18,CN19).....          | 24 |

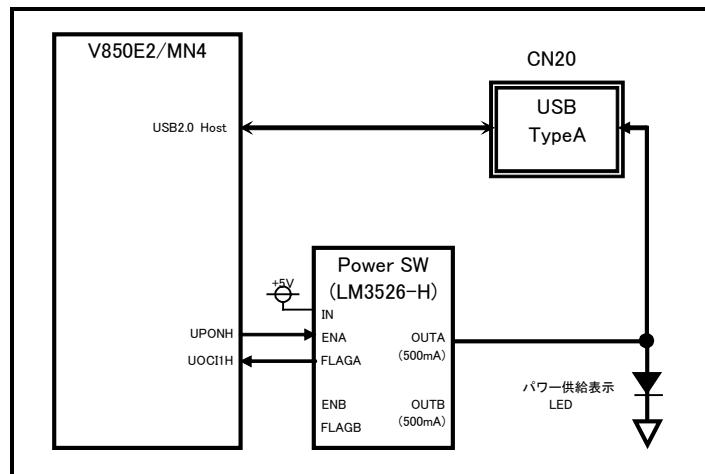

| 4.25. USB-HOST コネクタ(CN20) .....          | 24 |

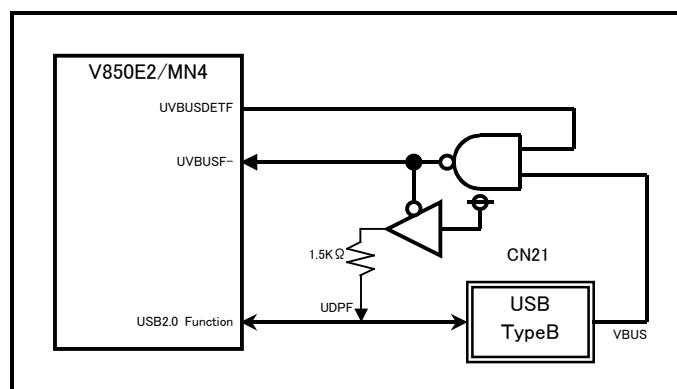

| 4.26. USB-FUNCTION コネクタ(CN21) .....      | 25 |

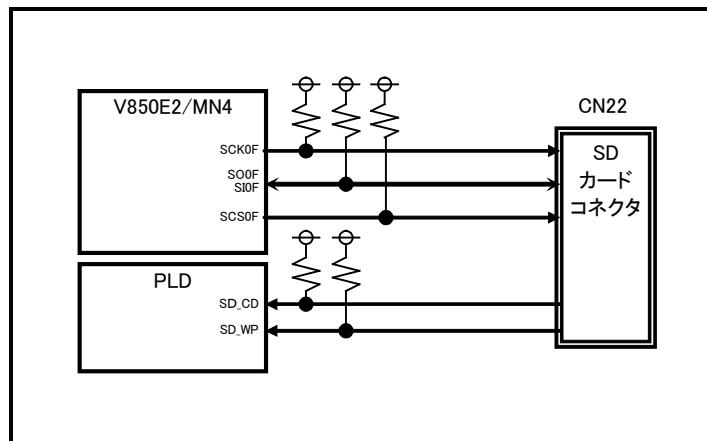

| 4.27. SD カード用コネクタ(CN22).....             | 25 |

|                                                |    |

|------------------------------------------------|----|

| 4.28. AVDD 切り替えジャンパ(JP1).....                  | 26 |

| 4.29. ジャンパ(JP2).....                           | 26 |

| 4.30. プライマリ SRAM バス幅切り替えジャンパ(JP3,JP4).....     | 26 |

| 4.31. P12-8 機能選択ジャンパ(JP6).....                 | 26 |

| 4.32. P13-0 機能選択ジャンパ(JP7).....                 | 26 |

| 4.33. P13-5 機能選択ジャンパ(JP8).....                 | 26 |

| 4.34. SDRAM バス幅切り替えジャンパ(JP9).....              | 26 |

| 4.35. セカンダリ SRAM バス幅切り替えジャンパ(JP10,JP11).....   | 27 |

| 4.36. PHONE/LINE 出力切り替えジャンパ(JP12,JP13).....    | 27 |

| 4.37. LAN8700IC バス切り離し選択ジャンパ(JP14).....        | 27 |

| 4.38. グランド接続切り替えジャンパ(JP15,JP16,JP17,JP18)..... | 27 |

| 4.39. DSR-DTR ループバック切り替えジャンパ(JP19,JP20).....   | 27 |

| 4.40. フラッシュプログラマ DDO/DDI 接続方法選択ジャンパ(JP21)..... | 27 |

| 4.41. リセット信号選択ジャンパ(JP22).....                  | 27 |

| 4.42. ジャンパ(JP23).....                          | 28 |

| 4.43. TDO プルアップ選択ジャンパ(JP24).....               | 28 |

| 5. ハードウェア・リファレンス .....                         | 29 |

| 5.1. メモリ・I/O のマップ .....                        | 29 |

| 6. メモリ詳細.....                                  | 31 |

| 6.1. SRAM .....                                | 31 |

| 6.2. SDRAM .....                               | 31 |

| 7. IOマップ .....                                 | 33 |

| 7.1. IO マップ一覧 .....                            | 33 |

| 7.2. PLD (0xF900_0000–0xF900_001F) .....       | 33 |

| 7.2.1. REG0 PLAY_D (0xF900_0000) .....         | 33 |

| 7.2.2. REG1 PLAY_C (0xF900_0004) .....         | 34 |

| 7.2.3. REG2 REC_D (0xF900_0008) .....          | 34 |

| 7.2.4. REG3 REC_C (0xF900_000C) .....          | 35 |

| 7.2.5. REG4 (0xF900_0010) .....                | 35 |

| 7.2.6. REG5 RSV (0xF900_0014) .....            | 35 |

| 7.2.7. REG6 MISC (0xF900_0018) .....           | 36 |

| 7.2.8. REG7 (0xF900_001C) .....                | 36 |

| 7.3. SW4 読み出しポート (0xF900_0018) .....           | 37 |

| 7.4. LED 表示出力ポート (0xF900_001C) .....           | 37 |

|             |                 |    |

|-------------|-----------------|----|

| 7.5.        | LAN-PHY         | 37 |

| 7.6.        | USB2.0-HOST     | 38 |

| 7.7.        | USB2.0-FUNCTION | 38 |

| 7.8.        | SD インターフェース     | 39 |

| 7.9.        | UART            | 39 |

| 7.10.       | CAN             | 40 |

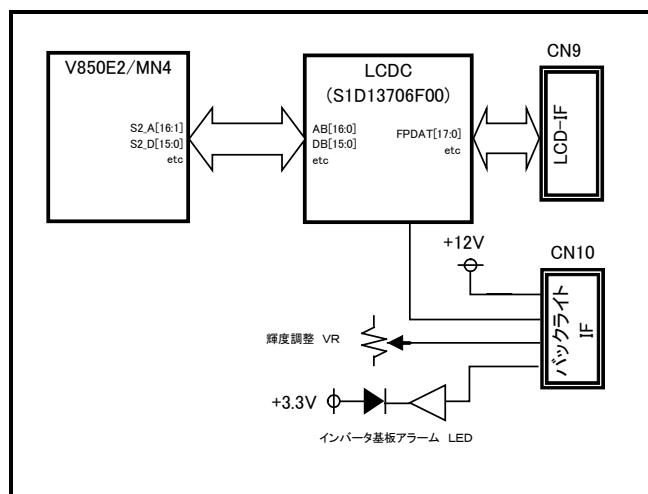

| 7.11.       | LCDC            | 40 |

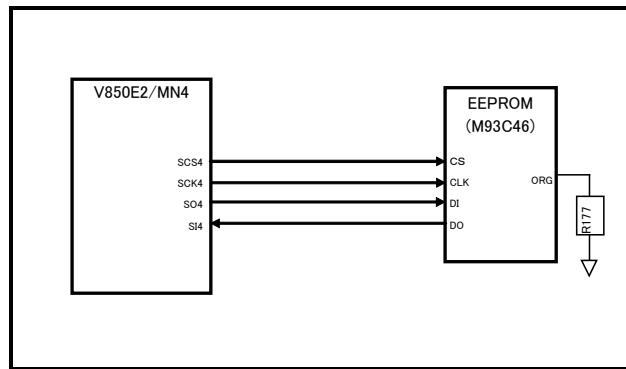

| 7.12.       | EEPROM          | 43 |

| 7.13.       | CODEC           | 43 |

| 8.          | CPU端子接続         | 47 |

| 8.1.        | 端子接続一覧          | 47 |

| APPENDIX. A |                 | 50 |

| - MEMO -    |                 | 51 |

## 1. はじめに

RTE-V850E2/MN4-EB は、Renesas エレクトロニクス社製プロセッサ V850E2/MN4 のリファレンスプラットフォームです。本ボードは、SRAM、SDRAM、Ethernet、USB2.0-Host/Function、SD カード、LCD、CAN、オーディオ CODEC、UART 等のインターフェース機能を搭載しています。

プロセッサの性能評価、デモンストレーション、アプリケーション・プログラムの試作開発など、幅広くご利用頂けます。

### 1.1. マニュアル表記について

本書では、数字の表記については下表の表記を用います。16 進数や 2 進数の表記では、桁数が多くて読みにくい場合は、4 桁ごとに“-”(ハイフン)を入れてあります。

| 進数    | 表記規則           | 例                      |

|-------|----------------|------------------------|

| 10 進数 | 数字のみを示します      | “10”は 10 進数の“10”を示します  |

| 16 進数 | 数字の末尾に“H”を記します | “10H”は 10 進数の“16”を示します |

| 2 進数  | 数字の末尾に“B”を記します | “10B”は 10 進数の“2”を示します  |

数字表記規則

### 1.2. 製品型番について

以下の2種の製品が用意されています。

RTE-V850E2/MN4-EB-S : シングルコアの V850E2/MN4 が実装されたボードです。

RTE-V850E2/MN4-EB-D : シマルチコアの V850E2/MN4 が実装されたボードです。

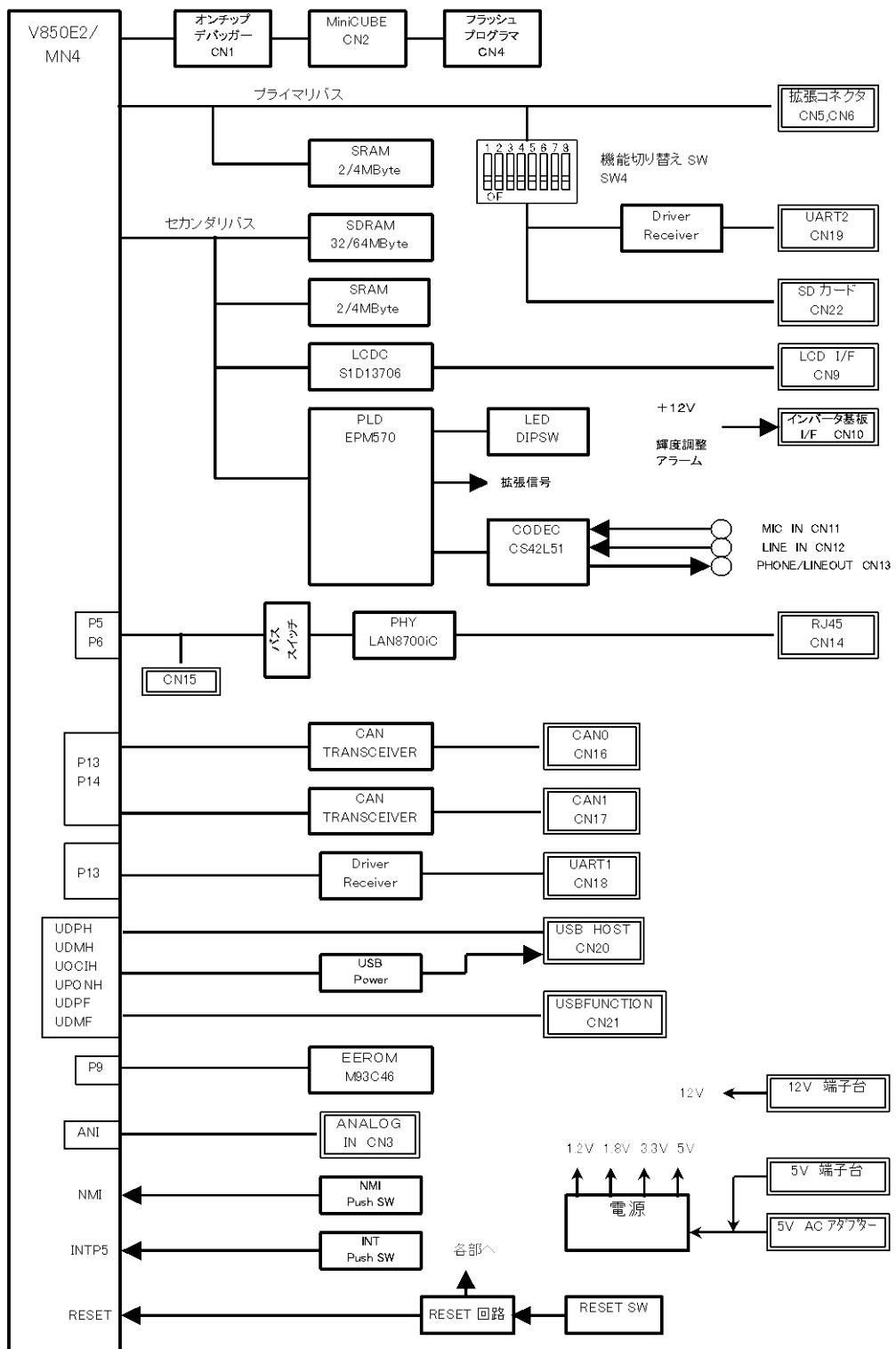

## 2. 機能概要

RTE-V850E2R/MN4-EB の機能ブロックの概要を下図に示します。

### 3. 基本的な仕様

| 項目              |                  | 概要                                                                          | 主要部品                             |   |

|-----------------|------------------|-----------------------------------------------------------------------------|----------------------------------|---|

| CPU             |                  | マイコン                                                                        | V850E2/MN4                       | 1 |

| プライマリ<br>バス メモリ | SRAM             | 16 ビットバス時 2MByte<br>32 ビットバス時 4MByte ジャンパ切り替え                               | SRAM:NEC<br>uPD4416016G5         | 2 |

| セカンダリ<br>バス メモリ | SRAM             | 16 ビットバス時 2MByte<br>32 ビットバス時 4MByte ジャンパ切り替え                               | SRAM:NEC<br>uPD4416016G5         | 2 |

|                 | SDRAM            | 16 ビットバス時 32MByte<br>32 ビットバス時 64MByte ジャンパ切り替え                             | SDRAM:MICRON<br>MT48LC16M16A2P   | 3 |

| セカンダリ<br>バス 周辺  | PLD              | 汎用 DIPSW、汎用 LED、DMA 要求<br>オーディオ CODEC 制御、RS232C 補助信号<br>CAN 補助信号、SD カード制御信号 | PLD:アルテラ<br>EPM570T100C5N        | 1 |

|                 | LCDC             | LCDコントローラをバスで接続                                                             | LCDC:エプソン<br>SID13706F00A        | 1 |

|                 |                  | LCD パネル用コネクタを装備                                                             | コネクタ:エルコ<br>08-6260-033-340-829+ | 1 |

|                 |                  | バックライト用インバータ制御、輝度調整<br>インバータエラー表示                                           | コネクタ:MOLEX<br>53261-0871         | 1 |

| CPU<br>ポート      | USB 2.0 Host     | V850E2/MN4 USB 2.0 Host I/F (A 端子コネクタ)                                      | コネクタ:AMP<br>292303-4             | 1 |

|                 | USB 2.0 Function | V850E2/MN4 USB 2.0 Function I/F (B 端子コネクタ)                                  | コネクタ:AMP<br>292304-1             | 1 |

|                 | UART1,2          | V850E2/MN4 UART1F、UART3F I/F に接続                                            | コネクタ:オムロン<br>XM2C-0912-132       | 2 |

|                 |                  |                                                                             | ドライバレーシーバ:マキシム<br>MAX3233        | 2 |

|                 | CAN1,2           | V850E2/MN4 CAN0、CAN1 I/F に接続                                                | コネクタ:オムロン<br>XM3B-0922-132       | 1 |

|                 |                  |                                                                             | トランシーバ:NXP<br>TJA1041T           | 1 |

|                 | CSI              | 1Kビット EEPROM を CSI4 に接続                                                     | EEROM:ST マイクロ<br>M93C46          | 1 |

|                 | SD カード           | SD I/F を CSIO に接続                                                           | コネクタ:アルプス<br>SCDA3A0202          | 1 |

|                 | Ether            | V850E2/MN4 Ether 10/100Mbps を P5、P6 ポートへ<br>接続<br>PHY 交換用ボード搭載コネクタを装備       | PHY:SMSC<br>LAN8700iC            | 1 |

|                 |                  |                                                                             | コネクタ:TDK<br>TLA-6T717W           | 1 |

|                 |                  |                                                                             | コネクタ:AMP<br>6-5174215-2          | 1 |

| PLD<br>ポート      | ADC              | V850E2/MN4 ANIに接続                                                           | コネクタ:オムロン<br>XG4C-1431           | 1 |

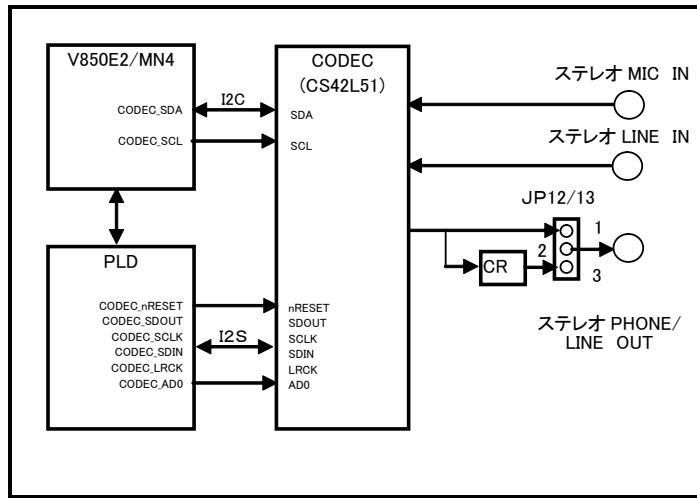

|                 | CODEC            | オーディオ用CODECを装備<br>PLD ポートからシリアル制御                                           | CODEC:CIRRUS LOGIC<br>CS42L51    | 1 |

|                 |                  |                                                                             | コネクタ:ホシデン<br>HSJ1636-01054       | 3 |

| プライマリ<br>バス 周辺  | プライマリバス拡張        | プライマリバス拡張コネクタ                                                               | コネクタ:オムロン<br>XG4C-5031           | 2 |

| 項目   |                       | 概要                                                   | 主要部品                                                |

|------|-----------------------|------------------------------------------------------|-----------------------------------------------------|

| 供給電源 | ACアダプタ電源<br>又は<br>端子台 | +5V :xxA                                             | 電源ジャック<br>HEC0470-01-630<br>端子台: サトーパーツ<br>ML-950-2 |

|      | 端子台                   | +12V :xxA                                            | 端子台: サトーパーツ<br>ML-950-2                             |

| 生成電源 | +3.3V                 | 最大電流値: 6A                                            | EN5366QI (Enpirion)                                 |

|      | +1.8V                 | 最大電流値: 1A                                            | MAX8869EUE10 (MAXIM)                                |

|      | +1.2V                 | 最大電流値: 1A                                            | EN5311QI (Enpirion)                                 |

| MISC | コネクタ                  | オンチップデバッグ用コネクタ                                       | コネクタ: AMP<br>2-5767004-2                            |

|      |                       | MiniCUBE 用コネクタ                                       | コネクタ: オムロン<br>XG4C-2031                             |

|      |                       | フラッシュプログラム用コネクタ                                      | コネクタ: オムロン<br>XG4C-1631                             |

|      |                       | PLDプログラム用コネクタ                                        | コネクタ: オムロン<br>XG8V-0631                             |

|      |                       | V850E2/MN4 CPUクロック選択                                 | MF-30-1-5                                           |

|      |                       | テストピン                                                | コネクタ: オムロン<br>XG4C-4031                             |

|      | スイッチ                  | モード設定 DIPSW                                          | SW: コパル<br>CHS-04TA1                                |

|      |                       | 共有端子信号切断 DIPSW                                       | SW: コパル<br>CHS-08TA1                                |

|      |                       | プライマリバス SRAM ベースアドレス選択用 DIPSW                        | SW: コパル<br>CHS-04TA1                                |

|      |                       | 汎用 DIPSW (PLD ポート)                                   | SW: コパル<br>CHS-08TA1                                |

|      |                       | CAN 伝送ライン終端 DIPSW                                    | SW: コパル<br>CHS-02TA1                                |

|      |                       | CAN ウェイク用スイッチ                                        | SW: 日開<br>G-19AP                                    |

|      |                       | NMI 用 プッシュ SW                                        | SW: フジソク<br>FP1F-2M-Z                               |

|      |                       | INTP5 用 プッシュ SW                                      | SW: フジソク<br>FP1F-2M-Z                               |

|      | LED                   | リセット用 トグル SW                                         | SW: フジソク<br>FT1F-2M-Z                               |

|      |                       | 汎用 LED (PLD ポート)                                     | LED: ローム<br>SML-210PTT86                            |

|      |                       | LANステータス LED (SPEED100、LINK、ACTIVITY、<br>FULLDUPLEX) | LED: ローム<br>SML-210PTT86                            |

|      |                       | USB電源供給インジケータ                                        | LED: ローム<br>SML-210PTT86                            |

|      |                       | バックライト用インバータ基板 エラー表示                                 | LED: スタンレー<br>FR1112H                               |

|      |                       | +5V 電源入力インジケータ                                       | LED: スタンレー<br>UB1112H                               |

|      |                       | +12V 電源入力インジケータ                                      | LED: スタンレー<br>UB1112H                               |

|      | VR                    | バックライト 輝度調整用                                         | VR: コパル<br>RJ-4EW 50KΩ                              |

#### 4. ボードの説明

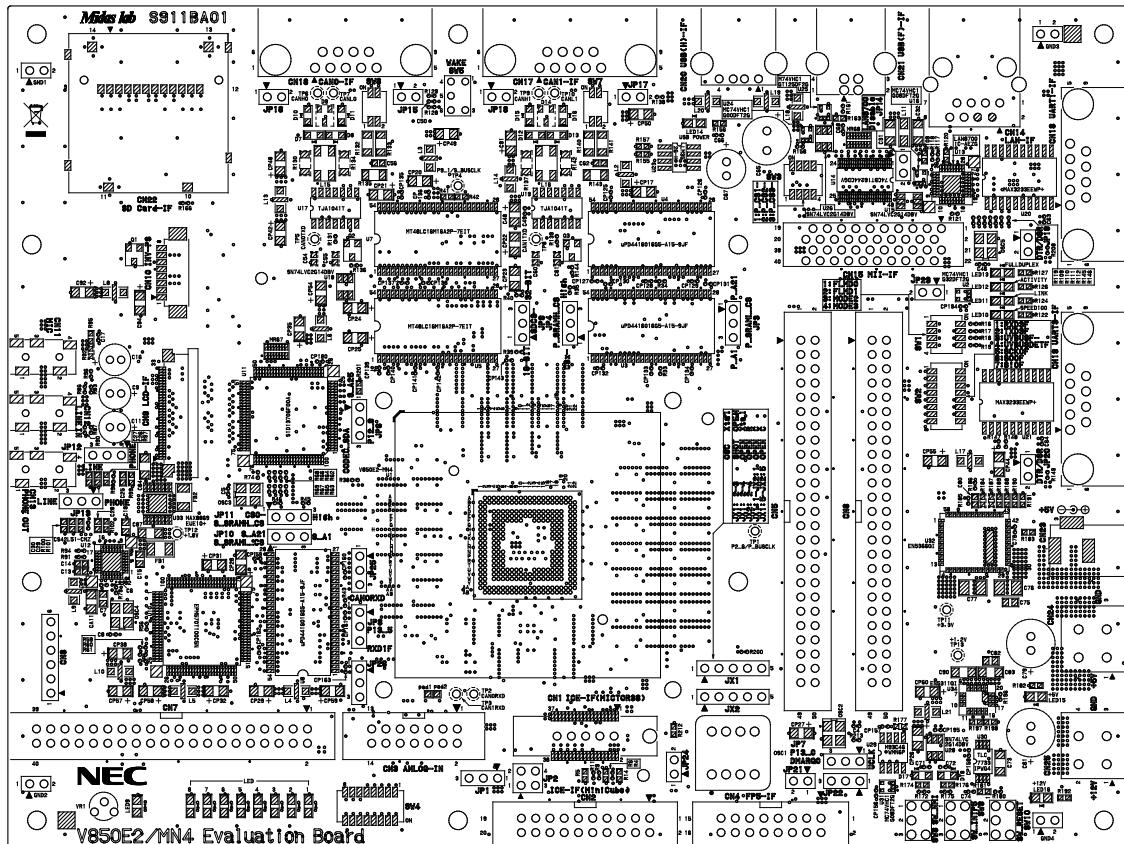

下図は RTE-V850E2R/MN4-EB 上の主要な部品の物理的な配置です。本章では、それぞれの部品について説明します。

RTE-V850E2R/MN4-EB の部品配置図

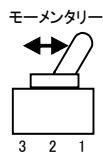

#### 4.1. リセットスイッチ(SW10)

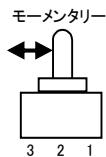

システムのリセットスイッチです。モーメンタリーとなっており、レバーを反対方向に倒したときリセット動作となります。手を離すと元の位置に戻ります。

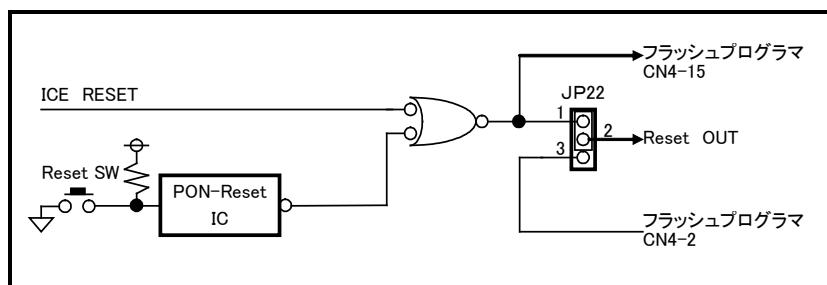

リセットの回路イメージを下図に示します。デフォルトで JP22 は 1-2 間がショートされています。

#### 4.2. 電源コネクタ(CN23,CN24,CN25)

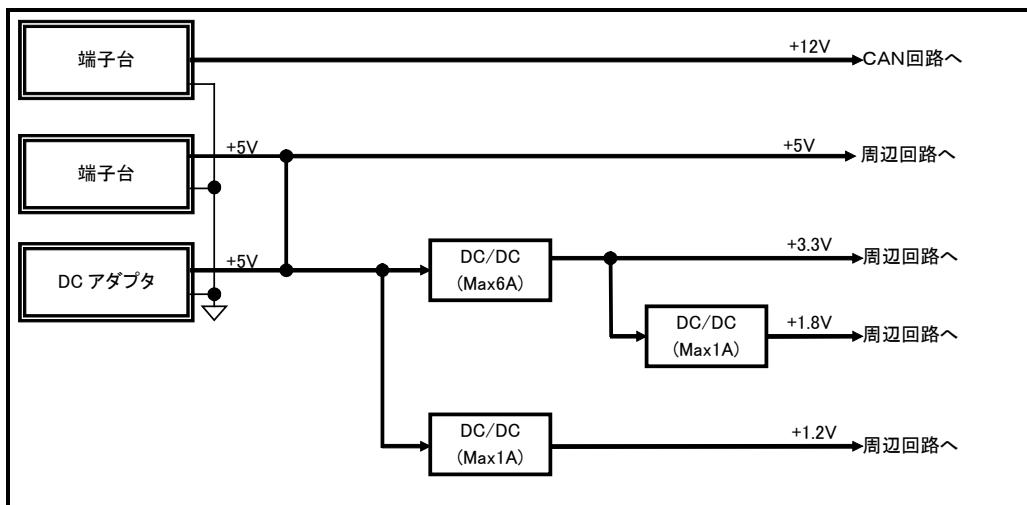

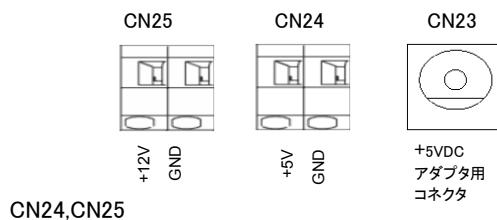

DC アダプタもしくは端子台から+5V、及び端子台から+12V を供給します。電源構成を下図に示します。CAN をご使用にならない場合は、5V だけの接続でご使用いただけます。

+5V と +12V の端子台を間違わないようにして

ください。

CN24,CN25

メーカー : サトーパーツ

型番 : ML-950-2

CN23

メーカー : ホシデン

型番 : HEC0470-01-630

DC アダプタコネクタ

CN23 に供給する電源は、以下の通りです。

電圧 : +5V

電流 : 1A 以上

適合コネクタ: TypeA(Φ 5.5)

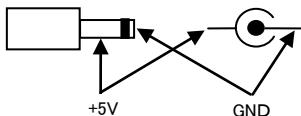

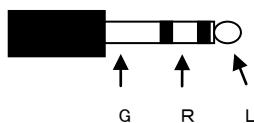

極性 : 下図

添付の電源をご使用ください。もし、他の電源

を使う場合は、極性に十分ご注意ください。

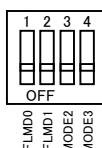

#### 4.3. スイッチ 1 (SW1)

V850E2/MN4 CPUのフラッシュプログラミングモード及び動作モードを決定します。

| 番号 | 信号名   | 出荷時の設定 | 機能                                     |

|----|-------|--------|----------------------------------------|

| 1  | FLMD0 | ON     | CPU の FLMD0 端子のレベル設定(ON:Low, OFF:High) |

| 2  | FLMD1 | ON     | CPU の FLMD1 端子のレベル設定(ON:Low, OFF:High) |

| 3  | MODE2 | ON     | CPU の MODE2 端子のレベル設定(ON:Low, OFF:High) |

| 4  | MODE3 | ON     | CPU の MODE3 端子のレベル設定(ON:Low, OFF:High) |

#### 4.4. スイッチ 2 (SW2)

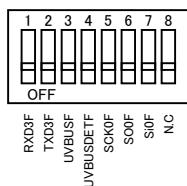

兼用端子に接続されているインターフェース回路を切り離し、競合しないようにするためのスイッチです。

個別に設定可能です。プライマリバス拡張用コネクタ(CN5、CN6)を使用する際、基板上の回路信号との衝突を防止する役割も持っています。CPU の端子接続については【8.1 端子接続一覧】を参照してください。

| 番号 | 信号名       | 出荷時の設定 | 機能                                                                        |

|----|-----------|--------|---------------------------------------------------------------------------|

| 1  | RXD3F     | OFF    | ON : P4_6 を RXD3F として使用します<br>OFF : P4_6 を EX_P4_6 として使用します               |

| 2  | TXD3F     | OFF    | ON : P4_7 を TXD3F として使用します<br>OFF : P4_7 を EX_P4_7 として使用します               |

| 3  | UVBUSF-   | OFF    | ON : P4_9 を UVBUSF- として使用します<br>OFF : P4_9 を EX_P4_9 もしくは P_CS2- として使用します |

| 4  | UVBUSDETF | OFF    | ON : P4_10 を UVBUSDETF として使用します<br>OFF : P4_10 を EX_P4_10 として使用します        |

| 5  | SCK0F     | OFF    | ON : P4_11 を SCK0F として使用します<br>OFF : P4_11 を EX_P4_11 として使用します            |

| 6  | SO0F      | OFF    | ON : P4_12 を SO0F として使用します<br>OFF : P4_12 を EX_P4_12 として使用します             |

| 7  | SI0F      | OFF    | ON : P4_13 を SI0F として使用します<br>OFF : P4_13 を EX_P4_13 として使用します             |

| 8  |           | OFF    | 未使用                                                                       |

#### 4.5. スイッチ 3 (SW3)

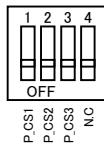

SRAM のベースアドレスを選択するためのスイッチです。SRAM のベースアドレスを P\_CS1～P\_CS3 の中から選択することができます。同時に 2 つ以上 ON としてはいけません。全てを OFF することで SRAM をバスから切り離すこともできます。

| 番号 | 信号名   | 出荷時の設定 | 機能                                                |

|----|-------|--------|---------------------------------------------------|

| 1  | P_CS1 | ON     | ON : 0x0200_0000 – 0x03FF_FFFF 空間を選択<br>OFF: 切り離し |

| 2  | P_CS2 | OFF    | ON : 0x0400_0000 – 0x07FF_FFFF 空間を選択<br>OFF: 切り離し |

| 3  | P_CS3 | OFF    | ON : 0x0800_0000 – 0x0BFF_FFFF 空間を選択<br>OFF: 切り離し |

| 4  |       | OFF    | 未使用                                               |

#### 4.6. スイッチ 4 (SW4)

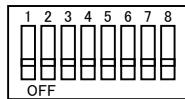

PLD に接続された汎用DIPスイッチです。プログラムで読み出すことが可能です。

アドレス、ビット配置については [【 7.2.7 REG6\\_MISC \(0xF900\\_0018\)】](#)を参照してください。

S1 S2 S3 S4 S5 S6 S7 S8

| 番号 | 信号名 | 出荷時の設定 | 機能                    |

|----|-----|--------|-----------------------|

| 1  | S1  | OFF    | ON : 0 OFF: 1 が読み出せます |

| 2  | S2  | OFF    | ON : 0 OFF: 1 が読み出せます |

| 3  | S3  | OFF    | ON : 0 OFF: 1 が読み出せます |

| 4  | S4  | OFF    | ON : 0 OFF: 1 が読み出せます |

| 5  | S5  | OFF    | ON : 0 OFF: 1 が読み出せます |

| 6  | S6  | OFF    | ON : 0 OFF: 1 が読み出せます |

| 7  | S7  | OFF    | ON : 0 OFF: 1 が読み出せます |

| 8  | S8  | OFF    | ON : 0 OFF: 1 が読み出せます |

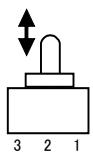

#### 4.7. スイッチ 5 (SW5)

CANのウェイクアップ用のトグルスイッチです。中間位置でオフ(CAN\_WAKE-へHレベルを出力)、左又は右にレバーを倒すとオン(CAN\_WAKE-へLレベルを出力)になります。ただし 左に倒した場合モ

一メンタリーとなり手を離すとレバーは中間位置に戻るようになっています。

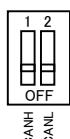

#### 4.8. スイッチ 6,7 (SW6,SW7)

CANラインの 終端抵抗の接続を ON 又はOFFするスイッチです。SW6 が CAN0 用、SW7 が CAN1 用です。CANL、CANH 個別にスイッチが設けられていますが、1と2は同じ設定にしてください。

| 番号 | 信号名  | 出荷時の設定 | 機能                          |

|----|------|--------|-----------------------------|

| 1  | CANH | OFF    | ON : 62Ω 抵抗で終端<br>OFF: 切り離し |

| 2  | CANL | OFF    | ON : 62Ω 抵抗で終端<br>OFF: 切り離し |

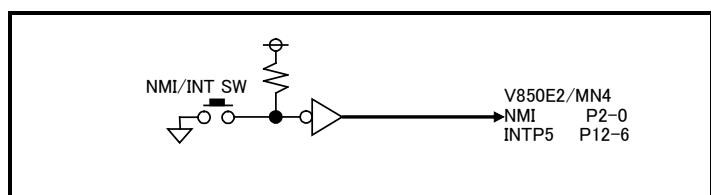

#### 4.9. スイッチ 8,9 (SW8,SW9)

NMI(SW8) 又は INTP5(SW9)へHレベルを出力するプッシュスイッチです。通常状態では、L レベルで、押したときだけ H レベルになります。マニュアル操作により CPU へ割り込みを入れたいときに使用します。

NMI/INT の回路イメージを下図に示します。

#### 4.10. クロック

V850E2/MN4 へクロックを供給する回路です。OSC1発振器又は クリスタル振動子のいずれかを選択できるようになっていますが、クリスタル振動子でのみご使用ください。オシレータでの動作は保証されていません。

| No          | 素子   | 周波数             | 用途                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

|-------------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|---------|------|------|---------|------|-----------------|---------|------|--------|-------------|------|---------|-------------|------|---------|

| OSC1        | 発振器  | ---             | 使用できません。                                                                                                                                                                                                                                                                                                                                                                                                                              |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| Xtal        | 振動子  | 10MHz           | Xtal の設定でのみご使用ください。                                                                                                                                                                                                                                                                                                                                                                                                                   |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

|             |      |                 | <table border="1"> <thead> <tr> <th>設定箇所</th> <th>発振器</th> <th>Xtal</th> </tr> </thead> <tbody> <tr> <td>JX1:2-3</td> <td>ショート</td> <td>オープン</td> </tr> <tr> <td>JX1:2-4</td> <td>オープン</td> <td>Xtal<br/>(10MHz)</td> </tr> <tr> <td>JX2:2-4</td> <td>オープン</td> <td>R(未実装)</td> </tr> <tr> <td>JX1:1-JX2:1</td> <td>オープン</td> <td>C(10pF)</td> </tr> <tr> <td>JX1:5-JX2:5</td> <td>オープン</td> <td>C(10pF)</td> </tr> </tbody> </table> | 設定箇所 | 発振器 | Xtal | JX1:2-3 | ショート | オープン | JX1:2-4 | オープン | Xtal<br>(10MHz) | JX2:2-4 | オープン | R(未実装) | JX1:1-JX2:1 | オープン | C(10pF) | JX1:5-JX2:5 | オープン | C(10pF) |

| 設定箇所        | 発振器  | Xtal            |                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| JX1:2-3     | ショート | オープン            |                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| JX1:2-4     | オープン | Xtal<br>(10MHz) |                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| JX2:2-4     | オープン | R(未実装)          |                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| JX1:1-JX2:1 | オープン | C(10pF)         |                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| JX1:5-JX2:5 | オープン | C(10pF)         |                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

|             |      |                 | 出荷時の状態(Xtal実装)でご使用ください。                                                                                                                                                                                                                                                                                                                                                                                                               |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| OSC2        | 発振器  | 48MHz           | USB専用 クロック<br>(JP7 1-2ショート時)<br>デフォルトではJP7 1-2がショートされています                                                                                                                                                                                                                                                                                                                                                                             |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| OSC3        | 発振器  | 50MHz           | LCDC IC用 クロック                                                                                                                                                                                                                                                                                                                                                                                                                         |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| OSC4        | 発振器  | 12.288MHz       | コーデック IC用 クロック                                                                                                                                                                                                                                                                                                                                                                                                                        |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

| OSC5        | 発振器  | 25MHz           | LAN PHY IC用 クロック                                                                                                                                                                                                                                                                                                                                                                                                                      |      |     |      |         |      |      |         |      |                 |         |      |        |             |      |         |             |      |         |

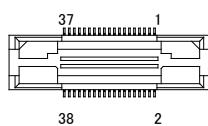

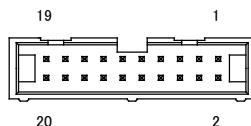

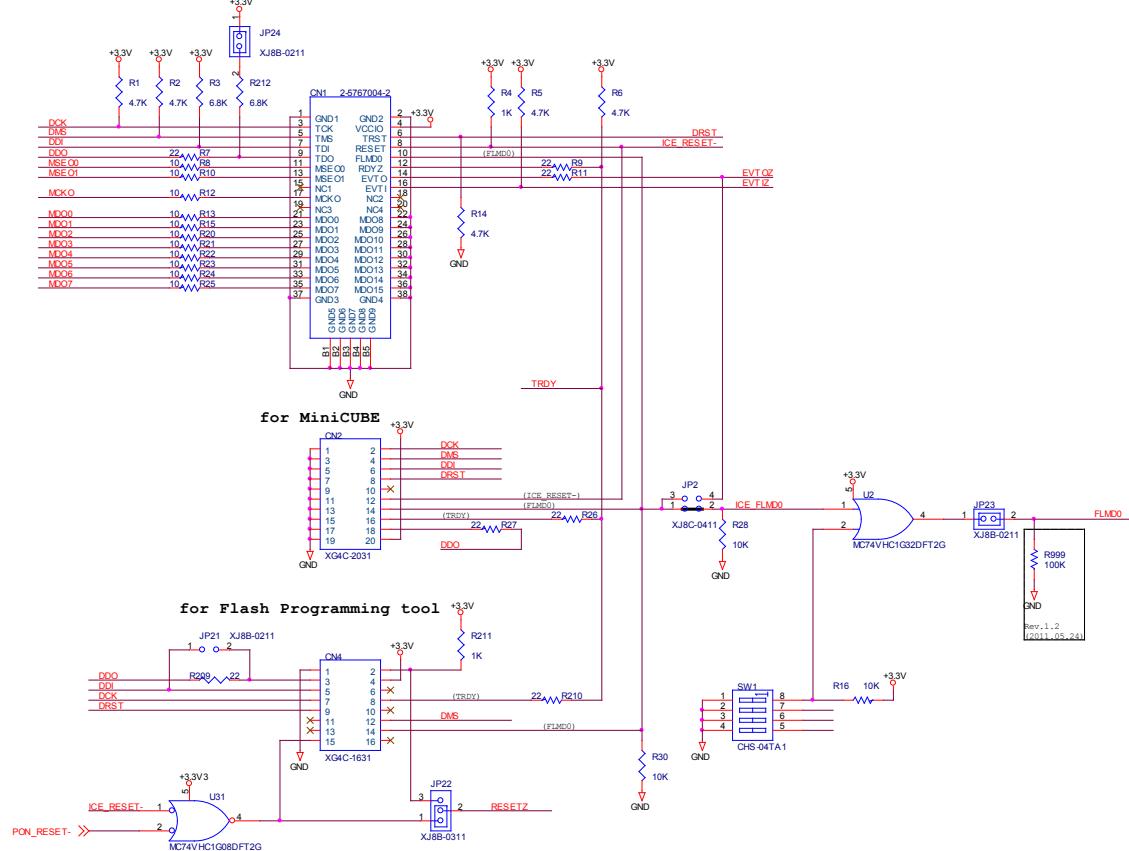

#### 4.11. デバッガ用コネクタ(CN1)

オンチップデバッガ(ICE)用のコネクタです。(Appendix.A 参照)

| Pin | 信号    | Pin | 信号    |

|-----|-------|-----|-------|

| 1   | GND1  | 2   | GND2  |

| 3   | TCK   | 4   | VCCIO |

| 5   | TMS   | 6   | TRST  |

| 7   | TDI   | 8   | RESET |

| 9   | TDO   | 10  | FLMD0 |

| 11  | MSEO0 | 12  | RDYZ  |

| 13  | MSEO1 | 14  | EVTO  |

| 15  | NC1   | 16  | EVTI  |

| 17  | MCKO  | 18  | NC2   |

| 19  | NC3   | 20  | NC4   |

| 21  | MDO0  | 22  | MDO8  |

| 23  | MDO1  | 24  | MDO9  |

| 25  | MDO2  | 26  | MDO10 |

| 27  | MDO3  | 28  | MDO11 |

| 29  | MDO4  | 30  | MDO12 |

| 31  | MDO5  | 32  | MDO13 |

| 33  | MDO6  | 34  | MDO14 |

| 35  | MDO7  | 36  | MDO15 |

| 37  | GND3  | 38  | GND4  |

CN1

メーカー : タイコエレクトロニクスアンプ®

型番 : 2-5767004-2

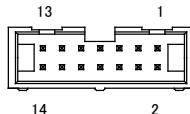

#### 4.12. MiniCUBE 用コネクタ(CN2)

MiniCUBE(ICE)用のコネクタです。(Appendix.A 参照)

| Pin | 信号  | Pin | 信号    |

|-----|-----|-----|-------|

| 1   | GND | 2   | DCK   |

| 3   | GND | 4   | DMS   |

| 5   | GND | 6   | DDI   |

| 7   | GND | 8   | DRST  |

| 9   | GND | 10  | N.C   |

| 11  | GND | 12  | RESET |

| 13  | GND | 14  | FLMD0 |

| 15  | GND | 16  | TRDY  |

| 17  | GND | 18  | DDO   |

| 19  | GND | 20  | VDD   |

CN2

メーカー : OMRON

型番 : XG4C-2031

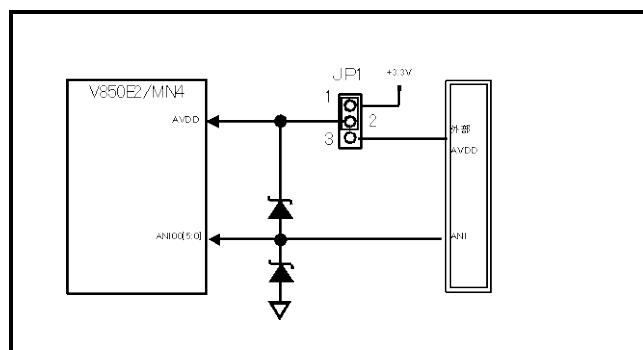

#### 4.13. アナログ信号入力コネクタ(CN3)

V850E2/MN4 内蔵のサンプル&ホールド付き 6ch AD コンバータのアナログ入力用のコネクタです。

内部電源(3.3V)使用時は分解能 10 ビット、外部から+5Vを供給した場合は分解能を 12 ビットにすることができます。入力はショットキーダイオードで AVDD に(内部の 3.3V、または外部電源)にクランプされており、デフォルトでは内部の 3.3V(JP1 は 1-2 間がショート)です。

| Pin | 信号         | Pin | 信号  |

|-----|------------|-----|-----|

| 1   | 外部 AVDD 入力 | 2   | GND |

| 3   | ANIO0 入力   | 4   | GND |

| 5   | ANIO1 入力   | 6   | GND |

| 7   | ANIO2 入力   | 8   | GND |

| 9   | ANIO3 入力   | 10  | GND |

| 11  | ANIO4 入力   | 12  | GND |

| 13  | ANIO5 入力   | 14  | GND |

CN3

メーカー : OMRON

型番 : XG4C-1431

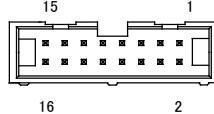

#### 4.14. フラッシュプログラミングツール用コネクタ(CN4)

V850E2/MN4 の内蔵フラッシュメモリプログラミング用のコネクタです。(Appendix.A 参照)

| Pin | 信号    | Pin | 信号    |

|-----|-------|-----|-------|

| 1   | GND   | 2   |       |

| 3   | DDO   | 4   | VDD   |

| 5   | DDI   | 6   | N.C   |

| 7   | DCK   | 8   | TRDY  |

| 9   | DRST  | 10  | N.C   |

| 11  | N.C   | 12  | DMS   |

| 13  | N.C   | 14  | FLMD0 |

| 15  | RESET | 16  | N.C   |

CN4

メーカー : OMRON

型番 : XG4C-1631

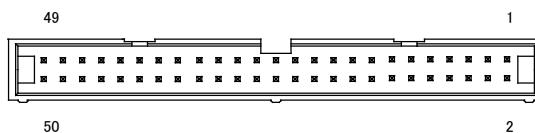

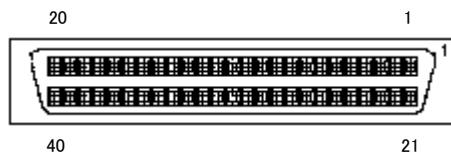

#### 4.15. プライマリバス拡張用コネクタ(CN5,CN6)

V850E2/MN4 のプライマリバス信号を外部で観測するためのコネクタです。

ピン配置は以下の通りです。機能の中で P\_A0-P\_A23 はアドレスを、P\_D0-P\_D31 はデータバスを示しています。

| ピン番号 | 信号名     | 機能   | ピン番号 | 信号名     | 機能    |

|------|---------|------|------|---------|-------|

| 1    | GND     |      | 1    | GND     |       |

| 2    | EX_P3_0 | P_A0 | 2    | EX_P4_0 | P_A16 |

| 3    | EX_P3_1 | P_A1 | 3    | EX_P4_1 | P_A17 |

| 4    | EX_P3_2 | P_A2 | 4    | EX_P4_2 | P_A18 |

| 5    | EX_P3_3 | P_A3 | 5    | EX_P4_3 | P_A19 |

| 6    | GND     |      | 6    | GND     |       |

| ピン番号 | 信号名      | 機能    | ピン番号 | 信号名      | 機能                   |

|------|----------|-------|------|----------|----------------------|

| 7    | EX_P3_4  | P_A4  | 7    | EX_P4_4  | P_A20                |

| 8    | EX_P3_5  | P_A5  | 8    | EX_P4_5  | P_A21                |

| 9    | EX_P3_6  | P_A6  | 9    | EX_P4_6  | P_A22                |

| 10   | EX_P3_7  | P_A7  | 10   | EX_P4_7  | P_A23                |

| 11   | GND      |       | 11   | GND      |                      |

| 12   | EX_P3_8  | P_A8  | 12   | EX_P4_8  | P_CS1-               |

| 13   | EX_P3_9  | P_A9  | 13   | EX_P4_9  | P_CS2-               |

| 14   | EX_P3_10 | P_A10 | 14   | EX_P4_10 | P_CS3-               |

| 15   | EX_P3_11 | P_A11 | 15   | EX_P4_11 | P_WAIT               |

| 16   | GND      |       | 16   | GND      |                      |

| 17   | EX_P3_12 | P_A12 | 17   | EX_P4_12 | P_HLD <sub>A</sub> K |

| 18   | EX_P3_13 | P_A13 | 18   | EX_P4_13 | P_HLD <sub>R</sub> Q |

| 19   | EX_P3_14 | P_A14 | 19   | N.C      |                      |

| 20   | EX_P3_15 | P_A15 | 20   | N.C      |                      |

| 21   | GND      |       | 21   | GND      |                      |

| 22   | EX_P1_0  | P_D16 | 22   | EX_P2_1  | P_LLBE-              |

| 23   | EX_P1_1  | P_D17 | 23   | EX_P2_2  | P_LUBE-              |

| 24   | EX_P1_2  | P_D18 | 24   | EX_P2_3  | P_ULBE-              |

| 25   | EX_P1_3  | P_D19 | 25   | EX_P2_4  | P_UUBE-              |

| 26   | GND      |       | 26   | GND      |                      |

| 27   | EX_P1_4  | P_D20 | 27   | EX_P2_5  | RD-                  |

| 28   | EX_P1_5  | P_D21 | 28   | EX_P2_6  | P_BUSCLK             |

| 29   | EX_P1_6  | P_D22 | 29   | EX_P2_7  | WR-                  |

| 30   | EX_P1_7  | P_D23 | 30   | N.C      |                      |

| 31   | GND      |       | 31   | GND      |                      |

| 32   | EX_P1_8  | P_D24 | 32   | EX_P0_0  | P_D0                 |

| 33   | EX_P1_9  | P_D25 | 33   | EX_P0_1  | P_D1                 |

| 34   | EX_P1_10 | P_D26 | 34   | EX_P0_2  | P_D2                 |

| 35   | EX_P1_11 | P_D27 | 35   | EX_P0_3  | P_D3                 |

| 36   | GND      |       | 36   | GND      |                      |

| 37   | EX_P1_12 | P_D28 | 37   | EX_P0_4  | P_D4                 |

| 38   | EX_P1_13 | P_D29 | 38   | EX_P0_5  | P_D5                 |

| 39   | EX_P1_14 | P_D30 | 39   | EX_P0_6  | P_D6                 |

| 40   | EX_P1_15 | P_D31 | 40   | EX_P0_7  | P_D7                 |

| 41   | GND      |       | 41   | GND      |                      |

| 42   | N.C      |       | 42   | EX_P0_8  | P_D8                 |

| 43   | N.C      |       | 43   | EX_P0_9  | P_D9                 |

| 44   | N.C      |       | 44   | EX_P0_10 | P_D10                |

| 45   | N.C      |       | 45   | EX_P0_11 | P_D11                |

| 46   | GND      |       | 46   | GND      |                      |

| 47   | N.C      |       | 47   | EX_P0_12 | P_D12                |

| 48   | N.C      |       | 48   | EX_P0_13 | P_D13                |

| 49   | N.C      |       | 49   | EX_P0_14 | P_D14                |

| 50   | N.C      |       | 50   | EX_P0_15 | P_D15                |

| CN5  |          |       | CN6  |          |                      |

メーカー :OMRON

型番 :XG4C-5031

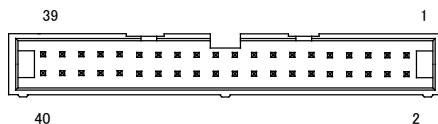

#### 4.16. テストピン用コネクタ(CN7)

TP 信号がこのコネクタに集められています。

| Pin | 信号     | Pin | 信号     |

|-----|--------|-----|--------|

| 1   | TP7_0  | 2   | TP7_1  |

| 3   | TP7_2  | 4   | TP7_3  |

| 5   | GND    | 6   | TP7_4  |

| 7   | TP7_5  | 8   | TP7_6  |

| 9   | TP7_7  | 10  | GND    |

| 11  | TP7_8  | 12  | TP7_9  |

| 13  | TP7_10 | 14  | TP7_11 |

| 15  | GND    | 16  | TP7_12 |

| 17  | TP7_13 | 18  | TP7_14 |

| 19  | TP7_15 | 20  | GND    |

| 21  | TP8_0  | 22  | TP8_1  |

| 23  | TP8_2  | 24  | TP8_3  |

| 25  | GND    | 26  | TP8_4  |

| 27  | TP8_5  | 28  | TP8_6  |

| 29  | TP8_7  | 30  | GND    |

| 31  | TP8_8  | 32  | TP8_9  |

| 33  | TP8_10 | 34  | TP8_11 |

| 35  | GND    | 36  | TP8_12 |

| 37  | TP8_13 | 38  | TP8_14 |

| 39  | TP8_15 | 40  | GND    |

CN7

メーカー :OMRON

型番 :XG4C-4031

#### 4.17. PLD プログラム用コネクタ(CN8)

PLD(EPM570T100C5N)のプログラミング用信号が基板のスルホールとして用意されています。アルテラ社 バイトブラスタとは形状が異なるので変換アダプタを使用してJTAGで接続します。

工場出荷時用です。

| Pin | 信号    |

|-----|-------|

| 1   | TCK   |

| 2   | TMS   |

| 3   | TDI   |

| 4   | TDO   |

| 5   | +3.3V |

| 6   | GND   |

CN8

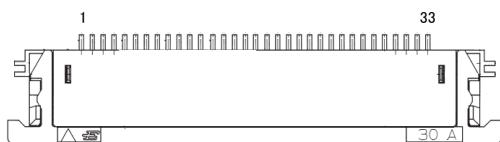

#### 4.18. LCD パネルモジュール IF コネクタ(CN9)

TFTカラー液晶モジュール(NL3224BC35-20) 5.5 型 QVGA を接続することができます。コネクタには LCD コントローラ(S1D13706)の信号が接続されています。

| Pin | 信号     | Pin | 信号     |

|-----|--------|-----|--------|

| 1   | GND    | 2   | CLK    |

| 3   | H SYNC | 4   | V SYNC |

| 5   | GND    | 6   | R0     |

| 7   | R1     | 8   | R2     |

| 9   | R3     | 10  | R4     |

| 11  | R5     | 12  | GND    |

| 13  | G0     | 14  | G1     |

| 15  | G2     | 16  | G3     |

| 17  | G4     | 18  | G5     |

| 19  | GND    | 20  | B0     |

| 21  | B1     | 22  | B2     |

| 23  | B3     | 24  | B4     |

| 25  | B5     | 26  | GND    |

| 27  | DE     | 28  | VCC    |

| 29  | VCC    | 30  | DPSH   |

| 31  | DPSV   | 32  | Q/V    |

| 33  | GND    |     |        |

CN9

メーカー :京セラエルコ

型番 :08-6260-033-340-829+

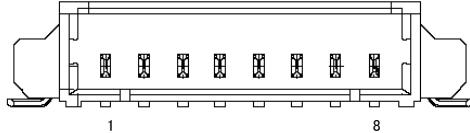

#### 4.19. LCD パネルバックライト用コネクタ(CN10)

バックライト用インバータ(55PW131)を接続することができます。

| Pin | 信号    |

|-----|-------|

| 1   | VDDB0 |

| 2   | VDDB1 |

| 3   | GNDB0 |

| 4   | GNDB1 |

| 5   | BRTC  |

| 6   | BRTI  |

| 7   | GNDB2 |

| 8   | AM    |

CN10

メーカー :モレックス

型番 :53261-0871

#### 4.20. ステレオジャックコネクタ(CN11,CN12,CN13)

オーディオ コーデックIC用入出力として、下記のステレオジャックを搭載しています。

CN11-CN13

メーカー : ホシデン

型番 : HSJ1636-01054

適合プラグ

3.5mm ミニプラグ

#### 4.21. LAN コネクタ(CN14)

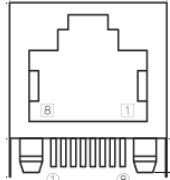

10BASE-T/100BASE-T 用の RJ45 コネクタが用意されています。このコネクタはトランシス内蔵となっています。

| Pin | 信号  |

|-----|-----|

| 1   | TD+ |

| 2   | TD- |

| 3   | RD+ |

| 4   | CT1 |

| 5   | CT2 |

| 6   | RD- |

| 7   | CT3 |

| 8   | CT4 |

CN14

メーカー : TDK

型番 : TLA-6T717W

#### 4.22. PHY ドーターカードコネクタ(CN15)

本ボードに搭載されている LAN8700iC 以外の PHY チップを使用できるようデーターカードコネクタの実装ホールが用意されていますが、テスト用です。コネクタは未実装であり、動作保証はされていません。

| Pin | 信号     | Pin | 信号         |

|-----|--------|-----|------------|

| 1   | +5V[3] | 21  | +5V[2]     |

| 2   | MDIO   | 22  | COMMON[18] |

| 3   | MDC    | 23  | COMMON[17] |

| 4   | RXD3   | 24  | COMMON[16] |

| 5   | RXD2   | 25  | COMMON[15] |

| 6   | RXD1   | 26  | COMMON[14] |

| 7   | RXD0   | 27  | COMMON[13] |

| 8   | RX_DV  | 28  | COMMON[12] |

| 9   | RX_CLK | 29  | COMMON[11] |

| 10  | RX_ER  | 30  | COMMON[10] |

| 11  | TX_ER  | 31  | COMMON[9]  |

| 12  | TX_CLK | 32  | COMMON[8]  |

| 13  | TX_EN  | 33  | COMMON[7]  |

| 14  | TXD0   | 34  | COMMON[6]  |

| 15  | TXD1   | 35  | COMMON[5]  |

| 16  | TXD2   | 36  | COMMON[4]  |

| 17  | TXD3   | 37  | COMMON[3]  |

| 18  | COL    | 38  | COMMON[2]  |

| 19  | CRS    | 39  | COMMON[1]  |

| 20  | +5V[4] | 40  | +5V[1]     |

CN15

メーカー : タイコエレクトロニクスアンプ<sup>®</sup>

型番 : 6-5174215-2

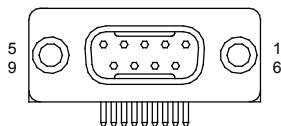

#### 4.23. CAN コネクタ(CN16,CN17)

CPU に搭載している CAN デバイスコントローラのインターフェース用コネクタです。

2 チャンネル用意しています。

| Pin | 信号   |

|-----|------|

| 1   |      |

| 2   | CANL |

| 3   | GND  |

| 4   |      |

| 5   |      |

| 6   |      |

| 7   | CANH |

| 8   |      |

| 9   |      |

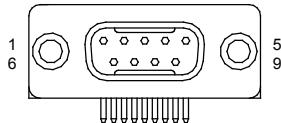

CN16/CN17

メーカー :OMRON

型番 :XM3B-0922-132

#### 4.24. UART コネクタ(CN18,CN19)

CPU に搭載されている UART デバイスコントローラのインターフェース用のコネクタです。

2 チャンネル用意しています。

| Pin | 信号  |

|-----|-----|

| 1   | DCD |

| 2   | RX  |

| 3   | TX  |

| 4   | DTR |

| 5   | GND |

| 6   | DSR |

| 7   | RTS |

| 8   | CTS |

| 9   | RI  |

CN18/CN19

メーカー :OMRON

型番 :XM2C-0912-132

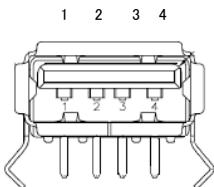

#### 4.25. USB-HOST コネクタ(CN20)

CPU に搭載されている USB ホストコントローラのインターフェースコネクタです。

コネクタは標準 A レセプタクルです。

| Pin | 信号    |

|-----|-------|

| 1   | VBus  |

| 2   | -Data |

| 3   | +Data |

| 4   | GND   |

CN20

メーカー :タイコエレクトロニクスアンフ

型番 :292303-4

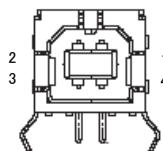

#### 4.26. USB-FUNCTION コネクタ(CN21)

CPU に搭載されている USB ファンクションコントローラのインターフェースコネクタです。

コネクタは標準 B レセプタクルです。

| Pin | 信号    |

|-----|-------|

| 1   | VBus  |

| 2   | -Data |

| 3   | +Data |

| 4   | GND   |

CN21

メーカー :AMP

型番 :292304-1

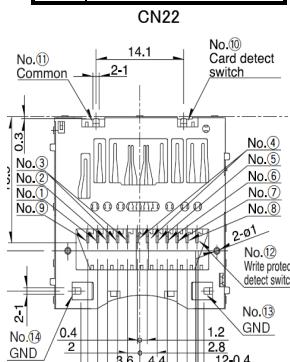

#### 4.27. SD カード用コネクタ(CN22)

SD カードのインターフェース用のコネクタです。

| Pin | 信号             |

|-----|----------------|

| 1   | CD/DAT3(CS-)   |

| 2   | CMD(Datain)    |

| 3   | VSS            |

| 4   | VDD            |

| 5   | CLK(CLK)       |

| 6   | VSS            |

| 7   | DATA0(Dataout) |

| 8   | DAT1           |

| 9   | DAT2           |

| 10  | CD             |

| 11  | COM            |

| 12  | WP             |

| 13  | GND            |

| 14  | GND            |

CN22

メーカー :ALPS

型番 :SCDA3A0202

#### 4.28. AVDD 切り替えジャンパ(JP1)

AVDD 電源を 内部から供給(1-2 間をショート)か 外部から CN3 コネクタを通して供給(2-3 間をショート)するかを選択します。内部を選択すると AVDD として+3.3V が供給されます。外部からは最大+5V まで供給することができます。

デフォルトでは1-2間をショートしています。

#### 4.29. ジャンパ(JP2)

MiniCUBE 用コネクタ(CN2)の 14pin に接続する信号を設定します。1-2 間をショートで FLMD0 信号が、3-4 間ショートで EVTOZ 信号が接続されます。

デフォルトでは 1-2 間をショートして FLMD0 信号が接続されています。

#### 4.30. プライマリ SRAM バス幅切り替えジャンパ(JP3,JP4)

プライマリ SRAM を 32 ビットバスで使用するとき(1-2 間をショート)、16 ビットバスで使用するとき(2-3 間をショート)します。JP3、JP4 共に同じ設定でなければなりません。

デフォルトでは 1-2 間をショートして 32 ビットバスとなっています。

#### 4.31. P12-8 機能選択ジャンパ(JP6)

CPU P12-8 端子の機能選択です。S1\_HA25(A25 として SDRAM で使用)として使用するとき(1-2 間をショート)、CODEC の SDA として使用するとき(2-3 間をショート)します。

デフォルトでは 1-2 間をショートして S1\_HA25 となっています。

#### 4.32. P13-0 機能選択ジャンパ(JP7)

CPU P13-0 端子の機能選択。USB クロック(48MHz)の入力として使用するとき(1-2 間をショート)、S\_DMARQ0 入力として使用するとき(2-3 間をショート)します。

デフォルトでは 1-2 間をショートして USB クロック入力としています。

#### 4.33. P13-5 機能選択ジャンパ(JP8)

P13-5 の機能選択。CAN0RXD として使用するとき(1-2 間をショート)、RXD1F として使用するとき(2-3 間をショート)します。

デフォルトでは 1-2 間をショートとして CAN0RXD となっています。

#### 4.34. SDRAM バス幅切り替えジャンパ(JP9)

SDRAM を 16 ビットバスで使用するとき(1-2 間をショート)、32 ビットバスで使用するとき(2-3 間をショート)します。

デフォルトでは 1-2 間をショートして 16 ビットバス幅となっています。

#### 4.35. セカンダリ SRAM バス幅切り替えジャンパ(JP10,JP11)

セカンダリ SRAM を 32 ビットバスで使用するとき(1-2 間をショート)、16 ビットバスで使用するとき(2-3 間をショート)します。JP10、JP11 共に同じ設定でなければなりません。

デフォルトでは 1-2 間をショートして 32 ビットバスとなっています。

#### 4.36. PHONE/LINE 出力切り替えジャンパ(JP12,JP13)

RIGHT 側(JP12)又は LEFT 側(JP13)を PHONE 出力に設定時(1-2 間をショート)、LINE 出力に設定時(2-3 間をショート)します。JP12、JP13 は同じ設定にしてください。

デフォルトでは 1-2 間をショートし、PHONE 出力となっています。

#### 4.37. LAN8700iC バス切り離し選択ジャンパ(JP14)

基板上の LAN8700iC をバスから切り離したいときショートし、使用のときオープンとします。

デフォルトではオープンで基板上の LAN8700iC が有効となっています。

#### 4.38. グランド接続切り替えジャンパ(JP15,JP16,JP17,JP18)

CAN コネクタの 5 番及び 6 番ピンをグランドに接続するかどうかを選択します。ショートするとグランドに接続できます。

JP15 は CN16-5、JP16 は CN16-6、JP17 は CN17-5、JP18 は CN17-6 に対応しています。

デフォルトでは JP15,JP17 がショート、JP16,JP18 がオープンとなっています。

#### 4.39. DSR-DTR ループバック切り替えジャンパ(JP19,JP20)

UART コネクタ CN18 又は CN19 において DSR と DTR 信号をループバックしたいときショートします。

JP19 は CN18 用、JP20 は CN19 用です。

デフォルトでは共にショートされています。

#### 4.40. フラッシュプログラマ DDO/DDI 接続方法選択ジャンパ(JP21)

フラッシュプログラマコネクタの DDO と DDI をつなぎ、双方向信号として使用するときショートします。

デフォルトではオープンで DDO、DDI 独立になっています。

#### 4.41. リセット信号選択ジャンパ(JP22)

CPU リセット信号を選択できます。通常 1-2 間をショートして使用しますが、2-3 間ショートしますとフラッシュプログラマ経由からリセット信号が選択されます。

デフォルトでは 1-2 間がショートされています。

#### 4.42. ジャンパ(JP23)

ショート時 FLMD0 がツールから制御可能となります。

デフォルトではショートされています。

#### 4.43. TDO プルアップ選択ジャンパ(JP24)

オンボードデバッグ用コネクタの TDO 端子をプルアップするとき ショートします。

デフォルトではショートされプルアップされています。

## 5. ハードウェア・リファレンス

RTE-V850E2R/MN4-EB のハードウェアの仕様について記します。

### 5.1. メモリ・I/O のマップ

ボードのメモリと I/O の割り付けは、以下の通りです。

|             |                              |                       |

|-------------|------------------------------|-----------------------|

| 0xFFFF_FFFF | 内蔵周辺I/O領域                    | 44KByte               |

| 0xFFFF_5000 | 予約域                          | 8MByte                |

| 0xFFFF_4FFF | 内蔵周辺I/O領域                    | 4MByte                |

| 0xFF84_0000 | 予約域                          | 6MByte                |

| 0xFF83_FFFF | RAM1領域                       | 64KByte               |

| 0xFF40_0000 | 予約域                          | 2MByte                |

| 0xFF3F_FFFF | RAM2領域                       | 64KByte               |

| 0xFE00_0000 | 予約域                          | 76MByte               |

| 0xFEDF_FFFF | 内蔵周辺I/O領域                    | 1KByte                |

| 0xFEDF_0000 | 予約域                          | 3KByte                |

| 0xFEDE_FFFF | 内蔵周辺I/O領域                    | 9KByte                |

| 0xFEC0_0000 | 予約域                          | 187KByte              |

| 0xFEBF_FFFF | 内蔵周辺I/O領域                    | 5KByte                |

| 0xFEBF_0000 | 予約域                          | 960KByte              |

| 0xFEBE_FFFF | EX-RAM領域                     | 64KByte               |

| 0xFA00_0000 | セカンダリJCS3領域<br>未使用           | 2MByte                |

| 0xF9FF_FFFF | セカンダリJCS2領域<br>LCD内ポート       | 2MByte                |

| 0xF993_3400 | セカンダリJCS1領域<br>PLD内ポート       | 4MByte                |

| 0xF993_33FF | セカンダリJCS0領域<br>外部SRAM ③      | 16MByte<br>(4MByte)   |

| 0xF993_3000 | セカンダリSDRAM CS領域<br>外部SDRAM ② | 128MByte<br>(64MByte) |

| 0xF993_2FFF | 予約域                          | 64MByte               |

| 0xF993_2400 | プライマリJCS3領域<br>外部SRAM ①      | 64MByte<br>(4MByte)   |

| 0xF993_23FF | プライマリJCS2領域<br>外部 SRAM ①     | 64MByte<br>(4MByte)   |

| 0xF993_0000 | プライマリJCS1領域<br>外部 SRAM ①     | 32MByte<br>(4MByte)   |

| 0xF992_FFFF | 予約域                          | 30MByte               |

| 0xF990_1400 | 内蔵フラッシュメモリ領域                 | 2MByte                |

| 0xF990_13FF |                              |                       |

| 0xF990_0000 |                              |                       |

| 0xF98F_FFFF |                              |                       |

| 0xF981_0000 |                              |                       |

| 0xF980_FFFF |                              |                       |

| 0xF980_0000 |                              |                       |

| 0xF97F_FFFF |                              |                       |

| 0xF960_0000 |                              |                       |

| 0xF95F_FFFF |                              |                       |

| 0xF940_0000 |                              |                       |

| 0xF93F_FFFF |                              |                       |

| 0xF900_0000 |                              |                       |

| 0xF8FF_FFFF |                              |                       |

| 0xF800_0000 |                              |                       |

| 0xF7FF_FFFF |                              |                       |

| 0xF000_0000 |                              |                       |

| 0xFFFF_FFFF |                              |                       |

| 0x0C00_0000 |                              |                       |

| 0x0BFF_FFFF |                              |                       |

| 0x0800_0000 |                              |                       |

| 0x07FF_FFFF |                              |                       |

| 0x0400_0000 |                              |                       |

| 0x03FF_FFFF |                              |                       |

| 0x0200_0000 |                              |                       |

| 0x01FF_FFFF |                              |                       |

| 0x0020_0000 |                              |                       |

| 0x001F_FFFF |                              |                       |

| 0x0000_0000 |                              |                       |

メモリ・I/O マップ

( )内の値は実際に使用される容量で 残りはイメージとなります。

- ① 外部SRAMは、16ビットバス幅を選択した場合、2Mバイトとなり、32ビットバス幅を選択した場合は4Mバイトとなります。又、外部SRAMは プライマリCS1からCS3までの領域のいずれか1つにのみ割り当てることができます。

- ② 外部SDRAMは、16ビットバス幅を選択した場合、32Mバイトとなり、32ビットバス幅を選択した場合は64Mバイトとなります。

- ③ 外部SRAMは、16ビットバス幅を選択した場合、2Mバイトとなり、32ビットバス幅を選択した場合は4Mバイトとなります。

**プライマリ CS1 領域 (SRAM)** :0x0200\_0000–0x03FF\_FFFF (32Mbyte)

**プライマリ CS2 領域 (SRAM)** :0x0400\_0000–0x07FF\_FFFF (64Mbyte)

**プライマリ CS3 領域 (SRAM)** :0x0800\_0000–0x0BFF\_FFFF (64Mbyte)

上記プライマリ CS1 から CS3 のいずれかの領域に SRAM を割り当てることができます。実際の SRAM の容量はバス幅の選択により異なり、16ビットバス幅を選択したときは2Mバイトとなり、32ビットバス幅を選択したときは4Mバイトとなります。実装容量以上の空間には、実メモリ空間のイメージが発生します。

**セカンダリ SDRAMCS 領域 (SDRAM)** :0xF000\_0000–0XF7FF\_FFFF (128Mbyte)

SDRAM が割り当てられています。実際の SDRAM の容量はバス幅の選択により異なり、16ビットバス幅を選択したときは32Mバイトとなり、32ビットバス幅を選択したときは64Mバイトとなります。実装容量以上の空間には、実メモリ空間のイメージが発生します。

**セカンダリ CS0 領域 (SRAM)** :0xF800\_0000–0xF8FF\_FFFF (16Mbyte)

SRAM が割り当てられています。実際の SRAM の容量はバス幅の選択により異なり、16ビットバス幅を選択したときは32Mバイトとなり、32ビットバス幅を選択したときは4Mバイトとなります。実装容量以上の空間には、実メモリ空間のイメージが発生します。

**セカンダリ CS1 領域 (PLD)** :0xF900\_0000–0xF93F\_FFFF (4Mbyte)

この領域は PLD の I/O ポートとして割り当てられています。実際に使用されている空間は、0xF900\_0000 から 0xF900\_001F まで、これを超える空間には実 I/O 空間のイメージが発生します。

**セカンダリ CS2 領域 (LCDC)** :0xF940\_0000–0xF95F\_FFFF (2Mbyte)

この領域は LCDC の I/O ポートとして割り当てられています。実際に使用されている空間は、0xF940\_0000 から 0xF941\_FFFF まで、これを超える空間には実 I/O 空間のイメージが発生します。

**セカンダリ CS3 領域 (使用不可)**

SDRAMCS として使用しているためこの領域は使用できません。

## 6. メモリ詳細

### 6.1. SRAM

16Mbit(1Mx16bit)SRAM 2 個をプライマリ CS 領域とセカンダリ CS 領域の 2 力所に配置しています。

このうちプライマリ領域の SRAM ではベースアドレスを変更することができます。(下図参照)

<DIPSW(SW3[4:1])の設定 vs 使用アドレス空間>

| SW3[4] | SW3[3] | SW3[2] | SW3[1] | 16bit バス時                       | 32bit バス時                       |

|--------|--------|--------|--------|---------------------------------|---------------------------------|

| ×      | OFF    | OFF    | ON     | 0x0200_0000<br> <br>0x021F_FFFF | 0x0200_0000<br> <br>0x023F_FFFF |

| ×      | OFF    | ON     | OFF    | 0x0400_0000<br> <br>0x041F_FFFF | 0x0400_0000<br> <br>0x043F_FFFF |

| ×      | ON     | OFF    | OFF    | 0x0800_0000<br> <br>0x081F_FFFF | 0x0800_0000<br> <br>0x083F_FFFF |

| ×      | OFF    | OFF    | OFF    |                                 | DISABLE                         |

× : don't care

SW3[1]～SW3[2]において 2 つ以上の同時ONは禁止されています。

それぞれの SRAM は 16Bit バスアクセス又は 32Bit バスアクセスを選択することができ、16Bit バスアクセス時は 2M バイト、32Bit バスアクセス時は 4M バイトの容量を持ちます。実装されている SRAM は Renesas 社製 uPD4416016G5-A15-9JF 又はサイプレス社製 CY7C1061DV33-10ZSXI です。

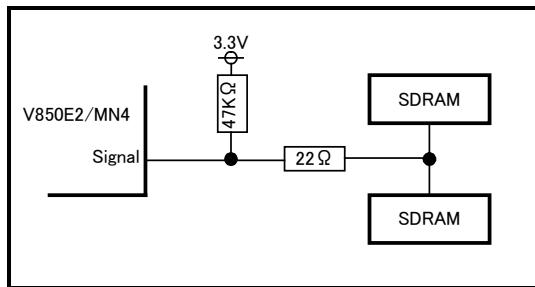

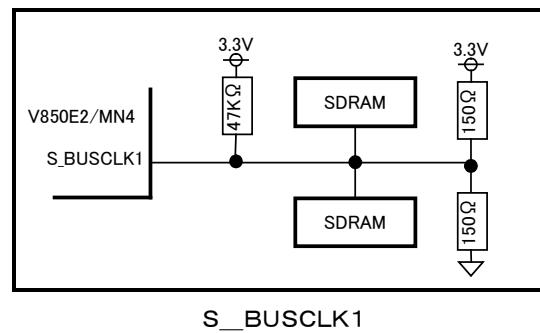

### 6.2. SDRAM

512Mbit(4Mx16bitx4bank) SDRAM を 3 個実装しています。但し 16Bit バス設定時は 1 個のみが有効となり 32Bit バス設定時は 2 個のみが有効となります。従って使用可能容量は 16Bit バス設定時は 32M バイトとなり 32Bit バス設定時は 64M バイトとなります。実装されている SDRAM は、Micron 社製 MT48LC16M16A2P-7E:IT です。

|          | 16bit バス時                       | 32bit バス時                       |

|----------|---------------------------------|---------------------------------|

| SDRAM 空間 | 0xF000_0000<br> <br>0xF1FF_FFFF | 0xF000_0000<br> <br>0xF3FF_FFFF |

配線トポロジを信号グループ別に下図に示します。

アドレス／データ／クロック／コマンド系

## 7. IOマップ

### 7.1. IO マップ一覧

バスに接続されている I/O は以下の通りです。

| アドレス                    | デバイス                  |

|-------------------------|-----------------------|

| 0xF900_0000-0xF900_001F | PLD レジスタ              |

| 0xF940_0000-0xF940_00B3 | LCD コントローラ コントロールレジスタ |

| 0xF942_0000-0xF943_FFFF | LCD コントローラ 表示メモリ      |

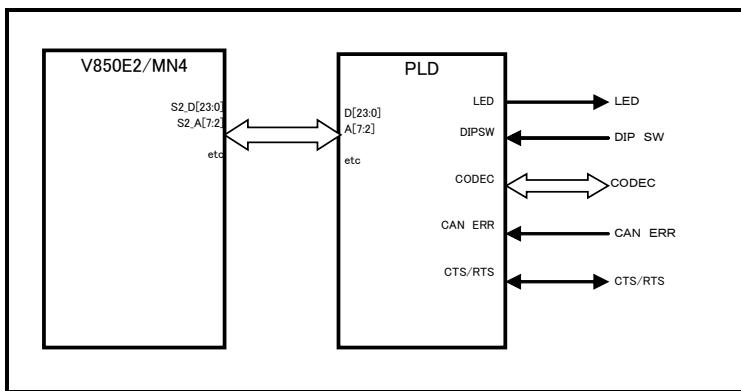

### 7.2. PLD (0xF900\_0000-0xF900\_001F)

V850E2/MN4 のセカンダリバスに接続され、オーディオ用 CODEC 制御、CAN/UART 補助信号、汎用 LED 汎用 DIPSW、SD カード補助信号のインターフェースとして機能します。

PLD 内のポートはセカンダリバス CS1 領域に割り付けられています。データは D0-D23 までが有効となっています。アクセス時は必ず 32 ビットでアクセスしてください。

以下に PLD 内部レジスタの詳細機能を示します。

#### 7.2.1. REG0 PLAY\_D (0xF900\_0000)

| Bit | Reset 時 | 名前     | R/W | 機能                                                                        |

|-----|---------|--------|-----|---------------------------------------------------------------------------|

| 23  |         | DI(23) | WO  | Lch、Rch 再生データ                                                             |

| 22  |         | DI(22) | WO  |                                                                           |

| 21  |         | DI(21) | WO  | DMA 使用<br>1回の DMAREQ0(low アクティブ)で、LchまたはRchの再生データを1つ書き込みます。               |

| 20  |         | DI(20) | WO  |                                                                           |

| 19  |         | DI(19) | WO  |                                                                           |

| 18  |         | DI(18) | WO  | DMA 未使用<br>PLAY_RUN = 1 後の PLAY_READY = 1 で、Lch または Rch の再生データを1つ書き込みます。  |

| 17  |         | DI(17) | WO  |                                                                           |

| 16  |         | DI(16) | WO  |                                                                           |

| 15  |         | DI(15) | WO  |                                                                           |

| 14  |         | DI(14) | WO  |                                                                           |

| 13  |         | DI(13) | WO  | モノラル再生<br>再生するチャネルの再生データを書き込み、再生しないチャネルには000000H を書き込みます。                 |

| 12  |         | DI(12) | WO  |                                                                           |

| 11  |         | DI(11) | WO  |                                                                           |

| 10  |         | DI(10) | WO  |                                                                           |

| 9   |         | DI(9)  | WO  |                                                                           |

| 8   |         | DI(8)  | WO  |                                                                           |

| 7   |         | DI(7)  | WO  |                                                                           |

| 6   |         | DI(6)  | WO  | 再生データは、最初の DMAREQ0 または PLAY_READY での書き込みから Lch, Rch, Lch, Rch... へ再生されます。 |

|   |  |       |    |                           |

|---|--|-------|----|---------------------------|

| 5 |  | DI(5) | WO | 緩衝用に 6 段の FIFO が内蔵されています。 |

| 4 |  | DI(4) | WO |                           |

| 3 |  | DI(3) | WO |                           |

| 2 |  | DI(2) | WO |                           |

| 1 |  | DI(1) | WO |                           |

| 0 |  | DI(0) | WO |                           |

### 7.2.2. REG1 PLAY\_C (0xF900\_0004)

| Bit | Reset 時 | 名前          | R/W | 機能                                                                                    |

|-----|---------|-------------|-----|---------------------------------------------------------------------------------------|

| 23  |         |             |     |                                                                                       |

| 22  |         |             |     |                                                                                       |

| 21  |         |             |     |                                                                                       |

| 20  |         |             |     |                                                                                       |

| 19  |         |             |     |                                                                                       |

| 18  |         |             |     |                                                                                       |

| 17  |         |             |     |                                                                                       |

| 16  |         |             |     |                                                                                       |

| 15  |         |             |     |                                                                                       |

| 14  |         |             |     |                                                                                       |

| 13  |         |             |     |                                                                                       |

| 12  |         |             |     |                                                                                       |

| 11  |         |             |     |                                                                                       |

| 10  |         |             |     |                                                                                       |

| 9   |         |             |     |                                                                                       |

| 8   |         |             |     |                                                                                       |

| 7   |         |             |     |                                                                                       |

| 6   |         |             |     |                                                                                       |

| 5   | 0       | PLAY_UDF    | RO  | 1:アンダーフローが発生しました。<br>Lch, Rch の再生データの書き込みが間に合わなかつたときに 1 となります。<br>再生開始時に自動的に 0 になります。 |

| 4   | 0       | DI_INT      | RO  | 未使用                                                                                   |

| 3   | 0       | PLAY        | W/R | 1:再生を開始します。<br>0:再生を停止します。                                                            |

| 2   | 0       | PLAY_DMAENB | W/R | 1:DMAREQ0 を使用します。<br>0:DMAREQ0 を使用しません。                                               |

| 1   | 0       | PLAY_RUN    | RO  | 1:再生中を示します。                                                                           |

| 0   | 0       | PLAY_READY  | RO  | 1:再生データの書き込みができます。<br>0:再生データの書き込みができません。                                             |

### 7.2.3. REG2 REC\_D (0xF900\_0008)

| Bit | Reset 時 | 名前     | R/W | 機能                                                               |

|-----|---------|--------|-----|------------------------------------------------------------------|

| 23  |         | DO(23) | RO  | Lch, Rch 録音データ                                                   |

| 22  |         | DO(22) | RO  |                                                                  |

| 21  |         | DO(21) | RO  | DMA 使用                                                           |

| 20  |         | DO(20) | RO  | DMAREQ1(Low アクティブ) で、Lch または Rch の録音データを読み出します。                  |

| 19  |         | DO(19) | RO  |                                                                  |

| 18  |         | DO(18) | RO  | DMA 未使用                                                          |

| 17  |         | DO(17) | RO  | REC_RUN = 1 後の REC_READY = 1 で、                                  |

| 16  |         | DO(16) | RO  | Lch または Rch の録音データを読み出します。                                       |

| 15  |         | DO(15) | RO  |                                                                  |

| 14  |         | DO(14) | RO  | MIC 録音                                                           |

| 13  |         | DO(13) | RO  | MIC 録音は、Lch のみ有効となり、Rch は、不定データとなります。                            |

| 12  |         | DO(12) | RO  |                                                                  |

| 11  |         | DO(11) | RO  | 録音データは、最初の DMAREQ1 または REC_READY から Lch, Rch, Lch, Rch... となります。 |

| 10  |         | DO(10) | RO  |                                                                  |

| 9   |         | DO(9)  | RO  |                                                                  |

| 8   |         | DO(8)  | RO  | 緩衝用に 6 段の FIFO が内蔵されています。                                        |

| 7   |         | DO(7)  | RO  |                                                                  |

| 6   |         | DO(6)  | RO  |                                                                  |

| 5   |         | DO(5)  | RO  |                                                                  |

| 4   |         | DO(4)  | RO  |                                                                  |

| 3   |         | DO(3)  | RO  |                                                                  |

| 2   |         | DO(2)  | RO  |                                                                  |

|   |  |       |    |  |

|---|--|-------|----|--|

| 1 |  | DO(1) | RO |  |

| 0 |  | DO(0) | RO |  |

#### 7.2.4. REG3 REC\_C (0xF900\_000C)

| Bit | Reset 時 | 名前         | R/W | 機能                                                                              |

|-----|---------|------------|-----|---------------------------------------------------------------------------------|

| 23  |         |            |     |                                                                                 |

| 22  |         |            |     |                                                                                 |

| 21  |         |            |     |                                                                                 |

| 20  |         |            |     |                                                                                 |

| 19  |         |            |     |                                                                                 |

| 18  |         |            |     |                                                                                 |

| 17  |         |            |     |                                                                                 |

| 16  |         |            |     |                                                                                 |

| 15  |         |            |     |                                                                                 |

| 14  |         |            |     |                                                                                 |

| 13  |         |            |     |                                                                                 |

| 12  |         |            |     |                                                                                 |

| 11  |         |            |     |                                                                                 |

| 10  |         |            |     |                                                                                 |

| 9   |         |            |     |                                                                                 |

| 8   |         |            |     |                                                                                 |

| 7   |         |            |     |                                                                                 |

| 6   |         |            |     |                                                                                 |

| 5   | 0       | REC_OVF    | RO  | 1:オーバーフローが発生しました。<br>Lch、Rchの録音データの読み出しが間に合わなかったときに1となります。<br>録音開始時に自動的に0となります。 |

| 4   |         | DO_INT     | RO  | 未使用                                                                             |

| 3   | 0       | REC        | W/R | 1:録音を開始します。<br>0:録音を停止します。                                                      |

| 2   | 0       | REC_DMAENB | W/R | 1:DMAREQ1を使用します。<br>0:DMAREQ1を使用しません。                                           |

| 1   | 0       | REC_RUN    | RO  | 1:録音中を示します。                                                                     |

| 0   | 0       | REC_READY  | RO  | 1:録音データがあります。<br>0:録音データがありません。                                                 |

#### 7.2.5. REG4 (0xF900\_0010)

未使用

#### 7.2.6. REG5 RSV (0xF900\_0014)

| Bit | Reset 時 | 名前 | R/W | 機能 |

|-----|---------|----|-----|----|

| 23  |         |    |     |    |

| 22  |         |    |     |    |

| 21  |         |    |     |    |

| 20  |         |    |     |    |

| 19  |         |    |     |    |

| 18  |         |    |     |    |

| 17  |         |    |     |    |

| 16  |         |    |     |    |

| 15  |         |    |     |    |

| 14  |         |    |     |    |

| 13  |         |    |     |    |

| 12  |         |    |     |    |

| 11  |         |    |     |    |

| 10  |         |    |     |    |

| 9   |         |    |     |    |

| 8   |         |    |     |    |

| 7   |         |    |     |    |

| 6   |         |    |     |    |

| 5   |         |    |     |    |

| 4   |         |    |     |    |

|   |   |              |     |                                                  |

|---|---|--------------|-----|--------------------------------------------------|

| 3 |   |              |     |                                                  |

| 2 |   |              |     |                                                  |

| 1 | 0 | CODEC_nRESET | W/R | O:CODEC をハードウェアリセット状態にします。<br>1:CODEC を動作状態にします。 |

| 0 | 0 | ADO          | W/R | 本ビットは0固定で使用してください。                               |

### 7.2.7. REG6 MISC (0xF900\_0018)

| Bit | Reset 時 | 名前     | R/W | 機能                                                            |

|-----|---------|--------|-----|---------------------------------------------------------------|

| 23  |         |        | RO  | 未使用                                                           |

| 22  |         |        |     |                                                               |

| 21  |         |        |     |                                                               |

| 20  |         |        |     |                                                               |

| 19  |         |        |     |                                                               |

| 18  |         |        |     |                                                               |

| 17  |         |        |     |                                                               |

| 16  |         |        |     |                                                               |

| 15  |         |        |     |                                                               |

| 14  |         |        |     |                                                               |

| 13  |         |        |     |                                                               |

| 12  |         |        |     |                                                               |

| 11  |         | SD_nWP | RO  | 入力ポート                                                         |

| 10  |         | SD_nCD | RO  |                                                               |

| 9   |         | CTS3F  | RO  |                                                               |

| 8   |         | CTS1F  | RO  |                                                               |

| 7   |         | SW(7)  | RO  | 入力ポート(スイッチ)<br>CPLD 内蔵プルアップ抵抗設定あり<br>Weak Pull-Up Resistor On |

| 6   |         | SW(6)  | RO  |                                                               |

| 5   |         | SW(5)  | RO  |                                                               |

| 4   |         | SW(4)  | RO  |                                                               |

| 3   |         | SW(3)  | RO  |                                                               |

| 2   |         | SW(2)  | RO  |                                                               |

| 1   |         | SW(1)  | RO  |                                                               |

| 0   |         | SW(0)  | RO  |                                                               |

### 7.2.8. REG7 (0xF900\_001C)

| Bit | Reset 時 | 名前       | R/W | 機能                           |

|-----|---------|----------|-----|------------------------------|

| 23  |         | TP1      | W/R | 予備端子                         |

| 22  |         |          | RO  | 未使用                          |

| 21  |         | RO       |     | 未使用                          |

| 20  |         |          |     |                              |

| 19  |         |          |     |                              |

| 18  |         |          |     |                              |

| 17  |         |          |     |                              |

| 16  |         |          |     |                              |

| 15  |         |          |     |                              |

| 14  |         |          |     |                              |

| 13  | 0       | CAN1EN   | W/R | 出力ポート                        |

| 12  | 0       | CAN0EN   | W/R |                              |

| 11  | 1       | nCAN1STB | W/R |                              |

| 10  | 1       | nCAN0STB | W/R |                              |

| 9   | 0       | RTS3F    | W/R |                              |

| 8   | 0       | RTS1F    | W/R |                              |

| 7   | 0       | LED(7)   | W/R |                              |

| 6   | 0       | LED(6)   | W/R |                              |

| 5   | 0       | LED(5)   | W/R | 出力ポート(LED表示)<br>ロジック0で点灯します。 |

| 4   | 0       | LED(4)   | W/R |                              |

| 3   | 0       | LED(3)   | W/R |                              |

| 2   | 0       | LED(2)   | W/R |                              |

| 1   | 0       | LED(1)   | W/R |                              |

| 0   | 0       | LED(0)   | W/R |                              |

### 7.3. SW4 読み出しポート (0xF900\_0018)

汎用で使用可能な 8bit のスイッチがあり、ソフトウェアでリードすることができます。

PLD 内レジスタ【 7.2.7 】を参照してください。又 SW について【 4.6 】を参照してください。

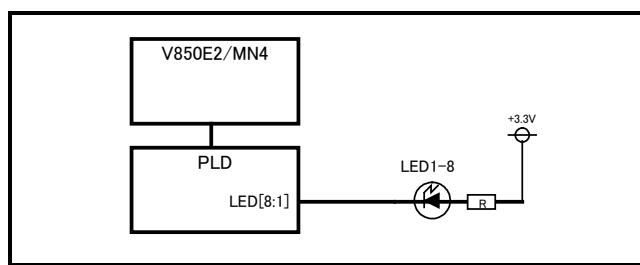

### 7.4. LED 表示出力ポート (0xF900\_001C)

ソフトウェアで制御できる LED を合計で8個実装しており、PLD のポートにより制御されます。

該当するビット位置に0をライトすると対応する LED が点灯します。

ビット位置は PLD 内レジスタ【 7.2.8 】を参照してください。

### 7.5. LAN-PHY

Ethernet I/F です。V850E2/MN4 とは PHY(LAN8700iC)を介して I/F します。RJ45 はトランスフォーマが内蔵されたタイプです。

また、V850E2/MN4 と PHY(LAN8700iC)はバススイッチ IC を経由して接続されているため、JP14 をショートすることにより基板上の PHY(LAN8700iC)が切り離され、CN15 へ独自の PHY/RJ45 搭載ボードを接続することができます。

## 7.6. USB2.0-HOST

V850E2/MN4 内蔵の USB ホスト・インターフェースを使用します。

USBバスパワーの制御が可能となっており、パワー供給中 LEDが点灯します。

## 7.7. USB2.0-FUNCTION

V850E2/MN4 内蔵の USB ファンクション・インターフェースを使用します。

## 7.8. SD インターフェース

V850E2/MN4 内蔵の CSI インターフェースを使用します。

## 7.9. UART

V850E2/MN4 内蔵 UART インターフェースを使用します。

### 7.10. CAN

V850E2/MN4 内蔵 CAN インターフェースを使用します。

### 7.11. LCDC

LCDC としてエプソン社製 S1D13706F00 をセカンダリバスへ直結しています。バックライト用インバータ基板への電源供給と輝度調整用のI/Fも備えています。

以下にレジスタ及び内部メモリのアドレスを示します。

| アドレス        | R/W | レジスタ名                                            |

|-------------|-----|--------------------------------------------------|

| 0xF940_0000 | R   | REG[00h] Revision Code Register                  |

| 0xF940_0001 | R   | REG[01h] Display Buffer Size Register            |

| 0xF940_0002 | R   | REG[02h] Configuration Readback Register         |

| 0xF940_0004 | R/W | REG[04h] Memory Clock Configuration Register     |

| 0xF940_0005 | R/W | REG[05h] Pixel Clock Configuration Register      |

| 0xF940_0008 | W   | REG[08h] Look-Up Table Blue Write Data Register  |

| 0xF940_0009 | W   | REG[09h] Look-Up Table Green Write Data Register |

| 0xF940_000A | W   | REG[0Ah] Look-Up Table Red Write Data Register   |

| 0xF940_000B | W   | REG[0Bh] Look-Up Table Write Address Register    |

| 0xF940_000C | R   | REG[0Ch] Look-Up Table Blue Read Data Register   |

| 0xF940_000D | R   | REG[0Dh] Look-Up Table Green Read Data Register  |

| 0xF940_000E | R   | REG[0Eh] Look-Up Table Red Read Data Register    |

|             |     |                                                              |

|-------------|-----|--------------------------------------------------------------|

| 0xF940_000F | W   | REG[0Fh] Look-Up Table Read Address Register                 |

| 0xF940_0010 | R/W | REG[10h] Panel Type Register                                 |

| 0xF940_0011 | R/W | REG[11h] MOD Rate Register                                   |

| 0xF940_0012 | R/W | REG[12h] Horizontal Total Register                           |

| 0xF940_0014 | R/W | REG[14h] Horizontal Display Period Register                  |

| 0xF940_0016 | R/W | REG[16h] Horizontal Display Period Start Position Register 0 |

| 0xF940_0017 | R/W | REG[17h] Horizontal Display Period Start Position Register 1 |

| 0xF940_0018 | R/W | REG[18h] Vertical Total Register 0                           |

| 0xF940_0019 | R/W | REG[19h] Vertical Total Register 1                           |

| 0xF940_001C | R/W | REG[1Ch] Vertical Display Period Register 0                  |

| 0xF940_001D | R/W | REG[1Dh] Vertical Display Period Register 1                  |

| 0xF940_001E | R/W | REG[1Eh] Vertical Display Period Start Position Register 0   |

| 0xF940_001F | R/W | REG[1Fh] Vertical Display Period Start Position Register 1   |

| 0xF940_0020 | R/W | REG[20h] FPLINE Pulse Width Register                         |

| 0xF940_0022 | R/W | REG[22h] FPLINE Pulse Start Position Register 0              |

| 0xF940_0023 | R/W | REG[23h] FPLINE Pulse Start Position Register 1              |

| 0xF940_0024 | R/W | REG[24h] FPFRAME Pulse Width Register                        |

| 0xF940_0026 | R/W | REG[26h] FPFRAME Pulse Start Position Register 0             |

| 0xF940_0027 | R/W | REG[27h] FPFRAME Pulse Start Position Register 1             |

| 0xF940_0028 | R/W | REG[28h] D-TFD GCP Index Register                            |

| 0xF940_002C | R/W | REG[2Ch] D-TFD GCP Data Register                             |

| 0xF940_0070 | R/W | REG[70h] Display Mode Register                               |

| 0xF940_0071 | R/W | REG[71h] Special Effects Register                            |

| 0xF940_0074 | R/W | REG[74h] Main Window Display Start Address Register 0        |

| 0xF940_0075 | R/W | REG[75h] Main Window Display Start Address Register 1        |

| 0xF940_0076 | R/W | REG[76h] Main Window Display Start Address Register 2        |

| 0xF940_0078 | R/W | REG[78h] Main Window Line Address Offset Register 0          |

| 0xF940_0079 | R/W | REG[79h] Main Window Line Address Offset Register 1          |

| 0xF940_007C | R/W | REG[7Ch] PIP+ Window Display Start Address Register 0        |

| 0xF940_007D | R/W | REG[7Dh] PIP+ Window Display Start Address Register 1        |

| 0xF940_007E | R/W | REG[7Eh] PIP+ Window Display Start Address Register 2        |

| 0xF940_0080 | R/W | REG[80h] PIP+ Window Line Address Offset Register 0          |

| 0xF940_0081 | R/W | REG[81h] PIP+ Window Line Address Offset Register 1          |

| 0xF940_0084 | R/W | REG[84h] PIP+ Window X Start Position Register 0             |

| 0xF940_0085 | R/W | REG[85h] PIP+ Window X Start Position Register 1             |

|             |     |                                                            |

|-------------|-----|------------------------------------------------------------|

| 0xF940_0088 | R/W | REG[88h] PIP+ Window Y Start Position Register 0           |

| 0xF940_0089 | R/W | REG[89h] PIP+ Window Y Start Position Register 1           |

| 0xF940_008C | R/W | REG[8Ch] PIP+ Window X End Position Register 0             |

| 0xF940_008D | R/W | REG[8Dh] PIP+ Window X End Position Register 1             |

| 0xF940_0090 | R/W | REG[90h] PIP+ Window Y End Position Register 0             |

| 0xF940_0091 | R/W | REG[91h] PIP+ Window Y End Position Register 1             |

| 0xF940_00A0 | R/W | REG[A0h] Power Save Configuration Register                 |

| 0xF940_00A1 | R/W | REG[A1h] Reserved                                          |

| 0xF940_00A2 | R/W | REG[A2h] Reserved                                          |

| 0xF940_00A3 | R/W | REG[A3h] Reserved                                          |

| 0xF940_00A4 | R/W | REG[A4h] Scratch Pad Register 0                            |

| 0xF940_00A5 | R/W | REG[A5h] Scratch Pad Register 1                            |

| 0xF940_00A8 | R/W | REG[A8h] General Purpose IO Pins Configuration Register 0  |

| 0xF940_00A9 | R/W | REG[A9h] General Purpose IO Pins Configuration Register 1  |

| 0xF940_00AC | R/W | REG[ACh] General Purpose IO Pins Status/Control Register 0 |

| 0xF940_00AD | R/W | REG[ADh] General Purpose IO Pins Status/Control Register 1 |

| 0xF940_00B0 | R/W | REG[B0h] PWM Clock / CV Pulse Control Register             |

| 0xF940_00B1 | R/W | REG[B1h] PWM Clock / CV Pulse Configuration Register       |

| 0xF940_00B2 | R/W | REG[B2h] CV Pulse Burst Length Register                    |

| 0xF940_00B3 | R/W | REG[B3h] PWMOUT Duty Cycle Register                        |

| 0xF942_0000 | R/W | 80KByte ディスプレイバッファ                                         |

| 0xF943_FFFF |     |                                                            |