# ***RTE-V850E/MS1-PC***

**ユーザーズ・マニュアル (Rev. 1.10)**

***Midas lab***

## 改訂履歴

| 実施日         | Revision | 章          | 内容                                                           |

|-------------|----------|------------|--------------------------------------------------------------|

| 1997年09月12日 | 0.00     |            | 暫定版                                                          |

| 1997年10月15日 | 0.80     |            | 初版                                                           |

| 1997年11月5日  | 0.81     | 3.5.4      | ・搭載可能 SIMM について追記                                            |

| 1998年01月10日 | 1.00     |            | ・33MHz 40MHz、SIMM 実装検査について追記<br>・40MHz 推奨値 / RWC レジスタ追加、内容修正 |

| 1998年01月16日 | 1.01     | 7.2<br>7.3 | ・表の 32/16BIT-の説明を修正<br>・注意事項 1 の内容修正<br>・注意事項 4 追加<br>・章追加   |

| 1998年07月11日 | 1.10     | 15         | PARTNER 用モニタ使用時の説明を追加                                        |

## 目次

|                                  |    |

|----------------------------------|----|

| <b>1. はじめに</b>                   | 1  |

| 1.1. マニュアル表記について                 | 1  |

| <b>2. 特徴と機能</b>                  | 2  |

| <b>3. ボードの構成</b>                 | 3  |

| 3.1. ディップ・スイッチ                   | 3  |

| 3.1.1. ディップ・スイッチ1 (SW1)          | 3  |

| 3.1.2. ディップ・スイッチ2 (SW2)          | 4  |

| 3.1.3. ディップ・スイッチ3 (SW3)          | 4  |

| 3.1.4. ディップ・スイッチ4 (SW4)          | 4  |

| 3.1.5. ディップ・スイッチ5 (SW5)          | 5  |

| 3.1.6. ディップ・スイッチ6 (SW6)          | 5  |

| 3.1.7. ディップ・スイッチ7 (SW7)          | 5  |

| 3.2. ジャンパ・スイッチ                   | 5  |

| 3.2.1. JP2                       | 5  |

| 3.2.2. AVDD 切り替えジャンパ (JP3)       | 6  |

| 3.2.3. ROM 容量切り替えジャンパ (JP5)      | 6  |

| 3.2.4. TIC 供給クロック切り替えジャンパ (JP6)  | 6  |

| 3.3. スイッチ                        | 6  |

| 3.3.1. リセット・スイッチ (SW_RESET)      | 6  |

| 3.4. LED                         | 7  |

| 3.5. コネクタ、ソケット類                  | 7  |

| 3.5.1. 電源コネクタ (JPOWER)           | 7  |

| 3.5.2. クリスタル・ソケット (JP4)          | 7  |

| 3.5.3. オシレータ・ソケット (OSC1)         | 8  |

| 3.5.4. DRAM-SIMM ソケット            | 8  |

| 3.5.5. ROM ソケット                  | 8  |

| 3.5.6. セルフ書き込み電源供給用コネクタ (JVPP)   | 8  |

| 3.5.7. ROM エミュレータ用コネクタ (JROM_EM) | 9  |

| 3.5.8. シリアル・コネクタ (JSIO1,JSIO2)   | 9  |

| 3.5.9. パラレル・コネクタ (JPRT)          | 10 |

| 3.5.10. シリアル・コネクタ (JRS232C)      | 11 |

| 3.5.11. フラッシュ書き込みコネクタ (JFLASH)   | 12 |

| 3.5.12. プロセッサ・ピンコネクタ (JCPU)      | 13 |

| 3.6. 拡張バス・コネクタ (JEXT)            | 14 |

| <b>4. ホストPCとの接続</b>              | 15 |

| 4.1. ISA バス・スロットに組み込んで使用する場合の手順  | 15 |

| 4.2. ボード単体で使用する場合の手順             | 15 |

|                                                          |           |

|----------------------------------------------------------|-----------|

| <b>5. ハードウェア・リファレンス</b>                                  | <b>16</b> |

| 5.1. メモリ・マップ概要                                           | 16        |

| 5.2. メモリ・マップ詳細                                           | 17        |

| <b>6. SYSTEM-IO</b>                                      | <b>19</b> |

| 6.1. SYSTEM-IO 一覧                                        | 19        |

| 6.2. UART/PRINTER ( TL16PIR552 ) (3D8-0000H ~ 3D8-003EH) | 20        |

| 6.3. TIC ( uPD71054 ) (3F-F040H ~ 3F-F048H)              | 21        |

| 6.4. 7セグメント LED 表示データ出力ポート(3D8-0050H [WRITE ONLY])       | 22        |

| 6.5. DIPSW7 読み出しポート(3D8-0050H [READ ONLY])               | 22        |

| 6.6. STATUS 読み出しポート(3D8-0060H [READ ONLY])               | 22        |

| 6.7. コントロール・ポート(3D8-0080H [READ/WRITE])                  | 23        |

| 6.8. NMI/INTP130 セレクト・ポート(3D8-0090H[READ/WRITE])         | 24        |

| 6.9. NMI/INTP130 ステータス・ポート(3D8-00A0H [READ ONLY])        | 24        |

| 6.10. EXT-BUS CPU-CORE 用バンク・ポート(3D8-00B0H[READ/WRITE])   | 24        |

| 6.11. EXT-BUS DMA0 用バンク・ポート(3D8-00C0H[READ/WRITE])       | 25        |

| 6.12. EXT-BUS DMA1 用バンク・ポート(3D8-00D0H[READ/WRITE])       | 25        |

| <b>7. EXT-BUS パス仕様</b>                                   | <b>27</b> |

| 7.1. ピン配置                                                | 27        |

| 7.2. 信号                                                  | 28        |

| 7.3. データバスの接続                                            | 30        |

| 7.3.1. 16ビット・データバス CPU ( V850E/MS1 )                     | 30        |

| 7.3.2. 32ビット・データバス CPU ( 参考 )                            | 31        |

| 7.4. タイミング                                               | 32        |

| 7.5. 適合コネクタ                                              | 33        |

| 7.6. 注意事項                                                | 33        |

| <b>8. DMA</b>                                            | <b>34</b> |

| 8.1. DMA 転送可能空間                                          | 34        |

| 8.2. DMA チャンネル                                           | 34        |

| 8.3. DIPSW の設定                                           | 34        |

| 8.4. CPU の設定                                             | 34        |

| 8.5. バンクポート設定 ( 2 サイクル DMA )                             | 34        |

| 8.6. バンクポート設定 ( フライバイ DMA )                              | 35        |

| 8.7. モニタ使用時                                              | 35        |

| <b>9. CPU 端子接続</b>                                       | <b>36</b> |

| 9.1. 一覧                                                  | 36        |

| 9.2. RESET-                                              | 37        |

| 9.3. NMI                                                 | 38        |

| 9.4. INTP130/P34                                         | 39        |

| 9.5. MODE0 ~ MODE2,CKSEL                                 | 40        |

|            |                                           |           |

|------------|-------------------------------------------|-----------|

| 9.6.       | MODE3/VPP,P21 .....                       | 41        |

| 9.7.       | X1,X2.....                                | 41        |

| 9.8.       | P22 ~ P27 .....                           | 41        |

| 9.9.       | ANIO/P70 ~ ANI7/P77,AVDD,AVSS,AVREF ..... | 42        |

| 9.10.      | ポート ( タイプ 1 ) .....                       | 42        |

| 9.11.      | ポート ( タイプ 2 ) .....                       | 43        |

| 9.12.      | ポート ( タイプ 3 ) .....                       | 43        |

| <b>10.</b> | <b>CPU 内蔵フラッシュROM 書き込み .....</b>          | <b>45</b> |

| 10.1.      | スイッチの設定 .....                             | 45        |

| 10.2.      | 通信方式.....                                 | 45        |

| 10.3.      | 書き込み手順.....                               | 45        |

| 10.4.      | 注意事項.....                                 | 45        |

| <b>11.</b> | <b>バス・サイクル .....</b>                      | <b>46</b> |

| 11.1.      | タイムオーバ・レディー .....                         | 46        |

| 11.2.      | SIMM インターフェース .....                       | 47        |

| 11.2.1.    | 概要 .....                                  | 47        |

| 11.2.2.    | 信号の説明.....                                | 47        |

| 11.2.3.    | リード・サイクル.....                             | 47        |

| 11.2.4.    | ライト・サイクル.....                             | 48        |

| <b>12.</b> | <b>ソフトウェア .....</b>                       | <b>48</b> |

| 12.1.      | CPU 設定 .....                              | 48        |

| 12.2.      | CS 空間設定 .....                             | 48        |

| 12.2.1.    | CS0/CS7 空間 ( SRAM/ROM ) .....             | 49        |

| 12.2.2.    | CS2 空間 ( EDO-DRAM ) .....                 | 49        |

| 12.2.3.    | CS3 空間 ( SIMM ) .....                     | 49        |

| 12.2.4.    | CS6 空間ウェイト .....                          | 49        |

| 12.2.5.    | CS6 空間コマンド・リカバリ・タイム .....                 | 49        |

| 12.3.      | ライブラリ .....                               | 50        |

| 12.4.      | タイマの使用法 .....                             | 50        |

| <b>13.</b> | <b>マスカブル割り込みを使用したアプリケーションの開発 .....</b>    | <b>53</b> |

| 13.1.      | 割り込みベクタ .....                             | 53        |

| 13.2.      | 一般的な制限事項 / 注意事項 .....                     | 54        |

| 13.3.      | ブレーク・ポイント使用に関する制限事項 / 注意事項 .....          | 54        |

| <b>14.</b> | <b>APPENDIX.A MULTI モニタ .....</b>         | <b>55</b> |

| 14.1.      | ボードの設置 .....                              | 55        |

| 14.1.1.    | RTE for Win32 のインストール .....               | 55        |

| 14.1.2.    | ディップ・スイッチ 1 ( SW1 ) .....                 | 55        |

| 14.1.3.    | ディップ・スイッチ 2 ( SW2 ) .....                 | 55        |

| 14.1.4.    | ディップ・スイッチ 3 ( SW3 ) .....                 | 55        |

|          |                                |    |

|----------|--------------------------------|----|

| 14.1.5.  | デイップ・スイッチ4 (SW4) .....         | 55 |

| 14.1.6.  | デイップ・スイッチ5 (SW5) .....         | 55 |

| 14.1.7.  | デイップ・スイッチ6 (SW6) .....         | 55 |

| 14.1.8.  | デイップ・スイッチ7 (SW7) .....         | 55 |

| 14.1.9.  | JP2 .....                      | 56 |

| 14.1.10. | AVDD 切り替えジャンパ (JP3) .....      | 56 |

| 14.1.11. | ROM 容量切り替えジャンパ (JP5) .....     | 56 |

| 14.1.12. | TIC 供給クロック切り替えジャンパ (JP6) ..... | 56 |

| 14.1.13. | ボードの接続 .....                   | 56 |

| 14.2.    | MULTI モニタ .....                | 57 |

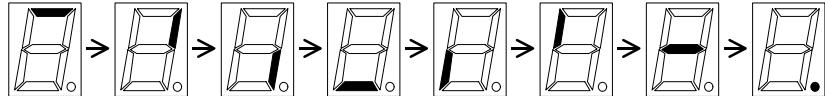

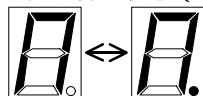

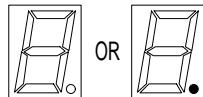

| 14.2.1.  | 起動時の 7Seg-LED .....            | 57 |

| 14.2.2.  | ROM モニタ・ワーク RAM .....          | 57 |

| 14.2.3.  | _INIT_SP の設定 .....             | 57 |

| 14.2.4.  | リモート接続 .....                   | 57 |

| 14.2.5.  | タイマ割り込み .....                  | 57 |

| 14.2.6.  | ハードウェアの初期化 .....               | 57 |

| 14.2.7.  | 特殊命令 .....                     | 57 |

| 14.3.    | RTE コマンド .....                 | 58 |

| 14.3.1.  | HELP(?) .....                  | 58 |

| 14.3.2.  | INIT .....                     | 58 |

| 14.3.3.  | VER .....                      | 58 |

| 14.3.4.  | SFR コマンド .....                 | 58 |

| 15.      | APPENDIX.B PARTNER モニタ .....   | 59 |

| 15.1.    | ボードの設置 .....                   | 59 |

| 15.1.1.  | デイップ・スイッチ1 (SW1) .....         | 59 |

| 15.1.2.  | デイップ・スイッチ2 (SW2) .....         | 59 |

| 15.1.3.  | デイップ・スイッチ3 (SW3) .....         | 59 |

| 15.1.4.  | デイップ・スイッチ4 (SW4) .....         | 59 |

| 15.1.5.  | デイップ・スイッチ5 (SW5) .....         | 59 |

| 15.1.6.  | デイップ・スイッチ6 (SW6) .....         | 59 |

| 15.1.7.  | デイップ・スイッチ7 (SW7) .....         | 60 |

| 15.1.8.  | JP2 .....                      | 60 |

| 15.1.9.  | AVDD 切り替えジャンパ (JP3) .....      | 60 |

| 15.1.10. | ROM 容量切り替えジャンパ (JP5) .....     | 60 |

| 15.1.11. | TIC 供給クロック切り替えジャンパ (JP6) ..... | 60 |

| 15.1.12. | ボードの接続 .....                   | 60 |

| 15.2.    | PARTNER モニタ .....              | 61 |

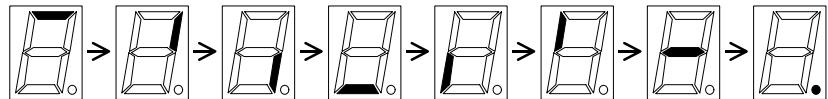

| 15.2.1.  | 起動時の 7Seg-LED .....            | 61 |

| 15.2.2.  | ROM モニタ・ワーク RAM .....          | 61 |

| 15.2.3.  | 強制ブレーキ用の割り込み .....             | 61 |

| 15.2.4.  | SP の設定 .....                   | 61 |

| 15.2.5.  | リモート接続 .....                   | 61 |

---

|         |                 |    |

|---------|-----------------|----|

| 15.2.6. | ハードウェアの初期化..... | 61 |

| 15.2.7. | 特殊命令 .....      | 61 |

## 1. はじめに

『RTE-V850E/MS1-PC』は、日本電気社製 CPU V850E/MS1 の評価を目的とした評価ボードで RS-232-C インターフェースと ISA バスのインターフェースを持っています。

評価プログラムの開発 / デバッグや CPU のパフォーマンス評価などを RS-232-C または ISA スロットに実装してご使用いただけます。

本製品は、開発用のソフトウェアツールとして GHS 社の Multi と自社製の PARTNER のどちらかをソースレベルデバッガとしてご使用になります。ご使用になるデバッガによって、ROM に搭載するモニタが異なります。

ROM は、購入時にご指定されたモニタが搭載されています。デバッガを同時に購入されていない場合は、それぞれ別売りされていますので、別途お買い求めください。

### 1.1. マニュアル表記について

本書では、数字の表記については表の表記を用います。16 進数や 2 進数の表記では、桁数が多くて読みにくい場合は、4 桁ごとに“-”（ハイフン）を入れてあります。

| 進数    | 表記規則           | 例                      |

|-------|----------------|------------------------|

| 10 進数 | 数字のみを示します      | “10”は 10 進数の“10”を示します  |

| 16 進数 | 数字の末尾に”H”を記します | “10H”は 10 進数の“16”を示します |

| 2 進数  | 数字の末尾に”B”を記します | “10B”は 10 進数の“2”を示します  |

数字表記規則

## 2. 特徴と機能

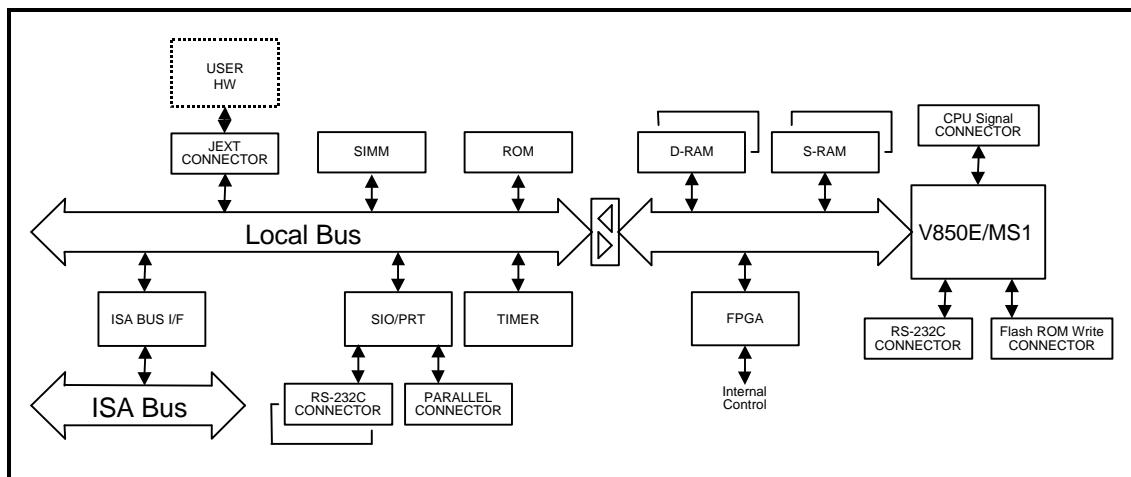

RTE-V850E/MS1-PC の機能ブロックの概要を以下の図に示します。

RTE-V850E/MS1-PC ブロック図

### 特徴

- ◊ ROM 標準 128K バイト (64K × 16 ビット EPROM × 1)

最大 512K バイト (256K × 16 ビット EPROM × 1)

- ◊ SRAM 512K バイト (64K × 16 ビット SRAM × 4)

- ◊ DRAM 4M バイト (2M × 8 ビット EDO-DRAM × 2)

- ◊ SIMM SIMM72 ピン・ソケット × 1 枚により 4M,8M (SIMM はオプション)

通常タイプの DRAM-SIMM に加え、EDO タイプの DRAM-SIMM も使用可能

- ◊ RS-232C ポート (D-SUB 9 ピン × 1、2.54mm ピンヘッダ 10 ピン × 2)

- ◊ パラレルポート (2.54mm ピンヘッダ 26 ピン × 1)

- ◊ PC/AT 互換機の ISA バスによる通信機能

- ◊ ユーザー拡張用のローカル・バスのコネクタ

- ◊ CPU の信号を計測できるプロセッサ・ピンコネクタ

- ◊ 外部リセット・スイッチをリアパネルに用意

- ◊ ROM インサーキット・デバッガ用の接続ピン

- ◊ CPU 内蔵フラッシュ ROM 書き込み用コネクタ

- ◊ CPU 内蔵の UART 機能を使用した RS232C コネクタ

### 3. ボードの構成

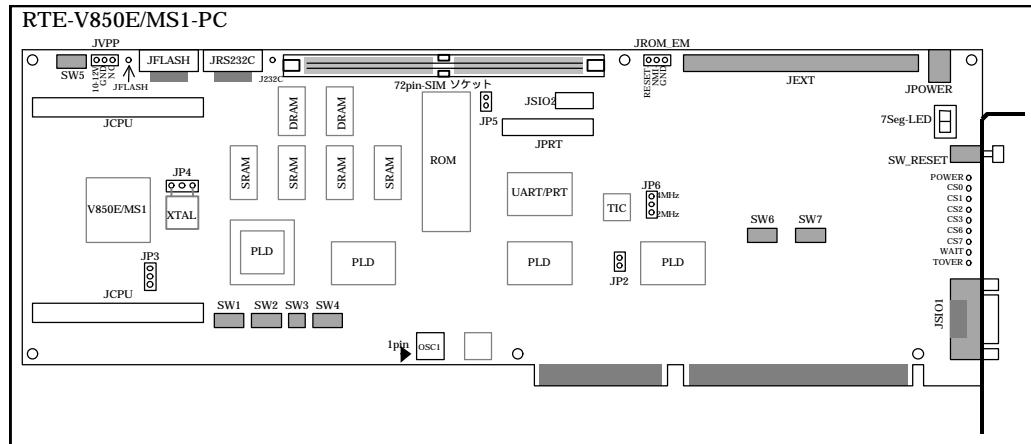

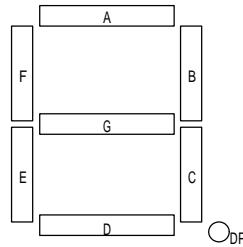

RTE-V850E/MS1-PC ボード上の主要な部品の物理的配置を以下の図に示します。

RTE-V850E/MS1-PC 概観

#### 3.1. ディップ・スイッチ

RTE-V850E/MS1-PC は、SW1～SW7 の 7 つのディップ・スイッチがあります。それぞれのディップスイッチの機能と出荷時の設定を以下で説明します。

##### 3.1.1. ディップ・スイッチ1 (SW1)

DIPSW1 は EXT-BUS の DMA 関係の設定を行います。

| No. | 記号                   | Def. | 機能                                                                                                                                                                        |

|-----|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | EXDMA0 <sup>*1</sup> | OFF  | OFF:CPU の INTP100/DMARQ0-/P04 端子と、INTP110/DMAAK0-/P14 端子が EXT-BUS の DMA 以外の用途で使用できます。<br>ON :CPU の INTP100/DMARQ0-/P04 端子と、INTP110/DMAAK0-/P14 端子が EXT-BUS の DMA で使用されます。 |

| 2   | EXDMA0 <sup>*1</sup> | OFF  | OFF:CPU の INTP101/DMARQ1-/P05 端子と、INTP111/DMAAK1-/P15 端子が EXT-BUS の DMA 以外の用途で使用できます。<br>ON :CPU の INTP101/DMARQ1-/P05 端子と、INTP111/DMAAK1-/P15 端子が EXT-BUS の DMA で使用されます。 |

| 3   | EXDMA1 <sup>*2</sup> | OFF  |                                                                                                                                                                           |

| 4   | EXDMA1 <sup>*2</sup> | OFF  | OFF:CPU の CS5-/RAS5-/IORD-/P85 端子が EXT-BUS の DMA 以外の用途で使用できます。<br>ON :CPU の CS5-/RAS5-/IORD-/P85 端子が EXT-BUS の DMA で IORD-として使用されます。                                      |

| 5   | PDMA                 | OFF  |                                                                                                                                                                           |

| 6   | PDMA                 | OFF  | システムで予約されています。OFF で用いてください。                                                                                                                                               |

| 7   | IORD- <sup>*3</sup>  | OFF  |                                                                                                                                                                           |

| 8   | IOWR- <sup>*3</sup>  | OFF  | OFF : CPU の CS4-/RAS4-/IOWR-/P84 端子が EXT-BUS の DMA 以外の用途で使用できます。<br>ON : CPU の CS4-/RAS4-/IOWR-/P84 端子が EXT-BUS の DMA で IOWR-として使用されます。                                   |

\*1 : EXT-BUS で DMA0 を使用する場合は、1 番と 2 番を ON にしてください。

\*2 : EXT-BUS で DMA1 を使用する場合は、3 番と 4 番を ON にしてください。

\*3 : EXT-BUS で DMA を使用する場合は、7 番と 8 番を ON にしてください。

### 3.1.2. ディップ・スイッチ2 (SW2)

DIPSW2 は割り込み関係の設定を行います。

| No. | 記号      | Def. | 機能                                                                                                                                                         |

|-----|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | NMI     | ON   | OFF : CPU の NMI/P20 端子が NMI 生成回路からの NMI 以外の用途で使用できます。<br>ON : CPU の NMI/P20 端子に NMI 生成回路からの NMI が接続されます。                                                   |

| 2   | INTP130 | OFF  | OFF : CPU の INTP130/P34 端子が INTP130 生成回路からの INTP130 以外の用途で使用できます。<br>ON : CPU の INTP130/P34 端子に INTP130 生成回路からの INTP130 が接続されます。                           |

| 3   | I_UART0 | OFF  | OFF : CPU の INTP131/SO2/P35 端子が TL16PIR552 の UART0 割り込み以外の用途で使用できます。<br>ON : CPU の INTP131/SO2/P35 端子に TL16PIR552 の INTRPT0 端子 (UART0 割り込み) が接続されます。       |

| 4   | I_UART1 | OFF  | OFF : CPU の INTP132/SI2/P36 端子が TL16PIR552 の UART1 割り込み以外の用途で使用できます。<br>ON : CPU の INTP132/SI2/P36 端子に TL16PIR552 の INTRPT1 端子 (UART1 割り込み) が接続されます。       |

| 5   | I_PRT   | OFF  | OFF : CPU の INTP133/SCK2-/P37 端子が TL16PIR552 の PRINTER 割り込み以外の用途で使用できます。<br>ON : CPU の INTP133/SCK2-/P37 端子に TL16PIR552 の PINTR-端子 (PRINTER 割り込み) が接続されます。 |

| 6   | I_TMR1  | OFF  | OFF : CPU の INTP140/P114 端子が TIC(μPD71054)のタイマ1 割り込み以外の用途で使用できます。<br>ON : CPU の INTP140/P114 端子に TIC(μPD71054)の TOUT1 端子 (タイマ1 割り込み) が接続されます。              |

| 7   | I_ISA   | OFF  | システムで予約されています。OFFで用いてください。                                                                                                                                 |

| 8   | 未使用     | OFF  |                                                                                                                                                            |

### 3.1.3. ディップ・スイッチ3 (SW3)

DIPSW3 は EXT-BUS の割り込みの設定を行います。

| No. | 記号     | Def. | 機能                                                                                                               |

|-----|--------|------|------------------------------------------------------------------------------------------------------------------|

| 1   | EXINT0 | OFF  | OFF : CPU の INTP150/P124 端子が EXT-BUS からの割り込み以外の用途で使用できます。<br>ON : CPU の INTP150/P124 端子に EXT-BUS の INT0 が接続されます。 |

| 2   | EXINT1 | OFF  | OFF : CPU の INTP151/P125 端子が EXT-BUS からの割り込み以外の用途で使用できます。<br>ON : CPU の INTP151/P125 端子に EXT-BUS の INT1 が接続されます。 |

| 3   | EXINT2 | OFF  | OFF : CPU の INTP152/P126 端子が EXT-BUS からの割り込み以外の用途で使用できます。<br>ON : CPU の INTP152/P126 端子に EXT-BUS の INT2 が接続されます。 |

| 4   | EXINT3 | OFF  | OFF : CPU の INTP153/P127 端子が EXT-BUS からの割り込み以外の用途で使用できます。<br>ON : CPU の INTP153/P127 端子に EXT-BUS の INT3 が接続されます。 |

### 3.1.4. ディップ・スイッチ4 (SW4)

DIPSW4 は SIMM の種類およびタイムオーバー Ready の設定を行います。

| No. | 記号                    | Def. | 機能                                                                                                           |

|-----|-----------------------|------|--------------------------------------------------------------------------------------------------------------|

| 1   | FLS_WP                | OFF  | システムで予約されています。OFFで用いて下さい。                                                                                    |

| 2   | FLS_VPP               | OFF  | システムで予約されています。OFFで用いて下さい。                                                                                    |

| 3   | TOVEN <sup>*1</sup>   | ON   | OFF : 一定期間バスサイクルが終了しなくともタイムオーバー Ready は発生しません。<br>ON : 一定期間バスサイクルが終了しない場合、タイムオーバー Ready を発生させてバスサイクルを終了させます。 |

| 4   | SIMMEDO <sup>*2</sup> | OFF  | OFF : SIMM が EDO タイプではない時設定します。<br>ON : SIMM が EDO タイプの時設定します。                                               |

| 5   | NMI/130               | OFF  | システムで予約されています。OFFで用いて下さい。                                                                                    |

| 6   | 未使用                   | OFF  |                                                                                                              |

| 7   | 未使用                   | OFF  |                                                                                                              |

| 8   | 未使用                   | OFF  |                                                                                                              |

\*1 : タイムオーバー Ready については『11.1 タイムオーバー・レディー』を参照してください。

\*2 : このスイッチの設定によりハードウェア的な切り替えは行なわれていません。このスイッチの内容は、モニタが読み出して CPU 内の DRAM コントローラの初期化に使用しています。

### 3.1.5. ディップ・スイッチ5 (SW5)

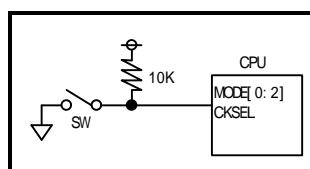

DIPSW5 は CPU の端子の状態を設定します。

| No. | 記号     | Def. | 機能                                                                                                                                                                                                                                                                                              |

|-----|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MODE0  | ON   | OFF : CPU の MODE0 端子を High にします。<br>ON : CPU の MODE0 端子を Low にします。                                                                                                                                                                                                                              |

| 2   | MODE1  | ON   | OFF : CPU の MODE1 端子を High にします。<br>ON : CPU の MODE1 端子を Low にします。                                                                                                                                                                                                                              |

| 3   | MODE2  | ON   | OFF : CPU の MODE2 端子を High にします。<br>ON : CPU の MODE2 端子を Low にします。                                                                                                                                                                                                                              |

| 4   | CKSEL  | ON   | OFF : CPU の CKSEL 端子を High にします (ダイレクト・モード)。<br>ON : CPU の CKSEL 端子を Low にします (PLL モード)。                                                                                                                                                                                                        |

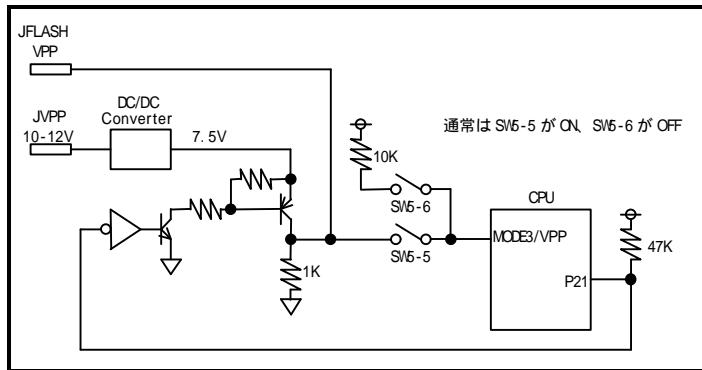

| 5   | M3_NML | ON   | システムで予約されています。ON で用いてください。                                                                                                                                                                                                                                                                      |

| 6   | M3_HI  | OFF  | システムで予約されています。OFF で用いてください。                                                                                                                                                                                                                                                                     |

| 7   | J232C  | OFF  | J232C と JFLASH の組み合わせで次のようにになります。<br>[J232C, JFLASH]<br>[ OFF, OFF ] CPU の P22 ~ P27 端子を下記以外の目的で使用できます。<br>[ ON, OFF ] CPU の P22 ~ P27 端子が JRS232C コネクタに接続され、JRS232C コネクタが有効になります (J232C-LED が点灯します)。<br>[ X, ON ] ライタを用いた CPU 内蔵フラッシュ ROM の書き込みモードになり、JFLASH コネクタが有効になります (JFLASH-LED が点灯します)。 |

| 8   | JFLASH | OFF  |                                                                                                                                                                                                                                                                                                 |

### 3.1.6. ディップ・スイッチ6 (SW6)

DIPSW6 は ISA バスの I/O アドレスを設定します。スイッチの番号 1 ~ 8 が ISA バスのアドレス A4 ~ A11 に対応しています (A12 ~ A15 は 0 に固定)。したがって、I/O アドレスとして 000xH ~ 0FFxH のいずれかに割り当てることができます。スイッチは、OFF で対応するアドレスが 1、ON で対応するアドレスが 0 になります。デフォルトの設定は、0200H 番地です。

| No. | 記号  | Def. | 機能                                    |

|-----|-----|------|---------------------------------------|

| 1   | A4  | ON   | ISA バスの I/O アドレスを設定します (OFF=1, ON=0)。 |

| 2   | A5  | ON   |                                       |

| 3   | A6  | ON   |                                       |

| 4   | A7  | ON   |                                       |

| 5   | A8  | ON   |                                       |

| 6   | A9  | OFF  |                                       |

| 7   | A10 | ON   |                                       |

| 8   | A11 | ON   |                                       |

### 3.1.7. ディップ・スイッチ7 (SW7)

CPU から汎用ポート経由で読み出すことのできるスイッチです。モニタを使用する場合は、一部のビットが予約されています。詳細はご使用するモニタに該当する付録の章を参照してください。

## 3.2. ジャンパ・スイッチ

RTE-V850E/MS1-PC は、JP2,JP3,JP5,JP6 の 4 つのジャンパ・スイッチがあります。以下にそれぞれのジャンパ・スイッチの機能を説明します。

### 3.2.1. JP2

JP2 はシステム予約です。オープン状態で用います。

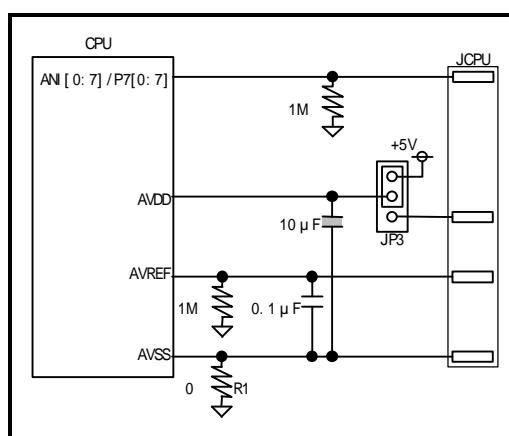

### 3.2.2. AVDD 切り替えジャンパ(JP3)

JP3 は、CPU の AVDD 端子に供給する電源を切り替えます (『9.9ANI0/P70 ~ ANI7/P77,AVDD,AVSS,AVREF』参照)。

| JP3 設定           | 内容                                                         |

|------------------|------------------------------------------------------------|

| 1pin - 2pin ショート | CPU の AVDD ピンに CPU の HVDD 端子と同じ電源(+5V)が接続されます。<br>(出荷時の設定) |

| 2pin - 3pin ショート | CPU の AVDD ピンに JCPU コネクタからの AVDD 信号が接続されます。                |

CPU の AVSS 端子は、JP3 の裏側にある R1 抵抗(0Ω)を経由して GND に接続されています。AVSS 端子を GND からアイソレートして、JCPU コネクタから AVSS を与える場合は、R1 抵抗を外してください。

### 3.2.3. ROM 容量切り替えジャンパ(JP5)

JP5 は実装する ROM の容量によって切り替えるジャンパです。

| JP5 設定           | 内容                                                                        |

|------------------|---------------------------------------------------------------------------|

| 1pin - 2pin オープン | 128K バイト (64K × 16 ピット) と 256K バイト (128K × 16 ピット) の ROM を実装する場合。(出荷時の設定) |

| 1pin - 2pin ショート | 512K バイト (256K × 16 ピット) の ROM を実装する場合。                                   |

### 3.2.4. TIC 供給クロック切り替えジャンパ(JP6)

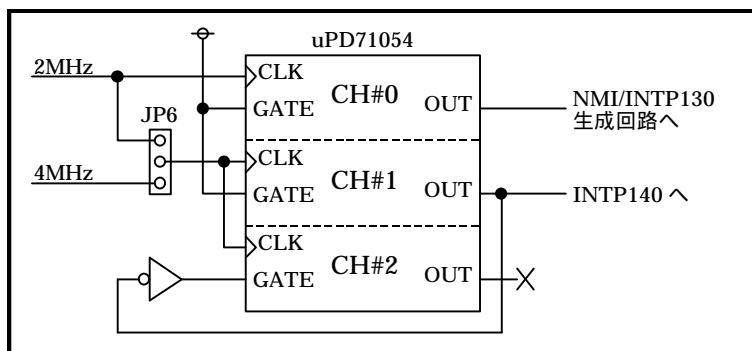

JP6 は TIC(μPD71054)のカウンタ#1 と#2 に供給するクロックを切り替えるジャンパです(『6.3TIC (uPD71054) (3F-F040H ~ 3F-F048H)』参照)。

| JP6 設定           | 内容                                          |

|------------------|---------------------------------------------|

| 1pin - 2pin ショート | TIC のカウンタ#1 と#2 のクロックに 2MHz を供給します。(出荷時の設定) |

| 2pin - 3pin ショート | TIC のカウンタ#1 と#2 のクロックに 4MHz を供給します。         |

## 3.3. スイッチ

RTE-V850E/MS1-PC は、スイッチとして SW\_RESET スイッチがあります。

### 3.3.1. リセット・スイッチ(SW\_RESET)

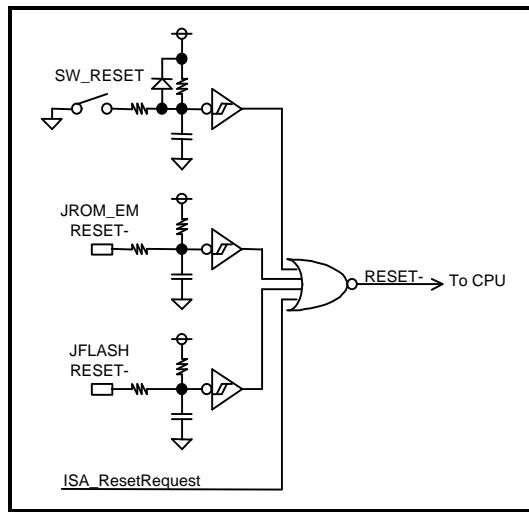

SW\_RESET はリセット・スイッチです。このスイッチを押すと CPU およびボード全体がリセットされます (『9.2RESET-』参照)。

### 3.4. LED

RTE-V850E/MS1-PC の各種 LED の機能を説明します。

| LED の名称  | 内容                                                                                   |

|----------|--------------------------------------------------------------------------------------|

| POWER    | ボードの電源が入っている時に点灯します。                                                                 |

| CS0      | CPU の CS0-端子が Low の時に点灯します。                                                          |

| CS1      | CPU の CS1-端子が Low の時に点灯します。                                                          |

| CS2      | CPU の CS2-端子が Low の時に点灯します。                                                          |

| CS3      | CPU の CS3-端子が Low の時に点灯します。                                                          |

| CS4      | CPU の CS4-端子が Low の時に点灯します。                                                          |

| CS5      | CPU の CS5-端子が Low の時に点灯します。                                                          |

| CS6      | CPU の CS6-端子が Low の時に点灯します。                                                          |

| CS7      | CPU の CS7-端子が Low の時に点灯します。                                                          |

| WAIT     | CPU の WAIT-端子が Low の時に点灯します。                                                         |

| TOVER    | タイムオーバー Ready が発生した時に点灯します。                                                          |

| JFLASH   | JFLASH コネクタが有効な時に点灯します。                                                              |

| J232C    | JRS232C コネクタが有効な時に点灯します。                                                             |

| 7Seg-LED | 汎用ポートに出力した内容により点灯させることができます (『6.47 セグメント LED 表示データ出力ポート(3D8-0050H [Write Only])』参照)。 |

### 3.5. コネクタ、ソケット類

RTE-V850E/MS1-PC の各種コネクタおよびソケットについて説明します。

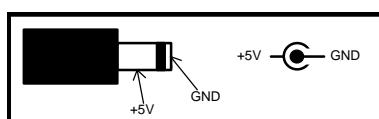

#### 3.5.1. 電源コネクタ (JPOWER)

本ボードを ISA バス・スロットに挿さずに単体で使用する場合には、JPOWER コネクタに外部電源を接続して電源を供給します。

JPOWER コネクタに供給する電源は、以下の通りです。

電圧 : 5 V

電流 : 最大 2 A (ただし、JEXT コネクタへの供給分を含まず)

適合コネクタ : Type A ( 5.5 )

極性 :

電源コネクタの極性に十分ご注意ください

また、ISA バス・スロットに挿して本ボードを使用する場合には、JPOWER に電源を接続しないでください。

#### 3.5.2. クリスタル・ソケット (JP4)

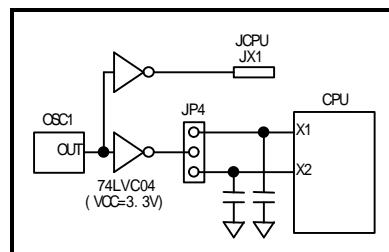

JP4 は、CPU に供給するクロックの切り替えの役割と、クリスタルの実装用ソケットの役割を持っています (『9.7X1,X2』参照)。

| JP4 設定                   | 内容                                          |

|--------------------------|---------------------------------------------|

| X1pin - X2pin 間にクリスタルを実装 | CPU の X1 端子と X2 端子に実装したクリスタルが接続されます。        |

| X1pin と JP4 の中央ピンをショート   | CPU の X1 端子に OSC1 ソケットに実装したオシレータの出力が接続されます。 |

### 3.5.3. オシレータ・ソケット( OSC1 )

OSC1 ソケットには、CPU に供給するクロック用のオシレータを実装します。

CPU への供給クロックは、JP4 によって、JP4 上に実装したクリスタルを使用することもできます (『9.7X1,X2』参照)

OSC1 ソケットには、DIP8 ピンタイプ ( ハーフタイプ ) の 5V 用オシレータを実装してください。

オシレータを実装する場合は、1 番ピンの位置に十分ご注意ください。オシレータの足が短すぎると、オシレータのフレーム(外装)部分がソケットの端子とショートしてしまうことがありますのでご注意願います。

### 3.5.4. DRAM-SIMM ソケット

DRAM-SIMM ソケットには 4M,8M バイトの 72 ピン SIMM ( PC/AT 互換機用として用いられるもので、ロウ・アドレス / カラム・アドレスのビット幅の等しい DRAM を搭載し、RAS-信号が独立した SIMM ) が実装できます。また、通常タイプの DRAM-SIMM に加え、EDO タイプの DRAM-SIMM を使用することができます。実装されている SIMM の容量は PIO ポートから読み出すことができます (『6.6Status 読み出しポート(3D8-0060H [Read Only])』参照 )

16M,32M バイトタイプの SIMM は使用できません。

### 3.5.5. ROM ソケット

ROM ソケットには、標準で 128K バイト ( 64K × 16 ピット ) の 40 ピン ROM が実装されています。ROM は、アクセス・タイムが 120ns 以下のものをご使用ください。異なる容量の ROM を実装する場合は、ボード上の JP5 の切り替えが必要な場合があります (『3.2.3ROM 容量切り替えジャンパ ( JP5 )』参照 )

### 3.5.6. セルフ書き込み電源供給用コネクタ( JVPP )

CPU 内蔵のフラッシュ ROM にセルフ書き込みを行う場合、7.5V の電源が必要になります。この 7.5V の電源を生成するための電源を供給するのが、JVPP コネクタです。

このコネクタに 10V ~ 12V の電源を供給し、CPU の P21 端子に Low を出力すると、CPU の VPP 端子に 7.5V が供給されます (『9.6MODE3/Vpp,P21』参照 )

JVPP のピン配置を以下に示します。

| JVPP ピン番号 | 名称     | 入出力 | 機能                   |

|-----------|--------|-----|----------------------|

| 1         | 10-12V | 入力  | 10V ~ 12V の電源を入力します。 |

| 2         | GND    | 入力  | 電源の GND に接続します。      |

| 3         | NC     |     | 未接続です。               |

### 3.5.7. ROM エミュレータ用コネクタ(JROM\_EM)

JROM\_EM は、ROM インサーキット型のデバッガを接続する際に使用するコネクタです。ROM インサーキット・デバッガからの制御信号が入力できます。

下表に信号名と機能を示します。

| JROM_EM ピン番号 | 名称     | 入出力   | 機能                                                                                                      |

|--------------|--------|-------|---------------------------------------------------------------------------------------------------------|

| 1            | RESET- | 入力    | ROM インサーキット・デバッガからのリセット要求信号を接続。Low レベル入力により、CPU がリセットされます。本ボード内で 1K ブルアップされています。（『9.2RESET-』参照）         |

| 2            | NMI-   | 入力    | ROM インサーキット・デバッガからの NMI 要求信号（ブレーク要求）を接続。Low レベル入力により、CPU に NMI が入ります。本ボード内で 1K ブルアップされています。（『9.3NMI』参照） |

| 3            | GND    | - - - | ROM インサーキット・デバッガの GND と接続。GND です。                                                                       |

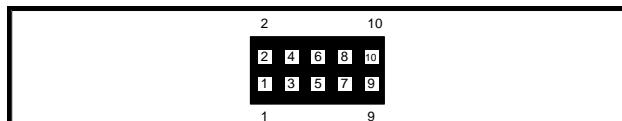

### 3.5.8. シリアル・コネクタ(JSIO1,JSIO2)

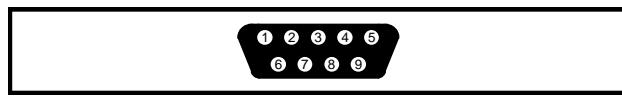

JSIO1,JSIO2 コネクタは、シリアル・コントローラ（TL16PIR552）によって制御される RS-232C 用のコネクタです。コネクタの形状は、JSIO1 は PC/AT 互換機で用いられる一般的な D-SUB9 ピンの RS-232C コネクタで、JSIO2 は 2.54mm ピッチのピンヘッダ型コネクタです。何れも、全ての信号は RS-232C レベルに変換されています。コネクタのピン番号と内容は図と表の通りです。

表には、ホストと接続する場合の接続信号について、ホスト側が D-SUB9 ピンの場合と D-SUB25 ピンの場合の布線をそれぞれ示してあります（一般的なクロスケーブルの布線です）。

また、JSIO2 のピン配置はリボンケーブルに対して圧接型コネクタを使用した場合、JSIO1 のピン配置と同じになるようになっています。

JSIO1 ピン配置

JSIO2 ピン配置

| JSIO1<br>ピン番号 | JSIO2<br>ピン番号 | 信号名     | 入出力 | ホストの接続ピン番号 |         |

|---------------|---------------|---------|-----|------------|---------|

|               |               |         |     | D-SUB9     | D-SUB25 |

| 1             | 1             | DCD     | 入力  |            |         |

| 2             | 3             | RxD(RD) | 入力  | 3          | 2       |

| 3             | 5             | TxD(SD) | 出力  | 2          | 3       |

| 4             | 7             | DTR(DR) | 出力  | 1, 6       | 6, 8    |

| 5             | 9             | GND     |     | 5          | 7       |

| 6             | 2             | DSR(ER) | 入力  | 4          | 20      |

| 7             | 4             | RTS(RS) | 出力  | 8          | 5       |

| 8             | 6             | CTS(CS) | 入力  | 7          | 4       |

| 9             | 8             | RI      | 入力  |            |         |

| --            | 10            | NC      |     |            |         |

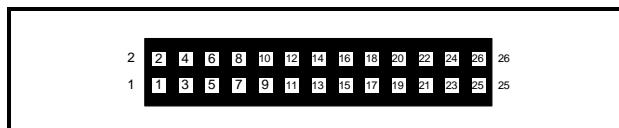

### 3.5.9. パラレル・コネクタ (JPRT)

JPRT コネクタは、パラレル (プリンタ)・コントローラ (TL16PIR552) によって制御されるパラレル用のコネクタです。コネクタの形状は、2.54mm ピッチのピンヘッダ型コネクタです。何れも、全ての信号は 5V レベルです。コネクタのピン番号と内容は図と表の通りです。

また、JPRT のピン配置はリボンケーブルに対して圧接型コネクタを使用した場合、PC/AT 互換機で用いられている一般的な D-SUB25 ピンのピン配置と同じになるようになっています。

JPRT ピン配置

| JPRT<br>ピン番号 | 信号名    | JPRT<br>ピン番号 | 信号名        |

|--------------|--------|--------------|------------|

| 1            | STB-   | 2            | AUTO_FD-   |

| 3            | D0     | 4            | ERROR-     |

| 5            | D1     | 6            | INIT-      |

| 7            | D2     | 8            | SELECT_IN- |

| 9            | D3     | 10           | GND        |

| 11           | D4     | 12           | GND        |

| 13           | D5     | 14           | GND        |

| 15           | D6     | 16           | GND        |

| 17           | D7     | 18           | GND        |

| 19           | ACK-   | 20           | GND        |

| 21           | BUSY   | 22           | GND        |

| 23           | PE     | 24           | GND        |

| 25           | SELECT | 26           | NC         |

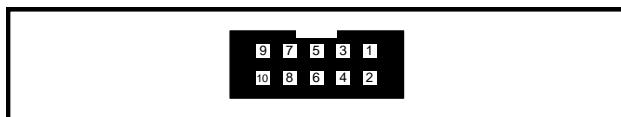

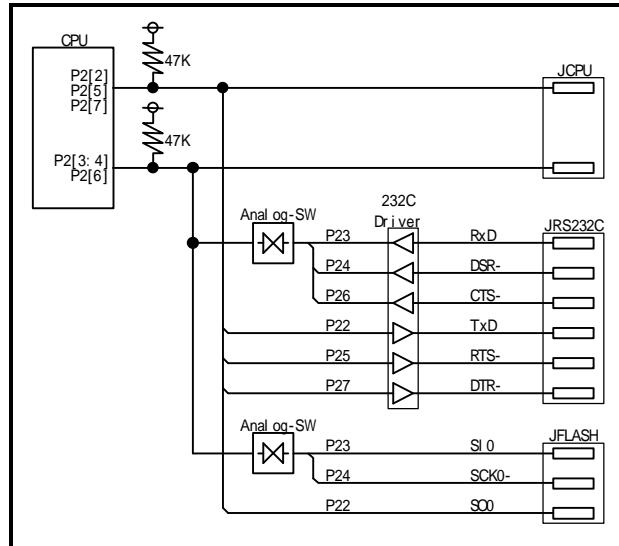

### 3.5.10. シリアル・コネクタ (JRS232C)

JRS232C コネクタは、CPU の内蔵 UART によって制御される RS-232C 用のコネクタです(『9.8P22 ~ P27』参照)。コネクタの形状は、2.54mm ピッチのピンヘッダですが、リボンケーブルに対して圧接型コネクタを使用した場合、ピン配置が PC/AT 互換機で用いられる一般的な D-SUB9 ピンの RS-232C コネクタと同じになっています。全ての信号は RS-232C レベルに変換されています。

JRS232C を使用する場合は、SW5 の設定が必要です(『3.1.5ディップ・スイッチ5 (SW5)』参照)。JRS232C が使用可能な場合は、J232C-LED が点灯します(『3.4LED』参照)。

JRS232C コネクタのピン配置を図と表に示します。また、パーソナル・コンピュータ (ホスト) などと接続する場合の布線は、『3.5.8シリアル・コネクタ (JSIO1,JSIO2)』の表を参照してください。

JRS232C ピン配置

| JRS232C<br>ピン番号 | 信号名     | 入出力 | 対応<br>CPU 端子 |

|-----------------|---------|-----|--------------|

| 1               | NC      | 入力  |              |

| 3               | RxD(RD) | 入力  | P23          |

| 5               | TxD(SD) | 出力  | P22          |

| 7               | DTR(DR) | 出力  | P27          |

| 9               | GND     |     |              |

| 2               | DSR(ER) | 入力  | P24          |

| 4               | RTS(RS) | 出力  | P25          |

| 6               | CTS(CS) | 入力  | P26          |

| 8               | NC      |     |              |

| 10              | NC      |     |              |

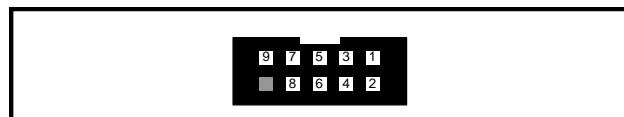

### 3.5.11. フラッシュ書き込みコネクタ (JFLASH)

JFLASH コネクタは、CPU の内蔵のフラッシュ ROM ヘライタを使用して書き込む時に、ライタを接続するためのコネクタです。このコネクタには弊社のフラッシュライタFP-100 が直接接続できます。

JFLASH を使用する場合は、SW5 の設定が必要です (『3.1.5 ディップ・スイッチ 5 (SW5)』参照)。JFLASH が使用可能な場合は、JFLASH-LED が点灯します (『3.4 LED』参照)。

フラッシュ ROM の書き込みの詳細については『10CPU 内蔵フラッシュ ROM 書き込み』を参照してください。

JFLASH ピン配置

| JFLASH<br>ピン番号 | 信号名    | 入出力 | 備考                      |

|----------------|--------|-----|-------------------------|

| 1              | SO0    | 出力  | 同期シリアルデータ出力 (CMOS レベル)  |

| 2              | SI0    | 入力  | 同期シリアルデータ入力 (CMOS レベル)  |

| 3              | SCK0-  | 入力  | 同期シリアルクロック入力 (CMOS レベル) |

| 4              | RESET- | 入力  | リセット入力                  |

| 5              | VPP    | 入力  | VPP 入力                  |

| 6              | +3.3V  | 出力  | CPU コア電源レベル出力           |

| 7              | +5V    | 出力  | CPU-I/O 電源レベル出力         |

| 8              | GND    | -   | グランド                    |

| 9              | NC     | -   | 未接続                     |

| (10)           | NC     | -   | 未接続 (ピン無し)              |

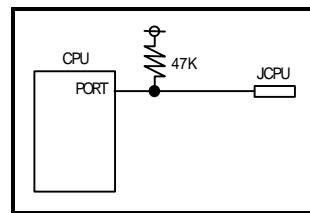

### 3.5.12. プロセッサ・ピンコネクタ (JCPU)

CPU の端子が接続されているコネクタです。ボード内の接続については『9CPU 端子接続』を参照してください。

| JCPU<br>ピン番号 | 信号名                      | JCPU<br>ピン番号 | 信号名                  |

|--------------|--------------------------|--------------|----------------------|

| 1            | GND                      | 2            | INTP142/SI3/P116     |

| 3            | INTP141/SO3/P115         | 4            | INTP140/P114         |

| 5            | TI14/P113                | 6            | TCLR14/P112          |

| 7            | TO141/P111               | 8            | TO140/P110           |

| 9            | +3.3V                    | 10           | 未接続                  |

| 11           | +3.3V                    | 12           | JX1 <sup>*1</sup>    |

| 13           | GND                      | 14           | CKSEL                |

| 15           | MODE0                    | 16           | MODE1                |

| 17           | MODE2                    | 18           | MODE3/VPP            |

| 19           | RESET-                   | 20           | INTP153/ADTRG/P127   |

| 21           | +5V                      | 22           | INTP152/P126         |

| 23           | INTP151/P125             | 24           | INTP150/P124         |

| 25           | TI15/P123                | 26           | TCLR15/P122          |

| 27           | TO151/P121               | 28           | TO150/P120           |

| 29           | CLKOUT/PX7               | 30           | WAIT-/PX6            |

| 31           | GND                      | 32           | REFRQ-/PX5           |

| 33           | JCPU_WAIT- <sup>*2</sup> | 34           | HLDRQ-/P97           |

| 35           | HLDAK-/P96               | 36           | OE-/P95              |

| 37           | ADV-/BCYST-/P94          | 38           | WE-/P93              |

| 39           | RD-/P92                  | 40           | UCAS-/UWR-/P91       |

| 41           | +3.3V                    | 42           | LCAS-/LWR-/P90       |

| 43           | CS7-/RAS7-/P87           | 44           | CS6-/RAS6-/P86       |

| 45           | CS5-/RAS5-/IORD-/P85     | 46           | CS4-/RAS4-/IOWR-/P84 |

| 47           | CS3-/RAS3-/P83           | 48           | CS2-/RAS2-/P82       |

| 49           | CS1-/RAS1-/P81           | 50           | CS0-/RAS0-/P80       |

| 51           | +5V                      | 52           | +5V                  |

| 53           | A23/P67                  | 54           | A22/P66              |

| 55           | A21/P65                  | 56           | A20/P64              |

| 57           | A19/P63                  | 58           | A18/P62              |

| 59           | A17/P61                  | 60           | A16/P60              |

| 61           | GND                      | 62           | A15/PB7              |

| 63           | A14/PB6                  | 64           | A13/PB5              |

| 65           | A12/PB4                  | 66           | A11/PB3              |

| 67           | A10/PB2                  | 68           | A9/PB1               |

| 69           | A8/PB0                   | 70           | GND                  |

| 71           | +3.3V                    | 72           | A7/PA7               |

| 73           | A6/PA6                   | 74           | A5/PA5               |

| 75           | A4/PA4                   | 76           | A3/PA3               |

| 77           | A2/PA2                   | 78           | A1/PA1               |

| 79           | A0/PA0                   | 80           | +5V                  |

\*1 : OSC1 ソケットに実装されているオシレータの出力が 3.3V レベルに変換されて出力されています (『9.7X1,X2』参照)。

\*2 : JCPU コネクタからの WAIT-の入力です。JCPU コネクタ経由でバスサイクルにウェイトを挿入する時に使用します。

| JCPU<br>ピン番号 | 信号名                 | JCPU<br>ピン番号 | 信号名                 |

|--------------|---------------------|--------------|---------------------|

| 81           | GND                 | 82           | D15/P57             |

| 83           | D14/P56             | 84           | D13/P55             |

| 85           | D12/P54             | 86           | D11/P53             |

| 87           | D10/P52             | 88           | D9/P51              |

| 89           | D8/P50              | 90           | GND                 |

| 91           | +3.3V               | 92           | D7/P47              |

| 93           | D6/P46              | 94           | D5/P45              |

| 95           | D4/P44              | 96           | D3/P43              |

| 97           | D2/P42              | 98           | D1/P41              |

| 99           | D0/P40              | 100          | +3.3V               |

| 101          | +5V                 | 102          | INTP103/DMARQ3-/P07 |

| 103          | INTP102/DMARQ2-/P06 | 104          | INTP101/DMARQ1-/P05 |

| 105          | INTP100/DMARQ0-/P04 | 106          | TI10/P03            |

| 107          | TCLR10/P02          | 108          | TO101/P01           |

| 109          | TO100/P00           | 110          | GND                 |

| 111          | GND                 | 112          | INTP113/DMAAK3-/P17 |

| 113          | INTP112/DMAAK2-/P16 | 114          | INTP111/DMAAK1-/P15 |

| 115          | INTP110/DMAAK0-/P14 | 116          | TI11/P13            |

| 117          | TCLR11/P12          | 118          | TO111/P11           |

| 119          | TO110/P10           | 120          | INTP123/TC3-/P107   |

| 121          | +3.3V               | 122          | INTP122/TC2-/P106   |

| 123          | INTP121/TC1-/P105   | 124          | INTP120/TC0-/P104   |

| 125          | TI12/P103           | 126          | TCLR12/P102         |

| 127          | TO121/P101          | 128          | TO120/P100          |

| 129          | ANI7/P77            | 130          | ANI6/P76            |

| 131          | +5V                 | 132          | ANI5/P75            |

| 133          | ANI4/P74            | 134          | ANI3/P73            |

| 135          | ANI2/P72            | 136          | ANI1/P71            |

| 137          | ANI0/P70            | 138          | AVDD <sup>*3</sup>  |

| 139          | AVSS <sup>*3</sup>  | 140          | AVREF               |

| 141          | GND                 | 142          | NMI/P20             |

| 143          | P21                 | 144          | TXD0/S00/P22        |

| 145          | RXD0/S10/P23        | 146          | SCK0-/P24           |

| 147          | TXD1/S01/P25        | 148          | RXD1/S11/P126       |

| 149          | SCK1-/P27           | 150          | +3.3V               |

| 151          | +3.3V               | 152          | INTP133/SCK2-/P37   |

| 153          | INTP132/SI2/P36     | 154          | INTP131/SO2/P35     |

| 155          | INTP130/P34         | 156          | TI13/P33            |

| 157          | TCLR13/P32          | 158          | TO131/P31           |

| 159          | TO130/P30           | 160          | INTP143/SCK3-/P117  |

\*3 : AVDD,AVSS と CPU の接続については、『9.9ANI0/P70 ~ ANI7/P77,AVDD,AVSS,AVREF』を参照して下さい。

### 3.6. 拡張バス・コネクタ (JEXT)

JEXT コネクタは、メモリや I/O などを拡張できるように用意されたコネクタです。このコネクタには、本ボードの内部のローカル・バスが接続されています。このコネクタの詳細については『7EXT-BUS バス仕様』を参照してください。

#### 4. ホストPCとの接続

##### 4.1. ISAバス・スロットに組み込んで使用する場合の手順

ボードをPCのISAバス・スロットに組み込むと、ISAバスからボードへ電源(+5V)が供給されます。また、デバッガとの通信にISAバス経由が使用できるため、プログラムの高速なダウンロードが実現できます。

ISAバス・スロットへの組み込み手順は、以下ようになります。

ボード上のディップ・スイッチにより、RTE-V850E/MS1-PCが使用するPCのI/Oアドレスを設定します。I/Oアドレスは他のI/Oと重ならないように注意してください。スイッチの設定については『3.1.6ディップ・スイッチ6(SW6)』を参照ください。

PCの電源を切って筐体をあけ、ボードを実装するISAバス・スロットを確認します。実装するスロットにリアパネルが付いている場合は、そのリアパネルを外します。

ボードをISAバス・スロットに差し込み、ボードが隣接の他のボードなどと接触していないかを確認し、ボードに付いているリアパネルをPCの筐体にネジで固定します。

PCの電源を入れ、ボードのPOWER-LEDが点灯することを確認します。**LEDが点灯しない場合は、すぐにPCの電源を切り接続を確認してください。**

ホストマシンでデバッガを起動して、ISAバス経由でコネクトします。エラーが発生する場合には、ボードの実装やソフトウェアのインストールに間違いがないかを確認してください。

##### 4.2. ボード単体で使用する場合の手順

PCに組み込みず、ボード単体で使用する場合は、外部からの電源供給が必要となります。また、デバッガとの通信もRS-232C経由のみとなります。

ボードを単体で使用する場合の手順は以下の通りです。

ホストと接続するためのシリアルケーブルと、電源供給のための外部電源(+5V 2A)を用意してください。特に電源については、電圧と**コネクタの極性**に注意してください。また、ボードの4隅にスペーサを取り付けるなど、設置場所にも問題がないようにしてください。RS-232Cケーブルの結線は『3.5.8シリアル・コネクタ(JSIO1,JSIO2)』、電源コネクタについては、『3.5.1電源コネクタ(JPOWER)』を参照してください。

ボード上のディップ・スイッチで、RS-232Cのボーレートを設定します。スイッチの設定については各モニタの章を参照してください。

ホストとRS-232Cケーブルで接続して、JPOWERコネクタに電源を接続し、ボードのPOWER-LEDが点灯することを確認します。**LEDが点灯しない場合は、すぐに電源を切り接続を確認してください。**

ホストマシンでデバッガを起動して、RS-232C経由でコネクトします。エラーが発生する場合には、シリアルケーブルやスイッチ(特にボーレート)の設定に間違いがないかを確認してください。

## 5. ハードウェア・リファレンス

ここでは、RTE-V850E/MS1-PC ボードのハードウェアについて記述します。

### 5.1. メモリ・マップ概要

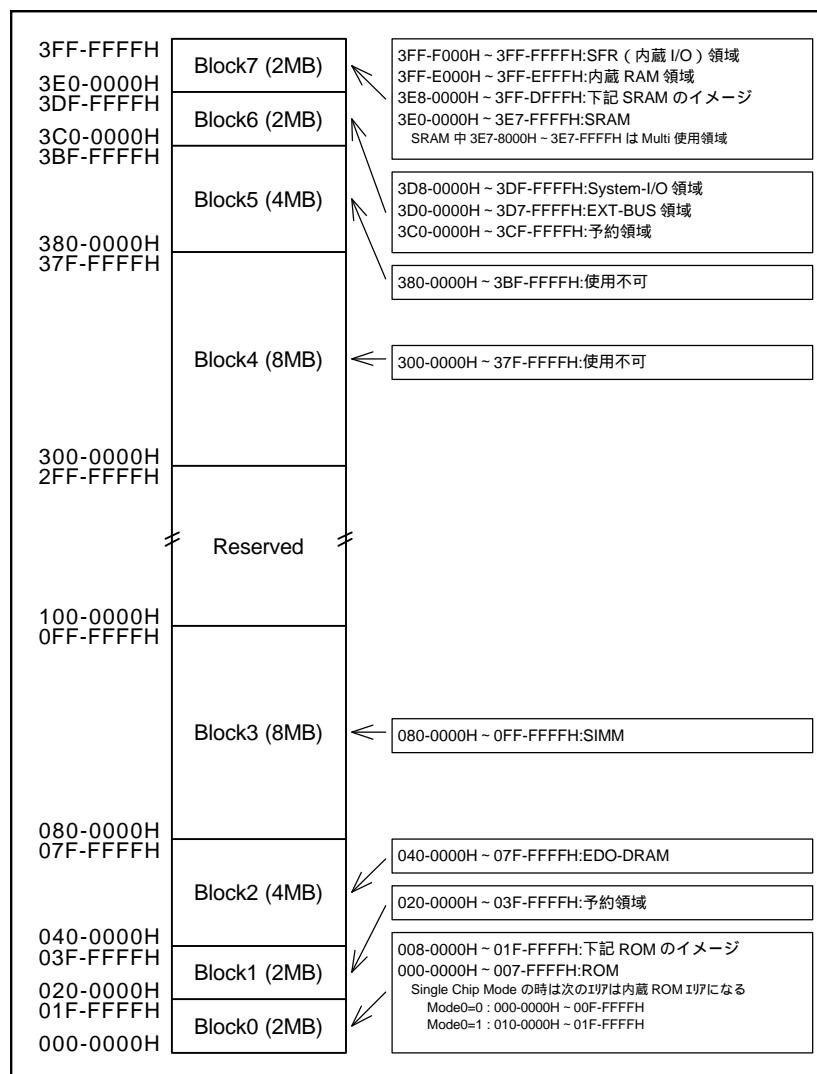

ボードのメモリ割り付けは、以下の通りです。

メモリ・マップ

## 5.2. メモリ・マップ詳細

メモリ・マップの詳細を以下に示します。各メモリ空間をアクセスするために必要なSFRの設定は『12ソフトウェア』を参照してください。

### CS0 空間 (Block0 : 000-0000H ~01F-FFFFH、16Bit、ROM 空間)

ボード上に実装されたROM用の空間です。ROMとして使用できるのは最大512Kバイトですが、標準では64K×16ビット(128Kバイト)アクセス・タイム120nS以下のROMが実装されています。ウェイト制御はCPUのプログラマブル・ウェイト機能を使用します。必要ウェイト数は『12ソフトウェア』を参照してください。

なお、標準で実装されているROMには、Multiと接続してデバッグするためのモニタが組み込まれています。

CPUがシングルチップ・モードの場合は、この領域の一部にCPU内蔵のフラッシュROMが現れます。CPUのMODE0端子がLowの時は000-0000H~00F-FFFFHに、MODE0端子がHighの時は010-0000H~01F-FFFFHに内蔵フラッシュROM領域が現れます。これらの領域以外であればシングルチップ・モードであっても外部ROMをアクセスすることができます。

**内蔵フラッシュROM領域は1Mバイト空間ありますが、実際のフラッシュROMは128Kバイトです。**

### CS1 空間 (Block1 : 020-0000H ~03F-FFFFH、16Bit、予約領域)

システムで予約した領域です。この領域にはアクセスしないでください。アクセスした場合の動作は保障されません。

### CS2 空間 (Block2 : 040-0000H ~07F-FFFFH、16Bit、EDO-DRAM 空間)

ボード上に実装されたEDO-DRAM(Hyper-Page)の空間です。EDO-DRAMは、2M×8Bit×2個(4Mバイト)が搭載されています。データバスの幅は16ビットに設定します。

### CS3 空間 (Block3 : 080-0000H ~0FF-FFFFH、16Bit、SIMM 空間)

ボード上に実装されたSIMM用ソケットの空間です。SIMMを搭載しない場合は、CPUコネクタを使用した拡張のための空間として使用することができます。

SIMMは4Mバイトと8Mバイトのもののみが使用可能です。また、Fast-PageとHyper-Pageのいずれのタイプも実装することができます。

### CS4 空間 (Block4 : 300-0000H ~37F-FFFFH、DMA 使用時使用不可)

DMAを使用する場合、CPUのCS4-/RAS4-/IOWR-/P84端子をIOWR-として使用するため、この空間は使用できません。DMAを全く使用しない場合は、この空間をCPUコネクタを使用した拡張のための空間として使用することができます。この場合、IORD-およびIOWR-を使用しないようにディップ・スイッチの設定を行う必要があります(『3.1.1ディップ・スイッチ1(SW1)』を参照)。

### CS5 空間 (Block5 : 380-0000H ~3BF-FFFFH、DMA 使用時使用不可)

DMAを使用する場合、CPUのCS5-/RAS5-/IORD-/P85端子をIORD-として使用するため、この空間は使用できません。DMAを全く使用しない場合は、CPUコネクタを使用した拡張のための空間として使用することができます。この場合、IORD-およびIOWR-を使用しないようにディップ・スイッチの設定を行う必要があります(『3.1.1ディップ・スイッチ1(SW1)』を参照)。

### CS6 空間 (Block6 : 3C0-0000H ~ 3DF-FFFFH、16Bit、拡張 / I/O 空間)

この空間は以下の 3 つの空間に分かれています。Wait 制御は CPU の WAIT-端子を使用してハードウェアが行っています。

#### 予約領域 (3C0-0000H ~ 3CF-FFFFH):

システムで予約した領域です。この領域にはアクセスしないでください。アクセスした場合の動作は保障されません。

#### EXT-BUS 領域 (3D0-0000H ~ 3D7-FFFFH):

EXT-BUS に割り当てられた空間です。EXT-BUS のメモリ空間に対しても I/O 空間に对しても、この領域を使用してアクセスします。EXT-BUS の 16M バイトのアドレス空間に対してこの領域は 512K バイトしかないため、上位のアドレスはバンク・ポートで指定します。また、EXT-BUS のメモリ、I/O のいずれの空間をアクセスするかもバンク・ポートで指定します (『6.10EXT-BUS CPU-Core 用バンク・ポート(3D8-00B0H[Read/Write])』、『6.11EXT-BUS DMA0 用バンク・ポート(3D8-00C0H[Read/Write])』、『6.12EXT-BUS DMA1 用バンク・ポート(3D8-00D0H[Read/Write])』を参照)。

#### System-I/O 領域 (3D8-0000H ~ 3DF-FFFFH):

ボード上に実装されているタイマー、シリアル / パラレル・ポートや、その他の制御ポートが割り付けられています (『6.1SYSTEM-IO 一覧』を参照)。

### CS7 空間 (Block7 : 3E0-0000H ~ 3FF-FFFFH、16Bit、SRAM 空間)

ボード上に実装された SRAM 用の空間です。SRAM は  $128K \times 8\text{Bit} \times 4$  個 (512K バイト) アクセス・タイム 15nS のものが実装されています。ウェイト制御は CPU のプログラマブル・ウェイト機能を使用します。必要ウェイト数は『12ソフトウェア』を参照して下さい。

この領域には、CPU の内蔵 RAM と内蔵 I/O (SFR) の空間があるため、3FF-E000H ~ 3FF-FFFFH の空間からは SRAM がアクセスできません。

## 6. SYSTEM-IO

SYSTEM-IO は、メモリ空間にマップされた I/O デバイスで UART/PRINTER, TIC, ISA バス・インターフェースなどがあります。

### 6.1. SYSTEM-IO 一覧

SYSTEM-IO の一覧を以下の表に示します。

| アドレス                  | 機能                                  | 備考         |

|-----------------------|-------------------------------------|------------|

| 3D8-0000H ~ 3D8-000EH | UART-CH#0(TL16PIR552)設定 / 参照        |            |

| 3D8-0010H ~ 3D8-001EH | UART-CH#1(TL16PIR552)設定 / 参照        |            |

| 3D8-0020H ~ 3D8-002EH | PRINTER(PPCS-)(TL16PIR552)設定 / 参照   |            |

| 3D8-0030H ~ 3D8-003EH | PRINTER(ECPICS-)(TL16PIR552)設定 / 参照 |            |

| 3D8-0040H ~ 3D8-0046H | タイマコントローラ(uPD71054)設定 / 参照          | リカバリタイムが必用 |

| 3D8-0050H             | 7セグメント LED 表示データ設定                  |            |

| 3D8-0050H             | DIPSW7 参照                           |            |

| 3D8-0060H             | ステータス参照(SIMM-PD,etc)                |            |

| 3D8-0070H ~ 3D8-007FH | システム予約                              | アクセス禁止     |

| 3D8-0080H             | コントロール・ポート設定 / 参照(Mask, Tover,etc)  |            |

| 3D8-0090H             | NMI, 割り込みセレクト設定 / 参照                |            |

| 3D8-00A0H             | 割り込みステータス参照                         |            |

| 3D8-00B0H             | EXT-BUS CPU-Core 用バンクポート設定 / 参照     |            |

| 3D8-00C0H             | EXT-BUS DMA0 用バンクポート設定 / 参照         |            |

| 3D8-00D0H             | EXT-BUS DMA1 用バンクポート設定 / 参照         |            |

| 3D8-00E0H ~ 3D8-00FFH | システム予約                              | アクセス禁止     |

## 6.2. UART/PRINTER (TL16PIR552) (3D8-0000H ~ 3D8-003EH)

UART/PRINTER として TEXAS INSTRUMENTS 製の TL16PIR552(DUAL UART WITH 1284 PARALLEL PORT)LSIを使用しています。TL16PIR552 は、UART を 2 チャンネル、IEEE1284 準拠の双方向プリンタ・ポートを 1 チャンネル備えており、UART の送受信部には 16 キャラクタ分の FIFO バッファを持ち、RTS/CTS フローを自動的に制御する機能を備えているため、最小限の割り込みでオーバーラン・エラーを押さえられます。

TL16PIR552 はの各レジスタは、表のように割り付けられています。各レジスタの機能については、TL16PIR552 のマニュアルを参照してください。

| アドレス                  | 機能              | 読み出し                          | 書き込み                    |

|-----------------------|-----------------|-------------------------------|-------------------------|

| 3D8-0000H             | UART-CH#0       | RBR/DLL                       | THR/DLL                 |

| 3D8-0002H             |                 | IER/DLM                       | IER/DLM                 |

| 3D8-0004H             |                 | IIR                           | FCR                     |

| 3D8-0006H             |                 | LCR                           | LCR                     |

| 3D8-0008H             |                 | MCR                           | MCR                     |

| 3D8-000AH             |                 | LSR                           | LSR                     |

| 3D8-000CH             |                 | MSR                           | MSR                     |

| 3D8-000EH             |                 | SCR                           | SCR                     |

| 3D8-0010H             | UART-CH#1       | RBR/DLL                       | THR/DLL                 |

| 3D8-0012H             |                 | IER/DLM                       | IER/DLM                 |

| 3D8-0014H             |                 | IIR                           | FCR                     |

| 3D8-0016H             |                 | LCR                           | LCR                     |

| 3D8-0018H             |                 | MCR                           | MCR                     |

| 3D8-001AH             |                 | LSR                           | LSR                     |

| 3D8-001CH             |                 | MSR                           | MSR                     |

| 3D8-001EH             |                 | SCR                           | SCR                     |

| 3D8-0020H             | PRINTER(PPCS-)  | DATA                          | DATA/ECPAIFO            |

| 3D8-0022H             |                 | DSR                           | ----                    |

| 3D8-0024H             |                 | DCR                           | DCR                     |

| 3D8-0026H             |                 | EPPADDR                       | EPPADDR                 |

| 3D8-0028H ~ 3D8-002EH |                 | EPPDATA                       | EPPDATA                 |

| 3D8-0030H             | PRINTER(ECPCS-) | PPDATAFIFO/<br>TESTFIFO/CNFGA | PPDATAFIFO/<br>TESTFIFO |

| 3D8-0032H             |                 | CNFGB                         | ----                    |

| 3D8-0034H             |                 | ECR                           | ECR                     |

TL16C552A レジスタ配置

TL16PIR552 の XIN 入力には 22.1184MHz のクロックが接続されています。UART-CH#0、UART-CH#1、PRINTER の各割り込みは下表のように CPU の割り込みに接続することができます。

| 割り込み発生元   | 接続 CPU 割り込み                           | 割り込みエッジ  |

|-----------|---------------------------------------|----------|

| UART-CH#0 | NMI/P20, INTP130/P34, INTP131/SO2/P35 | 立ち上がりエッジ |

| UART-CH#1 | INTP132/SI2/P36                       | 立ち上がりエッジ |

| PRINTER   | INTP133/SCK2-/P37                     | 立ち上がりエッジ |

マスカブル割り込みはディップ・スイッチの SW2 を経由しています。NMI については『9.3NMI』を、マスカブル割り込みについては『9.4INTP130/P34』および『9.12ポート(タイプ3)』を参照してください。

UART-CH#0 はボードのリアパネルにある JSIO1 コネクタに、UART-CH#1 は JSIO2 コネクタ、PRINTER は JPRT に接続しています。また、UART-CH#0 は Multi をシリアル通信で用いる場合に使用され、その時に NMI を使用します。

TL16PIR552 は、システム・リセットによってリセットされます。

### 6.3. TIC (uPD71054) (3F-F040H ~ 3F-F048H)

TIC は NEC 製の uPD71054 が実装されています。uPD71054 は Intel 製の i8254 と互換であり、3 つのタイマ / カウンタを持っています。これらのタイマ / カウンタにより、モニタのタイマ割り込みの生成を行っています。

TIC の各レジスタは、表の通りに割り当てられています。

| アドレス      | 読み出し      | 書き込み         |

|-----------|-----------|--------------|

| 3D8-0040H | COUNTER#0 | COUNTER#0    |

| 3D8-0042H | COUNTER#1 | COUNTER#1    |

| 3D8-0044H | COUNTER#2 | COUNTER#2    |

| 3D8-0046H | ----      | Control Word |

TIC のレジスタ配置

TIC の各チャネルは下図のよう接続されています。

チャネル 0 は、NMI および INTP130 生成回路に接続され、Multi 用 ROM モニタ・プログラムのインターバル・タイマとして使用されます。クロック入力には 2MHz が接続されています。

チャネル 1 は、ユーザのプログラムで自由に使用することができます。CPU の INTP140/P114 に接続されています。同時にチャネル 1 はチャネル 2 のプリスケール・カウンタとして機能します。

チャネル 2 は、ユーザのプログラムで自由に使用することができます。割り込みには接続されません。チャネル 1 およびチャネル 2 に接続されているクロックは、ボード上の JP6 により 2MHz か 4MHz のいずれかを選択して接続できます。

uPD71054 はコマンド・リカバリ・タイムとして 165ns 必要とします。リカバリ・タイムについては『12ソフトウェア』を参照してください。

TIC は、システム・リセットによってリセットされます。

#### 6.4. 7セグメントLED表示データ出力ポート(3D8-0050H [Write Only])

ボード上の7セグメントLEDに表示するデータを設定します。データ・フォーマットを下表に示します。該当するビットに0を設定すると対応するセグメントが点灯します。

電源投入時の初期値は不定です。

| Bit7  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------|------|------|------|------|------|------|------|

| DPseg | Gseg | Fseg | Eseg | Dseg | Cseg | Bseg | Aseg |

#### 6.5. DIPSW7 読み出しポート(3D8-0050H [Read Only])

ボード上のDIPSW7の状態を読み出すためのポートです。データ・フォーマットを下表に示します。

| Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SW7-8 | SW7-7 | SW7-6 | SW7-5 | SW7-4 | SW7-3 | SW7-2 | SW7-1 |

SW7-[8..1] : ボード上に実装されているSW7の状態を読み出せます。SW7-1がSW7の"1"のスイッチに、SW7-8がSW7の"8"のスイッチに対応します。該当するビットのスイッチがONで0、OFFで1が読み出されます。

このスイッチはモニタの動作設定用のスイッチとして使用しています。設定方法は、ご使用のモニタに該当する付録の章を参照してください。

#### 6.6. Status 読み出しポート(3D8-0060H [Read Only])

| Bit7      | Bit6       | Bit5       | Bit4      | Bit3 | Bit2 | Bit1 | Bit0 |

|-----------|------------|------------|-----------|------|------|------|------|

| NMI/INTP- | SFLASH_BY- | SFLASH_WP- | SIMM_EDO- | PD4  | PD3  | PD2  | PD1  |

PD[4..1] : ボードに実装されているDRAM(72ピンSIMM)のPD[4..1]が読み出せます。PD[2..1]の状態によって、実装されているDRAMのサイズを確認できます。PD[2..1]とDRAMの容量の関係を表に示します。

| PD[2] | PD[1] | DRAMの容量      |

|-------|-------|--------------|

| 0     | 0     | 4Mバイト        |

| 0     | 1     | 予約           |

| 1     | 0     | 16Mバイト(使用不可) |

| 1     | 1     | 8Mバイト        |

PD[2..1]とDRAMの容量

**SIMM\_EDO-** : DIPSW4-4 の状態が読み出せます。このスイッチはボード上の SIMM ソケットに搭載されている SIMM が EDO であるかそうでないかをユーザが設定します。この機能はソフトウェア的に定義されているものであり、スイッチの切り替えがハードウェアに作用して機能を切り替えるものではありません。DIPSW4-4 が OFF で”1”、ON で”0”が読み出せます。このスイッチの状態によりソフトウェアは CPU 内部(SFR)の設定を変更することができます。

**SFLASH\_WP-** : DIPSW4-1 の状態が読み出せます。このスイッチはシステムで予約されていますので、OFF で使用してください。将来の拡張に備え、このビットからどのような値が読み出されても、影響のないようにプログラムしてください。

**SFLASH\_BY-** : システム予約です。将来の拡張に備え、このビットからどのような値が読み出されても、影響のないようにプログラムしてください。

**NMI/INTP-** : DIPSW4-5 の状態が読み出せます。このスイッチはシステムで予約されていますので、OFF で使用してください。将来の拡張に備え、このビットからどのような値が読み出されても、影響のないようにプログラムしてください。

## 6.7. コントロール・ポート(3D8-0080H [Read/Write])

割り込み関係の制御ビットがあります。電源投入時、およびリセット時の初期値は 0x03 です。

| Bit7 | Bit6 | Bit5 | Bit4       | Bit3        | Bit2        | Bit1         | Bit0     |

|------|------|------|------------|-------------|-------------|--------------|----------|

| 未使用  | 未使用  | 未使用  | SFLASH_RP- | TM0_INT_CLR | TOV_INT_CLR | INTP130_MASK | NMI_MASK |

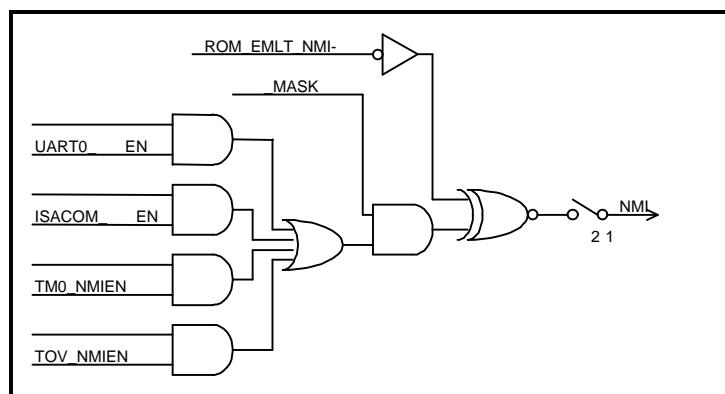

**NMI\_MASK** : NMI の最終的なマスクを制御するポートです。NMI 信号の生成ロジックについては『9.3NMI』を参照してください。

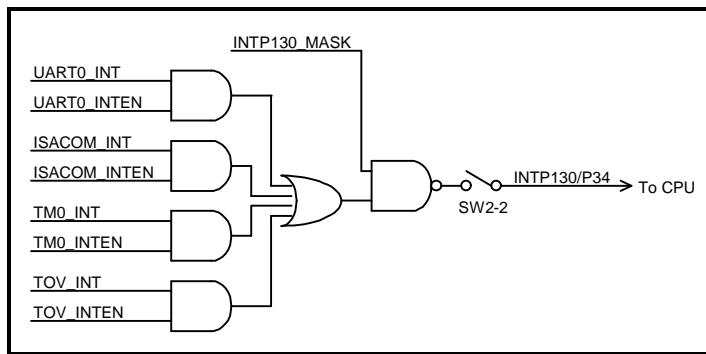

**INTP130\_MASK** : INTP130 の最終的なマスクを制御するポートです。INTP130 信号の生成ロジックについては『9.4INTP130/P34』を参照してください。

**TOV\_INT\_CLR** : CPU のレディー・タイムアウトによる割り込みは、ハード的に保持され CPU に接続しています。このビットはこの保持された割り込みの状態をクリアするビットです。このビットを一旦”1”に設定し”0”に戻すと、割り込み発生の保持状態がクリアされます。通常は”0”に設定しておきます。

**TM0\_INT\_CLR** : TIC ( μPD71054) のチャンネル 0 による割り込みの発生は、ハード的に保持され CPU に接続しています。このビットはこの保持された割り込みの状態をクリアするビットです。このビットを一旦”1”に設定し”0”に戻すと、割り込み発生の保持状態がクリアされます。通常は”0”に設定しておきます。

**SFLASH\_RP-** : システムで予約しています。将来の拡張に備え、設定されている値を変化させないようにプログラムして下さい。具体的には、設定を変える場合は一端読み出した後、設定を変えるビットのみを操作して、書き込んでください。

**未使用** : 未使用のビットは、将来の拡張に備え、設定されている値を変化させないようにプログラムしてください。具体的には、設定を変える場合は一端読み出した後、設定を変えるビットのみを操作して、書き込んでください。

### 6.8. NMI/INTP130 セレクト・ポート(3D8-0090H[Read/Write])

NMI および INTP130 の生成を制御するポートです。NMI および INTP130 信号の生成ロジックについては『9.3NMI』および『9.4INTP130/P34』を参照してください。

電源投入時、およびリセット時の初期値は 0x00 です。

| Bit7      | Bit6      | Bit5         | Bit4        | Bit3      | Bit2      | Bit1         | Bit0        |

|-----------|-----------|--------------|-------------|-----------|-----------|--------------|-------------|

| TOV_INTEN | TM0_INTEN | ISACOM_INTEN | UART0_INTEN | TOV_NMIEN | TM0_NMIEN | ISACOM_NMIEN | UART0_NMIEN |

各ビットは該当割り込み要求により NMI もしくは INTP130 を発生される時"1"に、発生させない時に"0"に設定します。

UART0\_NMIEN,UART0\_INTEN : TL16PIR552 の UART-CH#0 の割り込み要求

ISACOM\_NMIEN,ISACOM\_INTEN : ISA バスとの通信による割り込み要求

TM0\_NMIEN,TM0\_INTEN : TIC(uPD71054)の TOUT0 による割り込み要求

TOV\_NMIEN,TOV\_INTEN : タイムオーバ・レディーの発生による割り込み要求

### 6.9. NMI/INTP130 ステータス・ポート(3D8-00A0H [Read only])

NMI 要求および INTP130 要求の要求元を特定するためのポートです。NMI および INTP130 信号の生成ロジックについては『9.3NMI』および『9.4INTP130/P34』を参照してください。

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3      | Bit2      | Bit1         | Bit0        |

|------|------|------|------|-----------|-----------|--------------|-------------|

| ---  | ---  | ---  | ---  | TOV_INTRQ | TM0_INTRQ | ISACOM_INTRQ | UART0_INTRQ |

各ビットは該当割り込み要求が発生している時"1"が、発生していない時"0"が読み出せます。各ビットは、各割り込み要求元の割り込み要求状態を示し、NMI/INTP130 セレクト・ポートの設定の影響を受けません。従って、NMI/INTP130 ステータス・ポートの内容と NMI/INTP130 セレクト・ポートの内容を AND したものが、NMI および INTP130 の発生の原因となっている割り込み要因です。

UART0\_INTRQ : TL16PIR552 の UART-CH#0 の割り込み要求

ISACOM\_INTRQ : ISA バスとの通信による割り込み要求

TM0\_INTRQ : TIC(uPD71054)の TOUT0 による割り込み要求

TOV\_INTRQ : タイムオーバ・レディーの発生による割り込み要求

### 6.10. EXT-BUS CPU-Core 用バンク・ポート(3D8-00B0H[Read/Write])

メモリマップの 3D0-0000H ~ 3D7-FFFFH で EXT-BUS をアクセスする時、EXT-BUS に出力されるアドレスの A[23:19]を設定するポートです。また、EXT-BUS のメモリ空間へのアクセスか、I/O 空間へのアクセスかも設定します。このポートに設定するバンク・アドレスは、CPU-Core がアクセスする時 (プログラムにより CPU がアクセスする時) に使用されるものです。

電源投入時、およびリセット時の初期値は 0x01 です。

| Bit7      | Bit6      | Bit5      | Bit4      | Bit3      | Bit2 | Bit1 | Bit0      |

|-----------|-----------|-----------|-----------|-----------|------|------|-----------|

| CC_EXTA23 | CC_EXTA22 | CC_EXTA21 | CC_EXTA20 | CC_EXTA19 | 未使用  | 未使用  | CC_MEMSEL |

CC\_EXTA[23:19] : EXT-BUS のアドレス A[23:19]に出力される値を設定します。EXT-BUS のアドレス A[18:2]は、CPU のアドレス線がそのまま出力されます。

CC\_MEMSEL : 3D0-0000H ~ 3D7-FFFFH にアクセスした時に、EXT-BUS のメモリ空間にアクセスするのか I/O 空間にアクセスするのかを設定します。このビットを"1"に設定するとメモリ空間、"0"

に設定すると I/O 空間へアクセスします。

**未使用**：未使用のビットは、将来の拡張に備え、設定されている値を変化させないようにプログラムしてください。具体的には、設定を変える場合は一端読み出した後、設定を変えるビットのみを操作して、書き込んでください。

### 6.11. EXT-BUS DMA0 用バンク・ポート(3D8-00C0H[Read/Write])

メモリマップの 3D0-0000H ~ 3D7-FFFFH で EXT-BUS をアクセスする時、EXT-BUS に出力されるアドレスの A[23:19]を設定するポートです。また、EXT-BUS のメモリ空間へのアクセスか、I/O 空間へのアクセスかも設定します。このポートに設定するバンク・アドレスは、DMA のチャンネル 0 が 2 サイクル DMA でアクセスする時 (DMA サイクル) に使用されるものです。

電源投入時、およびリセット時の初期値は 0x01 です。

| Bit7      | Bit6      | Bit5      | Bit4      | Bit3      | Bit2 | Bit1      | Bit0      |

|-----------|-----------|-----------|-----------|-----------|------|-----------|-----------|

| D0_EXTA23 | D0_EXTA22 | D0_EXTA21 | D0_EXTA20 | D0_EXTA19 | 未使用  | D0_2CYCLE | D0_MEMSEL |

**D0\_EXTA[23:19]**：EXT-BUS のアドレス A[23:19]に出力される値を設定します。EXT-BUS のアドレス A[18:2]は、CPU のアドレス線がそのまま出力されます。

**D0\_2CYCLE**：CPU の DMA のチャンネル 0 を 2 サイクル DMA で用いる場合に、このビットを”1”に設定します。フライバイ DMA で用いる場合は”0”に設定します。

**D0\_MEMSEL**：3D0-0000H ~ 3D7-FFFFH にアクセスした時に、EXT-BUS のメモリ空間にアクセスするのか I/O 空間にアクセスするのかを設定します。このビットを”1”に設定するとメモリ空間、”0”に設定すると I/O 空間へアクセスします。

**未使用**：未使用のビットは、将来の拡張に備え、設定されている値を変化させないようにプログラムしてください。具体的には、設定を変える場合は一端読み出した後、設定を変えるビットのみを操作して、書き込んでください。

### 6.12. EXT-BUS DMA1 用バンク・ポート(3D8-00D0H[Read/Write])

メモリマップの 3D0-0000H ~ 3D7-FFFFH で EXT-BUS をアクセスする時、EXT-BUS に出力されるアドレスの A[23:19]を設定するポートです。また、EXT-BUS のメモリ空間へのアクセスか、I/O 空間へのアクセスかも設定します。このポートに設定するバンク・アドレスは、DMA のチャンネル 1 が 2 サイクル DMA でアクセスする時 (DMA サイクル) に使用されるものです。

電源投入時、およびリセット時の初期値は 0x01 です。

| Bit7      | Bit6      | Bit5      | Bit4      | Bit3      | Bit2 | Bit1      | Bit0      |

|-----------|-----------|-----------|-----------|-----------|------|-----------|-----------|

| D1_EXTA23 | D1_EXTA22 | D1_EXTA21 | D1_EXTA20 | D1_EXTA19 | 未使用  | D1_2CYCLE | D1_MEMSEL |

**D1\_EXTA[23:19]**：EXT-BUS のアドレス A[23:19]に出力される値を設定します。EXT-BUS のアドレス A[18:2]は、CPU のアドレス線がそのまま出力されます。

**D1\_2CYCLE**：CPU の DMA のチャンネル 1 を 2 サイクル DMA で用いる場合に、このビットを”1”に設定します。フライバイ DMA で用いる場合は”0”に設定します。

**D1\_MEMSEL**：3D0-0000H ~ 3D7-FFFFH にアクセスした時に、EXT-BUS のメモリ空間にアクセスするのか I/O 空間にアクセスするのかを設定します。このビットを”1”に設定するとメモリ空間、”0”に設定すると I/O 空間へアクセスします。

**未使用**：未使用のビットは、将来の拡張に備え、設定されている値を変化させないようにプログラムしてください。具体的には、設定を変える場合は一端読み出した後、設定を変えるビットのみを操

作して、書き込んでください。

## 7. EXT-BUS バス仕様

JEXT コネクタは、メモリや I/O などを拡張できるように用意された EXT-BUS 用のコネクタです。このコネクタには、本ボードの内部のローカル・バスが接続されています。

### 7.1. ピン配置

| 番号 | 信号名     | 番号 | 信号名     | 番号 | 信号名       | 番号  | 信号名     |

|----|---------|----|---------|----|-----------|-----|---------|

| 1  | GND     | 2  | +5V     | 3  | D0        | 4   | D1      |

| 5  | D2      | 6  | D3      | 7  | GND       | 8   | D4      |

| 9  | D5      | 10 | D6      | 11 | D7        | 12  | GND     |

| 13 | D8      | 14 | D9      | 15 | D10       | 16  | D11     |

| 17 | GND     | 18 | D12     | 19 | D13       | 20  | D14     |

| 21 | D15     | 22 | GND     | 23 | D16       | 24  | D17     |

| 25 | D18     | 26 | D19     | 27 | GND       | 28  | D20     |

| 29 | D21     | 30 | D22     | 31 | D23       | 32  | GND     |

| 33 | D24     | 34 | D25     | 35 | D26       | 36  | D27     |

| 37 | GND     | 38 | D28     | 39 | D29       | 40  | D30     |

| 41 | D31     | 42 | GND     | 43 | +5V       | 44  | GND     |

| 45 | Reserve | 46 | Reserve | 47 | (A1)      | 48  | A2      |

| 49 | A3      | 50 | A4      | 51 | GND       | 52  | A5      |

| 53 | A6      | 54 | A7      | 55 | A8        | 56  | A9      |

| 57 | A10     | 58 | GND     | 59 | A11       | 60  | A12     |

| 61 | A13     | 62 | A14     | 63 | A15       | 64  | A16     |

| 65 | GND     | 66 | A17     | 67 | A18       | 68  | A19     |

| 69 | A20     | 70 | A21     | 71 | A22       | 72  | A23     |

| 73 | GND     | 74 | +5V     | 75 | MRD-      | 76  | Reserve |

| 77 | MWR0-   | 78 | MWR1-   | 79 | MWR2-     | 80  | MWR3-   |

| 81 | IORD-   | 82 | IOWR-   | 83 | GND       | 84  | READY   |

| 85 | GND     | 86 | INT0-   | 87 | INT1-     | 88  | INT2-   |

| 89 | INT3-   | 90 | DMARQ0- | 91 | DMARQ1-   | 92  | DMAAK0- |

| 93 | DMAAK1- | 94 | RESET-  | 95 | 32/16BIT- | 96  | N/C     |

| 97 | +5V     | 98 | GND     | 99 | CLK       | 100 | GND     |

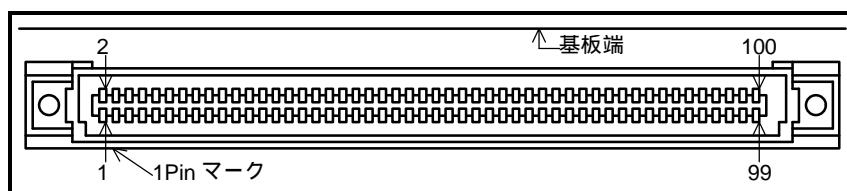

JEXT コネクタピン配置

JEXT のピン配置

## 7.2. 信号

| 信号名          | 入出力 | 機能                                                                                                                                                                                                                         |

|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[0..31]     | 入出力 | データ・バス信号。CPU のデータ・バス信号をバッファして接続。ボード上で 10K ブルアップ。                                                                                                                                                                           |

| A[1..23]     | 出力  | アドレス・バス信号。CPU のアドレス信号をバッファして接続。                                                                                                                                                                                            |

| MRD-         | 出力  | メモリ・リード・サイクルのタイミング信号。EXT-BUS 空間のアクセス時のみ、アクティブになる。                                                                                                                                                                          |

| MWR-[0..3]   | 出力  | メモリ・ライト・サイクルのタイミング信号。それぞれ、MWR0-は D[0..7]に、MWR1-は D[8..15]に、MWR2-は D[16..23]に、MWR3-は D[24..31]に対応。EXT-BUS 空間のアクセス時のみ、アクティブになる。                                                                                              |

| IORD-        | 出力  | I/O リード・サイクルのタイミング信号。EXT-BUS 空間のアクセス時、もしくはフライバイ DMA サイクルの時アクティブになる。                                                                                                                                                        |

| IOWR-        | 出力  | I/O ライト・サイクルのタイミング信号。EXT-BUS 空間のアクセス時、もしくはフライバイ DMA サイクルの時アクティブになる。                                                                                                                                                        |

| READY        | 入力  | サイクルの終了を CPU に通知する信号。EXT-BUS 空間のみで有効。確実に CPU に READY を認識させるためには、MRD-,MWR-[0..3],IORD-,IOWR-がインアクティブになるまで READY をアクティブに保つことが必要。ボード上で 10K ブルアップ。                                                                             |

| INT-[0..3]   | 入力  | Low アクティブの割り込み要求信号。バッファ後 SW3 を経由して、それぞれ CPU の INTP150,INTP151,INTP152,INTP153 端子に接続されている。ボード上で 10K ブルアップ。<br>( #0<br>ポート ( タイプ 3 ) <a href="#">参照</a>                                                                      |

| DMARQ-[0..1] | 入力  | Low アクティブの DMA 要求信号。バッファ後 SW1 を経由して、それぞれ CPU の DMARQ0-,DMARQ1-端子に接続されている。ボード上で 10K ブルアップ。<br>( #0<br>ポート ( タイプ 2 ) <a href="#">参照</a>                                                                                      |

| DMAAK-[0..1] | 出力  | Low アクティブの DMA 応答信号。CPU の DMAAK0-,DMAAK1-が、SW1 を経由後バッファされて接続されている。<br>( #0<br>ポート ( タイプ 3 ) <a href="#">参照</a>                                                                                                             |

| RESET-       | 出力  | Low アクティブのシステム・リセット信号。                                                                                                                                                                                                     |

| 32/16BIT-    | 入力  | この信号を Low にすると、CPU が 16Bit データバスの場合、D[15..0]のみが使用される。また、CPU が 32Bit データバスの場合、アドレスにより D[15..0]もしくは D[31..16]のいずれかが使用される (16 ビットバスモード)。High にすると、データバスの D[31..0]が使用される (32 ビットバスモード)。この信号はダイナミックに変化させてはならない。ボード上で 10K ブルアップ。 |

| CLK          | 出力  | クロック信号。V850E/MS1 の CLKOUT 端子がバッファ後、接続されている。                                                                                                                                                                                |

| Reserve      |     | 予約信号。EXT-BUS を使用するボードは、この端子に何も接続しないこと。                                                                                                                                                                                     |

JEXT コネクタ信号

### 注意事項 :

- 32/16BIT-信号は、将来の RTE-PC シリーズの全てでサポートされるとは限りません。EXT-BUS に接続するボードを将来の RTE-PC シリーズでも使用する予定の場合は、32 ビットバスモード

ドで動作するように設計してください。

- 2 . 32/16BIT-が Low の時は、MWR2-および MWR3-がアサートされることはありません。代わりに MWR0-および MWR1-がアサートされます。

また、32/16BIT-を Low にして使用する場合は、EXT-BUS に接続するボード上で D[15..0]と D[31..16]をショートしてください(『7.3データバスの接続』参照)。

- 3 . A1 は 32/16BIT-信号が Low の時有効です。したがって、32/16BIT-信号がサポートされていない将来の RTE-PC シリーズでは、A1 が出力されないことがあります。

- 4 . EXT-BUS バスの 1 回のサイクルでの最大アクセス・バス幅は、CPU のデータ・バスのバス幅に依存します。例えば 16 ビット・データバスの CPU の場合、I/O へのアクセスやフライバイ DMA でのアクセスの場合、最大 16 ビットまでのアクセスしかできません。

したがって、EXT-BUS に接続するボードの I/O サイクルやフライバイ DMA サイクルでアクセスされるポートは、接続しようとする CPU のデータバス幅以下のデータバス幅でなければならず、そのアドレスは  $4n+0$  番地に配置されていなければなりません。

- 5 . DMA 機能は、将来の RTE-PC シリーズの全てでサポートされるとは限りません。

### 7.3. データバスの接続

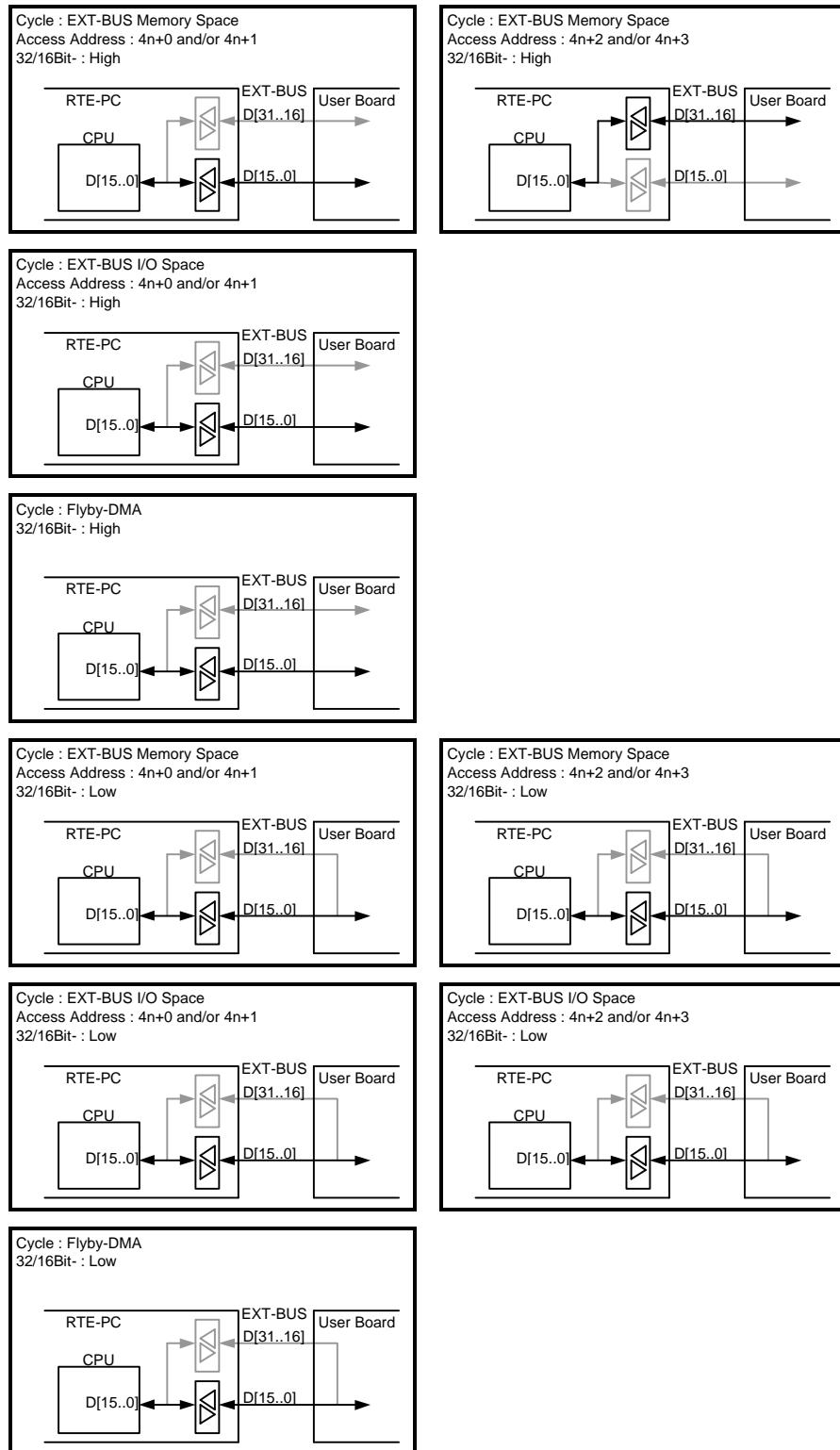

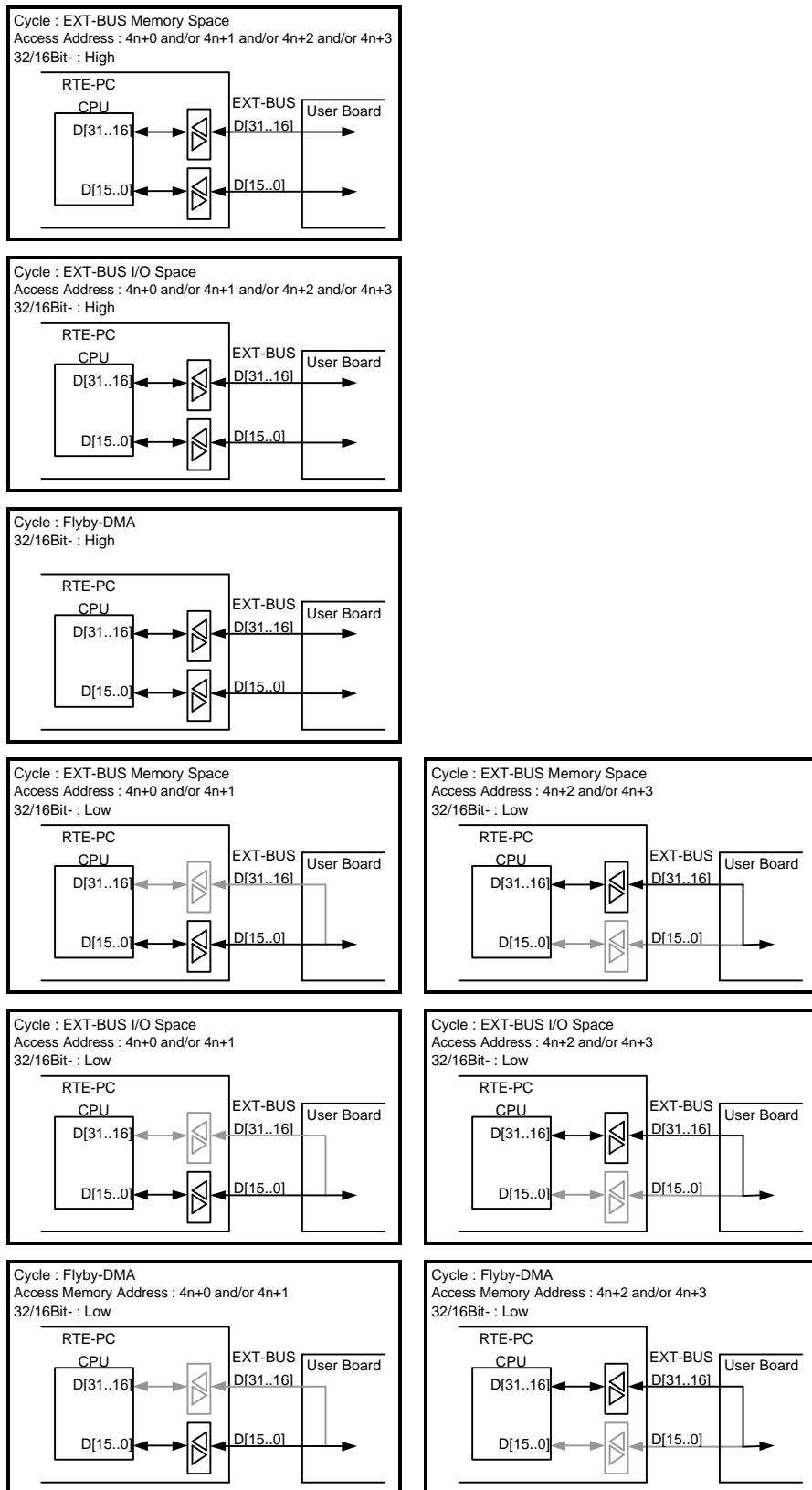

#### 7.3.1. 16 ビット・データバスCPU (V850E/MS1)

### 7.3.2. 32 ビット・データバスCPU (参考)

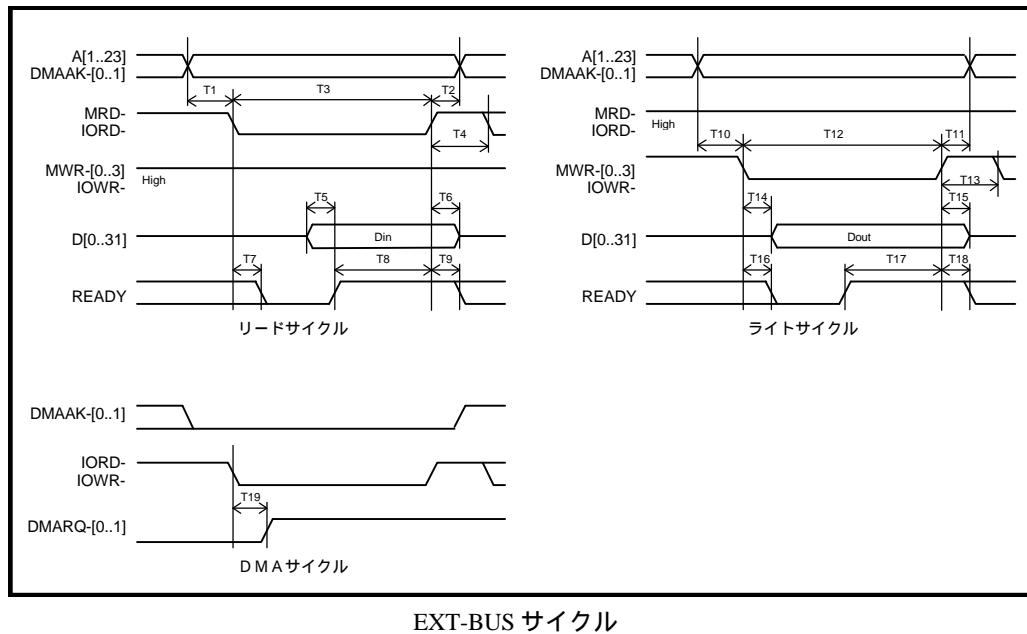

## 7.4. タイミング

| 記号  | 内容                              | MIN(ns) | MAX(ns) |

|-----|---------------------------------|---------|---------|

| T1  | ADDR,DMAAK- MRD-,IORD- セットアップ時間 | 10      |         |

| T2  | MRD-,IORD- ADDR,DMAAK- ホールド時間   | 10      |         |

| T3  | MRD-,IORD- サイクル時間               | 50      |         |

| T4  | MRD-,IORD- サイクル間隔               | 20      |         |

| T5  | RD DATA RD READY セットアップ時間       | 0       |         |

| T6  | MRD-,IORD- RD DATA ホールド時間       | 0       |         |

| T7  | MRD-,IORD- RD READY ディレイ時間      |         | 20      |

| T8  | RD READY MRD-,IORD- ディレイ時間      | 15      |         |

| T9  | MRD-,IORD- RD READY ホールド時間      | 0       |         |

| T10 | ADDR,DMAAK- MWR-,IOWR- セットアップ時間 | 10      |         |

| T11 | MWR-,IOWR- ADDR,DMAAK- ホールド時間   | 10      |         |

| T12 | MWR-,IOWR- サイクル時間               | 50      |         |

| T13 | MWR-,IOWR- サイクル間隔               | 20      |         |

| T14 | MWR-,IOWR- WR DATA ディレイ時間       |         | 20      |

| T15 | MWR-,IOWR- WR DATA ホールド時間       | 10      |         |

| T16 | MWR-,IOWR- WR READY ディレイ時間      |         | 20      |

| T17 | WR READY MWR-,IOWR- ディレイ時間      | 0       |         |

| T18 | MWR-,IOWR- WR READY ホールド時間      | 0       |         |

| T19 | IORD-,IOWR- DMARQ- インアクティブ遅延時間  |         | 20      |

EXT-BUS AC スペック

## 7.5. 適合コネクタ

EXT-BUS に使用しているコネクタと、そのコネクタに勘合する適合コネクタの型番を以下に示します。

複数のボードを EXT-BUS に接続する場合は、ケーブルを使用してデージーチェーン接続を行います。

|                       |                        |

|-----------------------|------------------------|

| EXT-BUS 使用コネクタ        | : KEL 社 8830E-100-170S |

| 適合コネクタ ( 基板用 )        | : KEL 社 8802-100-170S  |

| 適合コネクタ ( ケーブル用 )      | : KEL 社 8825E-100-1705 |

| 対ケーブル用ライトアングル ( 基板用 ) | : KEL 社 8830E-100-170L |

|                       | KEL 社 8831E-100-170L   |

## 7.6. 注意事項

EXT-BUS に接続するボードを設計する上での注意事項を以下に示します。

- 1 . 複数のボードを EXT-BUS に接続する場合は、READY 信号はボードが選択されているときのみドライブするように、Hi-Z 制御を行わなければなりません。

- 2 . EXT-BUS のサイクルにウェイトを挿入するためには、T7 および T16 を満足する必要があります。

- 3 . DMA サイクルをシングル転送モードで行う場合、次の DMA サイクルを確実に発生させないためには、タイミング図の T19 を満足する必要があります。ただし、この T19 は使用している DMA コントローラの仕様に大きく依存するため、将来の RTE-PC シリーズで変更される可能性があります。

- 4 . RTE-V850E/MS1-PC では、CPU に I/O 空間がないため、EXT-BUS の I/O 空間をアクセスするか、メモリ空間をアクセスするかは、ポートの設定に依存します (『6.10EXT-BUS CPU-Core 用バンク・ポート(3D8-00B0H[Read/Write])』『6.11EXT-BUS DMA0 用バンク・ポート(3D8-00C0H[Read/Write])』『6.12EXT-BUS DMA1 用バンク・ポート(3D8-00D0H[Read/Write])』参照 )。

- 5 . RTE-V850E/MS1-PC でサポートされる DMA 転送は、幾つかの空間の組み合わせのみです (『8DMA』参照)。

## 8. DMA

RTE-V850E/MS1-PC では、CPU 内蔵の DMA コントローラを使用して、EXT-BUS に接続した外部のボードと、RTE-V850E/MS1-PC 上のメモリの間で DMA 転送を行うことができます。

本章ではこの DMA 転送について説明します。

### 8.1. DMA 転送可能な空間

EXT-BUS を使用して DMA 転送可能な空間は以下の組み合わせです。

#### フライバイ転送時

EXT-BUS I/O 空間 RTE-V850E/MS1-PC 上 SRAM

EXT-BUS I/O 空間 RTE-V850E/MS1-PC 上 DRAM

EXT-BUS I/O 空間 RTE-V850E/MS1-PC 上 SIMM

#### 2 サイクル転送時

EXT-BUS 任意の空間 RTE-V850E/MS1-PC 上任意の空間

### 8.2. DMA チャンネル

EXT-BUS の DMA 信号と CPU の DMA チャンネルの関係を以下に示します。

| EXT-BUS 信号      | CPU DMA チャンネル |

|-----------------|---------------|

| DMARQ0-,DMAAK0- | チャンネル 0       |

| DMARQ1-,DMAAK1- | チャンネル 1       |

### 8.3. DIPSW の設定

EXT-BUS で DMA 転送を行う場合は、次の DIPSW を ON にする必要があります(『3.1.1 ディップ・スイッチ 1 ( SW1 )』参照)。

| 使用する DMA | DIPSW1 の設定 |    |    |    |    |    |

|----------|------------|----|----|----|----|----|

|          | 1          | 2  | 3  | 4  | 7  | 8  |

| チャンネル 0  | ON         | ON |    |    | ON | ON |

| チャンネル 1  |            |    | ON | ON | ON | ON |

### 8.4. CPU の設定

DMA 転送を行うためには、使用するチャンネルの DMARQ-および DMAAK-端子が、DMA に使用するように設定されていることと、CS4-/RAS4-/IOWR-/P84 および CS5-/RAS5-/IORD-/P85 がそれぞれ IOWR-と IORD-として使用するように CPU の SFR が設定されていなければなりません。

### 8.5. バンクポート設定(2 サイクルDMA)

EXT-BUS で 2 サイクル DMA 転送を行う場合は、EXT-BUS の DMA バンクポートを設定する必要があります。DMA でアクセスする空間が EXT-BUS のメモリ空間か I/O 空間かも設定します(『6.11 EXT-BUS DMA0 用バンク・ポート(3D8-00C0H[Read/Write])』『6.12 EXT-BUS DMA1 用バンク・ポート(3D8-00D0H[Read/Write])』参照)。

EXT-BUS 用のバンクポートが、CPU-Core 用、DMA チャンネル 0 用、DMA チャンネル 1 用の 3 つが用意されているため、DMA 転送中であっても EXT-BUS の任意のアドレスにプログラムでアクセスすることができます。

また、1 度の DMA 転送で、EXT-BUS の複数のバンクにまたがった転送を行うことはできません。バンクにまたがった転送を行う場合は、バンク空間ごとに DMA 転送を行うようにしてください。

## 8.6. バンクポート設定(フライバイDMA)

フライバイ DMA 転送の場合、I/O 側のアドレスは不要なため、バンクポートのアドレスの設定は必要ありません。しかし、フライバイ DMA を行うことをバンクポートに設定する必要があります(『6.11EXT-BUS DMA0 用バンク・ポート(3D8-00C0H[Read/Write])』、『6.12EXT-BUS DMA1 用バンク・ポート(3D8-00D0H[Read/Write])』参照)。ただしバンクポートの設定は、どちらのチャンネルもフライバイ DMA を行う設定にリセット時にハード的にクリアされますので、リセット後バンクポートに何も書き込んでいなければ、バンクポートの設定を行わずにフライバイ DMA 転送を行うことができます。

## 8.7. モニタ使用時

モニタでは、タイマ割り込みや通信割り込みに、NMI を使用します。したがって、タイマ割り込みや通信で NMI が発生するため、その度に DMA が停止します。ROM モニタは DMA の再開を行いますが、停止している間 DMA が保留されます。

タイミング的にクリティカルな DMA を行う場合は、タイマ割り込みを停止するか、DMA 転送中は一時的に NMI をマスク(『6.7コントロール・ポート(3D8-0080H [Read/Write])』参照)して下さい。ただし、NMI がマスクされている間は如何なるブレークもできなくなります。

- Multi のプロファイル機能を使用するとタイマによるNMI 割り込みが入ります。したがって、プロファイル・タイマを停止することで、タイマ割り込みによるNMI は発生しなくなります。

- デバッガからの非同期のブレーク要求や、ブレーク・ポイントによるブレーク発生のデバッガへの通知には通信が使用されます。この通信はNMI によりハンドリングされているため、NMI を禁止にするとブレークができなくなります。

## 9. CPU 端子接続

本章では、RTE-V850E/MS1-PC 内での CPU の各端子の使用状態を説明します。

### 9.1. 一覧

下表は CPU 端子の使用状態の一覧です。詳細は後続の章で説明します。

| 端子名                                  | 使用状態                                                    | 参照章  |

|--------------------------------------|---------------------------------------------------------|------|

| A0/PA0 ~ A7/PA7                      | アドレスバスとして使用                                             |      |

| A8/PB0 ~ A15/PB7                     |                                                         |      |

| A16/P60 ~ A22/P66                    |                                                         |      |

| A23/P67                              | ユーザ使用可能                                                 | 9.10 |

| ADV-/BCYST-/P94                      | システム予約                                                  |      |

| ANI0/P70 ~ ANI7/P77                  | ユーザ使用可能                                                 | 9.9  |

| AVREF, AVSS, AVDD                    |                                                         |      |

| CKSEL                                | CKSEL 端子として使用                                           | 9.5  |

| CS0-/RAS0-/P80                       | CS0 空間のチップセレクトとして使用                                     |      |

| CS1-/RAS1-/P81                       | システム予約                                                  |      |

| CS2-/RAS2-/P82                       | EDO-DRAM の RAS-として使用                                    |      |

| CS3-/RAS3-/P83                       | SIMM の RAS-として使用                                        |      |

| CS4-/RAS4-/IOWR-/P84                 | DMA を使用する場合は IOWR-として使用<br>DMA を使用しない場合はユーザ使用可能         | 0    |

| CS5-/RAS5-/IORD-/P85                 | DMA を使用する場合は IORD-として使用<br>DMA を使用しない場合はユーザ使用可能         | 0    |

| CS6-/RAS6-/P86                       | CS6 空間のチップセレクトとして使用                                     |      |

| CS7-/RAS7-/P87                       | CS7 空間のチップセレクトとして使用                                     |      |

| D0/P40 ~ D7/P47                      | データバスとして使用                                              |      |

| D8/P50 ~ D15/P57                     |                                                         |      |

| HLDAK-/P96, HLDRQ-/P97               | ユーザ使用可能                                                 | 9.10 |

| INTP100/DMARQ0-/P04                  | EXT-BUS の DMA を使用する場合は DMARQ-として使用、DMA を使用しない場合はユーザ使用可能 | 0    |

| INTP101/DMARQ1-/P05                  |                                                         |      |

| INTP102/DMARQ2-/P06                  | システムで使用できるように回路が構成されているが、現在はシステムでは使用していないため、ユーザ使用可能     | 0    |

| INTP103/DMARQ3-/P07                  | ユーザ使用可能                                                 | 9.10 |

| INTP110/DMAAK0-/P14                  | EXT-BUS の DMA を使用する場合は DMAAK-として使用、DMA を使用しない場合はユーザ使用可能 | 0    |

| INTP111/DMAAK1-/P15                  |                                                         |      |

| INTP112/DMAAK2-/P16                  | システムで使用できるように回路が構成されているが、現在はシステムでは使用していないため、ユーザ使用可能     | 0    |

| INTP113/DMAAK3-/P17                  | ユーザ使用可能                                                 | 9.10 |

| INTP130/P34                          | INTP として使用、割り込みを使用しない場合はユーザ使用可能                         | 9.4  |

| INTP131/SO2/P35                      | INTP として使用、割り込みを使用しない場合はユーザ使用可能                         | 0    |

| INTP132/SI2/P36, INTP133/SCK2-/P37   |                                                         |      |

| INTP140/P114, INTP141/SO3/P115       | INTP として使用、割り込みを使用しない場合はユーザ使用可能                         | 0    |

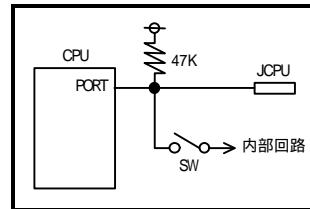

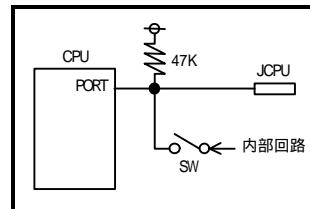

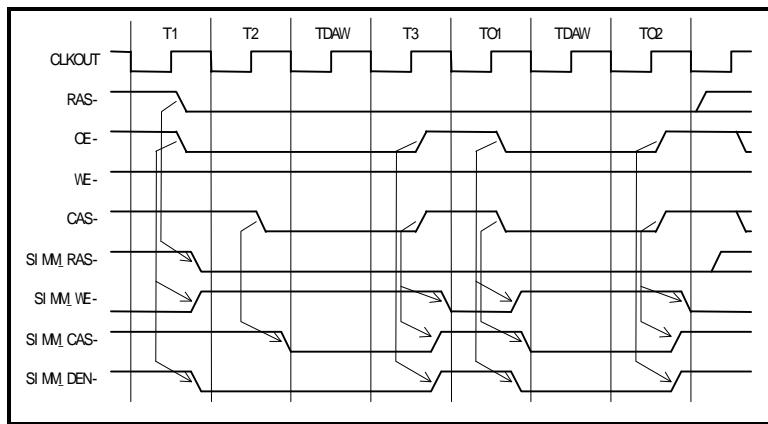

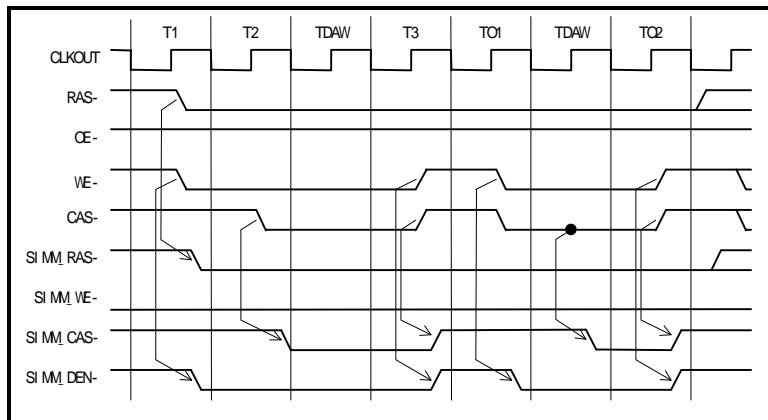

| INTP142/SI3/P116, INTP143/SCK3-/P117 | ユーザ使用可能                                                 | 9.10 |