# ***RTE-V852-PC***

**ユーザーズ・マニュアル (Rev. 1.12)**

***Midas lab***

## 改訂履歴

| 実施日         | Revision | 章                                  | 内容                                                                                                                                                                                           |

|-------------|----------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1996年8月15日  | 1.00     |                                    | 初版                                                                                                                                                                                           |

| 1996年9月12日  | 1.10     | 14,15                              | 14章、15章の追加                                                                                                                                                                                   |

| 1996年10月8日  | 1.11     | 3<br>3.15<br>4.1<br>5.1<br>8<br>xx | RTE-V852-PC 概観図へ SW3 を追記<br>リファレンスの章を追記<br>ボードのスイッチの図に SW3 を追記<br>メモリ・マップに Multi Monitor 使用領域を追記<br>JEXT コネクタ信号の表中、INT-の機能説明における誤記訂正とリファレンス追記<br>誤記訂正 : INT0(P24/INTP03) -> INT0(P22/INTP01) |

| 1996年11月25日 | 1.12     | 9<br>34                            | 誤記訂正 : port2 のピンレイアウト表(P22,P21)<br>誤記訂正 : JEXT コネクタ信号表(CLK)                                                                                                                                  |

## 目次

|                                                                             |           |

|-----------------------------------------------------------------------------|-----------|

| <b>1. はじめに.....</b>                                                         | <b>5</b>  |

| 1.1. マニュアル表記について .....                                                      | 5         |

| <b>2. 特徴と機能.....</b>                                                        | <b>6</b>  |

| <b>3. ボードの構成.....</b>                                                       | <b>7</b>  |

| 3.1. リセット・スイッチ [ ソケットボード ] ( RESET_SW ) .....                               | 7         |

| 3.2. リセット・スイッチ [ ベースボード ] ( SW_RESET ) .....                                | 7         |

| 3.3. NMI スイッチ [ ソケットボード ] ( NMI_SW ) .....                                  | 7         |

| 3.4. 電源コネクタ [ ソケットボード / ベースボード ] ( JPOWER ) .....                           | 8         |

| 3.5. プロセッサ・ピンコネクタ [ ソケットボード ] ( JPORT0,JPORT1,JPORT2,JPORT3,JPORT10 ) ..... | 9         |

| 3.6. プロセッサ・ピンコネクタ [ ソケットボード / ベースボード ] ( J1,J2/J5,J6 ) .....                | 10        |

| 3.7. シリアル・コネクタ [ ソケットボード ] ( J3 ) .....                                     | 10        |

| 3.8. スイッチ 1 [ ソケットボード ] ( SW1 ) .....                                       | 11        |

| 3.9. スイッチ 2 [ ソケットボード ] ( SW2 ) .....                                       | 11        |

| 3.10. クリスタル・ソケット [ ソケットボード ] ( JP1 ) .....                                  | 12        |

| 3.11. 7SEG_LED [ ソケットボード ] ( LED_P1 ) .....                                 | 12        |

| 3.12. LED [ ソケットボード ] .....                                                 | 12        |

| 3.13. スイッチ 1 [ ベースボード ] ( SW1 ) .....                                       | 12        |

| 3.14. スイッチ 2 [ ベースボード ] ( SW2 ) .....                                       | 12        |

| 3.15. スイッチ 3 [ ベースボード ] ( SW3 ) .....                                       | 12        |

| 3.16. ROM 容量切り替えジャンパ [ ベースボード ] ( JP1).....                                 | 13        |

| 3.17. ISA バス・インターフェース切り替えジャンパ [ ベースボード ] ( JP2).....                        | 13        |

| 3.18. LED [ ベースボード ] .....                                                  | 13        |

| 3.19. ROM エミュレータ用テストピン [ ベースボード ] ( JROMEM ) .....                          | 14        |

| 3.20. シリアル・コネクタ [ ベースボード ] ( JSIO1,JSIO2 ) .....                            | 14        |

| 3.21. パラレル・コネクタ [ ベースボード ] ( JPRT ) .....                                   | 15        |

| 3.22. 拡張バス・コネクタ [ ベースボード ] ( JEXT ) .....                                   | 15        |

| 3.23. クロック・ソケット [ ベースボード ] ( OSC1 ) .....                                   | 15        |

| 3.24. DRAM-SIMM ソケット .....                                                  | 16        |

| 3.25. ROM ソケット .....                                                        | 16        |

| <b>4. インストールと使用方法.....</b>                                                  | <b>17</b> |

| 4.1. ボードの設定 .....                                                           | 17        |

| 4.2. ISA バスに実装する場合 .....                                                    | 19        |

| 4.3. ボード単体で使用する場合 .....                                                     | 19        |

| <b>5. ハードウェア・リファレンス.....</b>                                                | <b>20</b> |

| 5.1. メモリ・マップ .....                                                          | 20        |

| <b>6. SYSTEM-IO.....</b>                                                    | <b>22</b> |

|                                                                |           |

|----------------------------------------------------------------|-----------|

| 6.1. SYSTEM-IO 一覧 .....                                        | 22        |

| 6.2. UART/PRINTER ( TL16C552A ) (3F-F000H ~ 3F-F026H).....     | 23        |

| 6.3. TIC ( uPD71054 ) (3F-F030H ~ 3F-F038H) .....              | 25        |

| 6.4. 7 セグメント LED 表示データ出力ポート(3F-F040H [WRITE ONLY]) .....       | 26        |

| 6.5. DIPSW1 読み出しポート(3F-F050H [READ ONLY]).....                 | 26        |

| 6.6. STATUS 読み出しポート(3F-F060H [READ ONLY]).....                 | 27        |

| 6.7. BIC ( BUS-INTERFACE-CONTROL ) (3F-F080H ~ 3F-F0F0H).....  | 28        |

| 6.8. NMI セレクト・ポート(3F-F140H ~ 3F-F150H).....                    | 30        |

| 6.9. NMI ステータス・ポート(3F-F160H ~ 3F-F170H [READ ONLY]) .....      | 30        |

| 6.10. NMI/INT0/INT1 マスク・ポート(3F-F180H).....                     | 31        |

| 6.11. NMI/INT1 要求クリア・ポート(3F-F190H,3F-F1A0H [WRITE ONLY]) ..... | 31        |

| 6.12. INT0(P22/INTP01)セレクト・ポート(3F-F200H).....                  | 31        |

| 6.13. INT1(P24/INTP03)セレクト・ポート(3F-F210H).....                  | 32        |

| 6.14. INT0(P22/INTP01)ステータス・ポート(3F-F220H [READ ONLY]) .....    | 32        |

| 6.15. INT1(P24/INTP03)ステータス・ポート(3F-F230H [READ ONLY]) .....    | 32        |

| <b>7. 推奨設定.....</b>                                            | <b>33</b> |

| 7.1. CPU 設定 .....                                              | 33        |

| 7.2. SRAM/ROM.....                                             | 33        |

| 7.3. DRAM.....                                                 | 33        |

| 7.4. SYSTEM-I/O ウェイト .....                                     | 33        |

| 7.5. SYSTEM-IO コマンド・リカバリ・タイム.....                              | 33        |

| <b>8. JEXT バス仕様.....</b>                                       | <b>34</b> |

| <b>9. その他のCPU 資源.....</b>                                      | <b>36</b> |

| 9.1. RESET- .....                                              | 36        |

| 9.2. NMI- .....                                                | 36        |

| 9.3. マスカブル割り込み(INT0(P22/INTP01),INT1(P24/INTP03)) .....        | 38        |

| 9.4. ポート.....                                                  | 39        |

| <b>10. MULTI モニタ.....</b>                                      | <b>40</b> |

| 10.1. モニタ・ワーク RAM .....                                        | 40        |

| 10.2. 割り込み.....                                                | 40        |

| 10.3. _INIT_SP の設定 .....                                       | 40        |

| 10.4. リモート接続 .....                                             | 40        |

| 10.5. タイマ割り込み .....                                            | 40        |

| <b>11. RTE コマンド.....</b>                                       | <b>41</b> |

| 11.1. HELP(?) .....                                            | 41        |

| 11.2. INIT .....                                               | 41        |

| 11.3. VER .....                                                | 41        |

| 11.4. SFR .....                                                | 41        |

| <b>12. バス・サイクル.....</b>                                        | <b>42</b> |

|                                               |    |

|-----------------------------------------------|----|

| 12.1. タイムオーバ・レディー .....                       | 42 |

| 12.2. DRAM インターフェース .....                     | 42 |

| 12.2.1. 概要 .....                              | 42 |

| 12.2.2. 信号の説明 .....                           | 42 |

| 12.2.3. シングル・リード (ノーマル・モード) .....             | 43 |

| 12.2.4. シングル・ライト (ノーマル・モード) .....             | 44 |

| 12.2.5. ページ・アクセス (ページ・モード、同一 Row アドレス) .....  | 45 |

| 12.2.6. ページ・アクセス (ページ・モード、異なる Row アドレス) ..... | 46 |

| 13. CPU ポート接続 .....                           | 47 |

| 13.1. P00 ~ P07 .....                         | 47 |

| 13.2. P10 ~ P17 .....                         | 47 |

| 13.3. P20 ~ P27 .....                         | 47 |

| 13.4. P30 ~ P37 .....                         | 48 |

| 13.5. P100 ~ P103 .....                       | 48 |

| 14. マスカブル割り込みを使用したアプリケーションの開発 .....           | 49 |

| 14.1. 割り込みベクタ .....                           | 49 |

| 14.2. 一般的な制限事項 / 注意事項 .....                   | 50 |

| 14.3. ブレーク・ポイント使用に関する制限事項 / 注意事項 .....        | 50 |

| 15. ブレーク・ポイント .....                           | 52 |

| 15.1. ブレーク・ポイントの実現方法 .....                    | 52 |

| 15.2. 制限事項 .....                              | 52 |

## 1. はじめに

このマニュアルでは、日本電気社製 CPU の V852 用の評価ボード「RTE-V852-PC」について説明します。RTE-V852-PC では、GreenHills 社の Multi デバッガを利用してプログラムの開発 / デバッグや CPU のパフォーマンス評価などができます。このデバッガとの通信には、IBM-PC/AT の ISA バスか RS-232C シリアル・インターフェースが使用できます。またボードに設けられたローカル・バス用のコネクタやポート用コネクタを使用してメモリや I/O を拡張することもできます。

### 1.1. マニュアル表記について

本書では、数字の表記については表の表記を用います。16 進数や 2 進数の表記では、桁数が多くて読みにくい場合は、4 行ごとに“-”（ハイフン）を入れてあります。

| 進数    | 表記規則           | 例                      |

|-------|----------------|------------------------|

| 10 進数 | 数字のみを示します      | “10”は 10 進数の“10”を示します  |

| 16 進数 | 数字の末尾に”H”を記します | “10H”は 10 進数の“16”を示します |

| 2 進数  | 数字の末尾に”B”を記します | “10B”は 10 進数の“2”を示します  |

数字表記規則

## 2. 特徴と機能

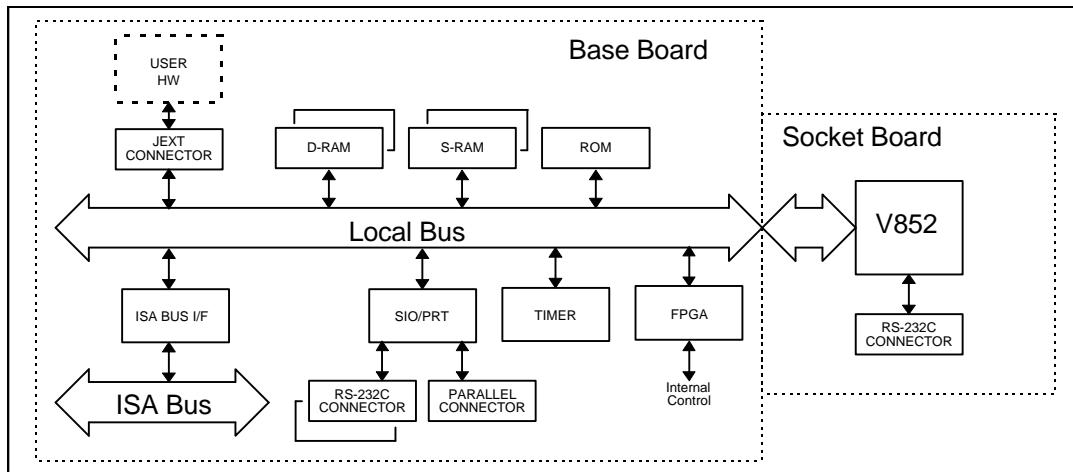

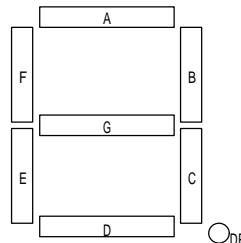

RTE-V852-PC の機能ブロックの概要を図に示します。RTE-V852-PC は、CPU が実装されているソケットボード（小さいボード）と、CPU 以外の資源が実装されソケットボードを実装するベースボードから構成されます。

RTE-V852-PC ブロック図

### 特徴

- ◊ ROM 標準 128K バイト (64K×16 ビット EPROM × 1)

最大 512K バイト (128K×16 ビット EPROM × 1)

- ◊ SRAM 512K バイト (64K×16 ビット SRAM × 4)

- ◊ DRAM SIMM72 ピン・ソケット×1枚により 4M,8M,16M (標準では 4M が実装)

通常タイプの DRAM-SIMM に加え、EDO タイプの DRAM-SIMM も使用可能

- ◊ RS-232C ポート (D-SUB 9 ピン×1、2.54mm ピンヘッダ 10 ピン×2)

- ◊ パラレルポート (2.54mm ピンヘッダ 26 ピン×1)

- ◊ PC/AT 互換機の ISA バスによる通信機能

- ◊ ユーザー拡張用のローカル・バスのコネクタを用意

- ◊ CPU のポートをコネクタに解放

- ◊ 外部リセット・スイッチをリアパネルに用意

- ◊ ROM インサーキット・デバッガ用の接続ピン

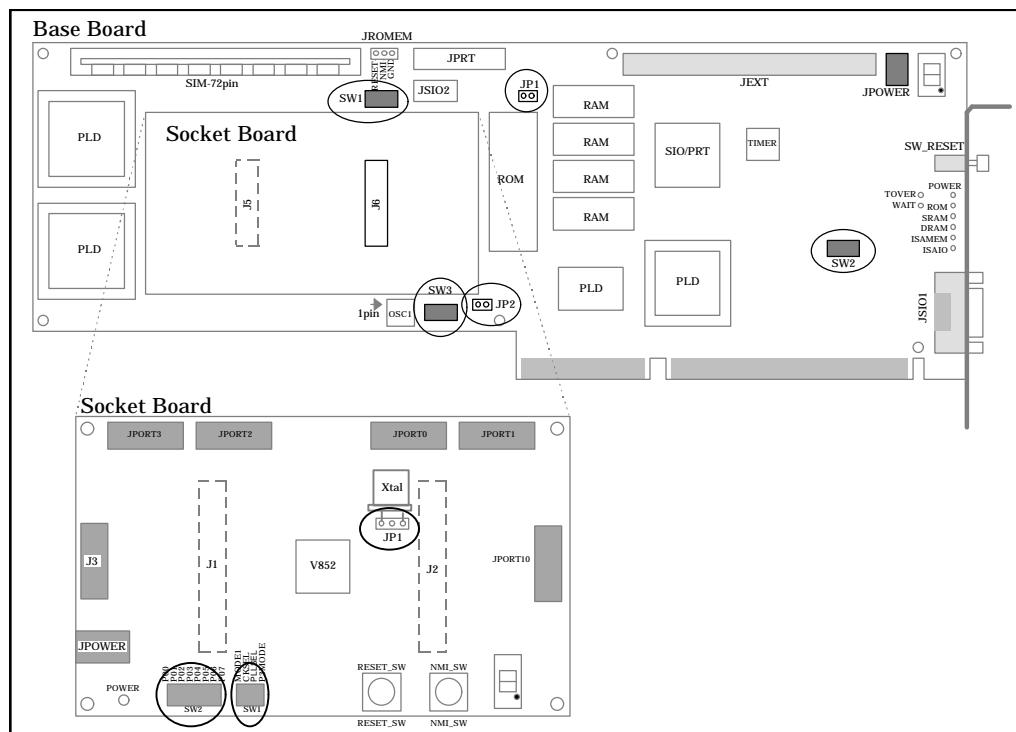

### 3. ボードの構成

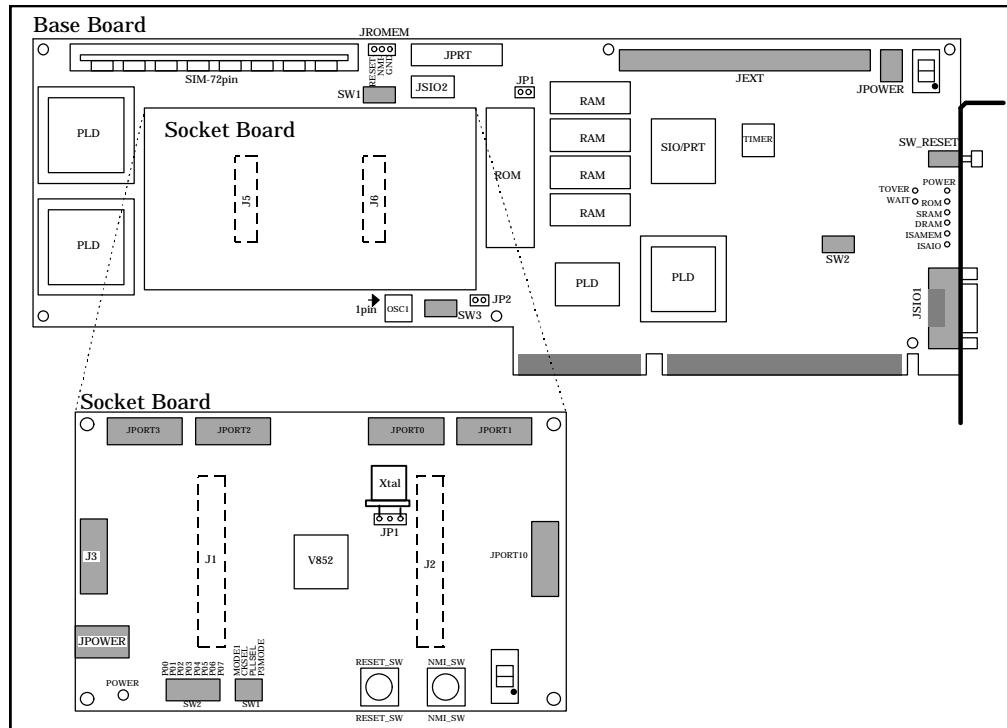

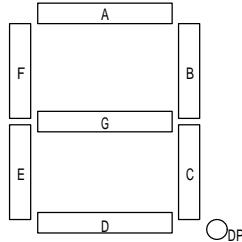

図は RTE-V852-PC ボード上の主要な部品の物理的な配置です。ここでは、それぞれの部品について説明します。取り敢えず Multi でお使いになりたいという場合は、「4インストールと使用方法」を先にご覧ください。

RTE-V852-PC 概觀

### 3.1. リセット・スイッチ[ソケットボード](RESET\_SW)

ソケットボード上の RESET\_SW はリセット・スイッチです。このスイッチを押すと CPU がリセットされます。このリセットはベースボードにも供給されます。ベースボード上のリセット・スイッチと同じ働きをします。

### 3.2. リセット・スイッチ [ベースボード](SW\_RESET)

ベースボード上の SW\_RESET はリセット・スイッチです。このスイッチを押すと CPU がリセットされます。ソケットボード上のスイッチと同じ働きをします。

### 3.3. NMI スイッチ [ ソケットボード ](NMI\_SW)

ベースボード上の NMI\_SW は NMI スイッチです。このスイッチを押すと CPU の NMI 端子が Low レベルになります。NMI はベースボードからも供給され、スイッチによる NMI はベースボードからの NMI と OR されます（「9.2NMI-」参照）。

### 3.4. 電源コネクタ [ ソケットボード / ベースボード ] (JPOWER)

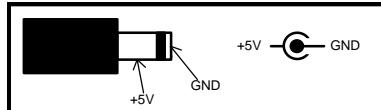

本ボードを ISA バス・スロットに挿さずに単体で使用する場合に、JPOWER コネクタに外部電源を接続して電源を供給します。

ソケットボードとベースボードそれぞれに JPOWER がありますが、ベースボードの JPOWER を使用して下さい。

JPOWER コネクタに供給する電源は、下記の通りです。

電圧：5 V

電流：最大 2 A ( ただし、JEXT コネクタへの供給分を含まず )

適合コネクタ：Type A ( 5.5 )

極性：

**【注意】** 電源コネクタの極性に注意してください。また、ISA バス・スロットに挿して使用する場合には、JPOWER に電源を接続しないでください。

### 3.5. プロセッサ・ピンコネクタ[ソケットボード](JPORT0,JPORT1,JPORT2,JPORT3,JPORT10)

CPU の端子が接続されているコネクタです。ボード内の接続については『13CPU ポート接続』を参照してください。

| J PORT 0<br>ピン番号 | 信号名             | J PORT 0<br>ピン番号 | 信号名             |

|------------------|-----------------|------------------|-----------------|

| 1                | GND             | 2                | GND             |

| 3                | P 07 / INT P 13 | 4                | P 06 / INT P 12 |

| 5                | P 05 / INT P 11 | 6                | P 04 / INT P 10 |

| 7                | P 03 / T I 1    | 8                | P 02 / T CLR 1  |

| 9                | P 01 / T O 11   | 10               | P 00 / T O 10   |

J PORT 0 のピンレイアウト

| J PORT 1<br>ピン番号 | 信号名  | J PORT 1<br>ピン番号 | 信号名  |

|------------------|------|------------------|------|

| 1                | GND  | 2                | GND  |

| 3                | P 17 | 4                | P 16 |

| 5                | P 15 | 6                | P 14 |

| 7                | P 13 | 8                | P 12 |

| 9                | P 11 | 10               | P 10 |

J PORT 1 のピンレイアウト

| J PORT 2<br>ピン番号 | 信号名                | J PORT 2<br>ピン番号 | 信号名                |

|------------------|--------------------|------------------|--------------------|

| 1                | GND                | 2                | GND                |

| 3                | P 27 / SCK 2 -     | 4                | P 26 / SI 2        |

| 5                | P 25 / SO 2        | 6                | P 24 / INT P 0 3*1 |

| 7                | P 23 / INT P 0 2*1 | 8                | P 22 / INT P 0 1*1 |

| 9                | P 21 / INT P 0 0*1 | 10               | NC .               |

J PORT 2 のピンレイアウト

| J PORT 3<br>ピン番号 | 信号名          | J PORT 3<br>ピン番号 | 信号名            |

|------------------|--------------|------------------|----------------|

| 1                | GND          | 2                | GND            |

| 3                | P 37 / SCK 1 | 4                | P 36 / SI 1    |

| 5                | P 35 / SO 1  | 6                | P 34 / RXD     |

| 7                | P 33 / TXD   | 8                | P 32 / SCK 0 - |

| 9                | P 31 / SI 0  | 10               | P 30 / SO 0    |

J PORT 3 のピンレイアウト

| J PORT 10<br>ピン番号 | 信号名              | J PORT 10<br>ピン番号 | 信号名               |

|-------------------|------------------|-------------------|-------------------|

| 1                 | GND              | 2                 | GND               |

| 3                 | NC .             | 4                 | NC .              |

| 5                 | NC .             | 6                 | NC .              |

| 7                 | P 103            | 8                 | P 102             |

| 9                 | P 101 / HLD RQ - | 10                | P 100 / HLD A K - |

J PORT 10 のピンレイアウト

\*1: 「3.15スイッチ3[ベースボード](SW3)」参照

### 3.6. プロセッサ・ピンコネクタ[ソケットボード/ベースボード](J1,J2/J5,J6)

ソケット・ボードとベースボードを接続するためのコネクタです。

| J1 / J5<br>ピン番号 | 信号名            | J1 / J5<br>ピン番号 | 信号名              |

|-----------------|----------------|-----------------|------------------|

| 1               | GND            | 2               | GND              |

| 3               | P57 / AD15     | 4               | P56 / AD14       |

| 5               | P55 / AD13     | 6               | P54 / AD12       |

| 7               | P53 / AD11     | 8               | P52 / AD10       |

| 9               | P51 / AD9      | 10              | P50 / AD8        |

| 11              | GND            | 12              | GND              |

| 13              | P47 / AD7      | 14              | P46 / AD6        |

| 15              | P45 / AD5      | 16              | P44 / AD4        |

| 17              | P43 / AD3      | 18              | P42 / AD2        |

| 19              | P41 / AD1      | 20              | P40 / AD0        |

| 21              | P22 / INTPO1   | 22              | P21 / INTPO0     |

| 23              | RTE_CON - (IN) | 24              | 1M / 16M - (OUT) |

| 25              | +5V (IN)       | 26              | +5V (IN)         |

J1 / J5 のピンレイアウト

| J2 / J6<br>ピン番号 | 信号名              | J2 / J6<br>ピン番号 | 信号名            |

|-----------------|------------------|-----------------|----------------|

| 1               | GND              | 2               | GND            |

| 3               | GND (A23)        | 4               | GND (A22)      |

| 5               | GND (A21)        | 6               | GND (A20)      |

| 7               | P63 (A19)        | 8               | P62 (A18)      |

| 9               | P61 (A17)        | 10              | P60 (A16)      |

| 11              | GND              | 12              | GND            |

| 13              | CLKOUT           | 14              | X1 (IN)        |

| 15              | RESET - (IN/OUT) | 16              | WAIT -         |

| 17              | NMI              | 18              | P96 / HLD RQ - |

| 19              | P95 / HLD A K -  | 20              | P94 / AST B    |

| 21              | P93 / DST B -    | 22              | P92 / R_W -    |

| 23              | P91 / UBE N -    | 24              | P90 / LB E N - |

| 25              | P24 / INTPO3     | 26              | P23 / INTPO2   |

J2 / J6 のピンレイアウト

### 3.7. シリアル・コネクタ[ソケットボード](J3)

J3 コネクタは、CPU の内蔵 UART によって制御される RS-232C 用のコネクタです。コネクタの形状は、2.54mm ピッチのピンヘッダですが、リボンケーブルに対して圧接型コネクタを使用した場合、ピン配置が PC/AT で用いられる一般的な D-SUB9 ピンの RS-232C コネクタと同じになっています。全ての信号は RS-232C レベルに変換されています。

J3 コネクタのピン配置を図と表に示します。また、パーソナル・コンピュータ(ホスト)などと接続する場合の布線は、「3.20シリアル・コネクタ[ベースボード](JSIO1,JSIO2)」の表を参照して下さい。

J7 ピン配置

| J3<br>ピン番号 | 信号名       | 入出力 | 対応<br>ポート |

|------------|-----------|-----|-----------|

| 1          | NC        | 入力  |           |

| 3          | RxD(RD)   | 入力  | P34       |

| 5          | TxD(SD)   | 出力  | P33       |

| 7          | DTR(DR)*1 | 出力  | --        |

| 9          | GND       |     |           |

| 2          | DSR(ER)   | 入力  | P37       |

| 4          | RTS(RS)   | 出力  | P35       |

| 6          | CTS(CS)   | 入力  | P36       |

| 8          | NC        |     |           |

| 10         | NC        |     |           |

J7 コネクタ信号

\*1:DTR は、電源が入ることによって、アクティブレベルを出力します。

### 3.8. スイッチ1 [ソケットボード](SW1)

ソケットボードの SW1 は、モードを設定するためのスイッチです。

| SW1 番号 | 1     | 2     | 3      | 4      |

|--------|-------|-------|--------|--------|

| ポート    | MODE1 | CKSEL | PLLSEL | P3MODE |

SW1 ポート対応

MODE1 :V852 の動作モードを指定するスイッチです。

OFF : シングルチップモード

ON : ROM レスモード (出荷時の設定)

CKSEL :V852 の CKSEL のレベルを指定するスイッチです。

OFF : ダイレクト・モード

ON : PLL モード (出荷時の設定)

PLLSEL :V852 の PLLSEL のレベルを指定するスイッチです。

OFF : 5 適倍 (出荷時の設定)

ON : 1 適倍

P3MODE :V852 の P3 の使用するモードを指定するスイッチです。

OFF : P34,P36,P37 を JPORT3 へ接続します。 (出荷時の設定)

ON : P34,P36,P37 を J3(RS232C) に接続します。

### 3.9. スイッチ2 [ソケットボード](SW2)

ソケットボードの SW2 は、CPU の Port0 に接続されており、ユーザが自由に使用する事が出来ます。スイッチは、OFF で 1、ON で 0 の値となります。

**【注意】 P0 端子を他の目的で使用する場合は、全てを OFF に設定して下さい。**

| SW2 番号 | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| ポート    | P00 | P01 | P02 | P03 | P04 | P05 | P06 | P07 |

SW2 ポート対応

### 3.10. クリスタル・ソケット[ソケットボード](JP1)

JP1 は、CPU に供給するクロックの切り替え役割と、クリスタルの実装用ソケットの役割を持っています。

#### ベースボード上の OSC1 のソケットにオシレータを実装して使用する場合

JP1 の 1 ピンと 2 ピンをショートします。JP1 にクリスタルは実装しないで下さい。

#### JP1 にクリスタルを実装して使用する場合

1 ピンと 3 ピンの間にクリスタルを実装します。1 ピンと 2 ピンはショートしないで下さい。

### 3.11. 7Seg\_LED [ソケットボード](LED\_P1)

LED\_P1 は 7 セグメント LED であり、CPU のポートの P1 が下表の様に接続されています。該当するビットを 1 に設定すると、対応するセグメントが点灯します。

| セグメント | A   | B   | C   | D   | E   | F   | G   | D.P. |

|-------|-----|-----|-----|-----|-----|-----|-----|------|

| ポート   | P10 | P11 | P12 | P13 | P14 | P15 | P16 | P17  |

LED\_P11 対応

### 3.12. LED [ソケットボード]

ソケットボード上の LED の内容を下表に示します。

| 名称        | 内容                 |

|-----------|--------------------|

| LED_POWER | ボードに電源が供給されている時に点灯 |

LED ステータス

### 3.13. スイッチ1 [ベースボード](SW1)

SW1 は、汎用の入力ポートに接続したソフトウェアで読み出す為のスイッチです。スイッチは、OFF で 1、ON で 0 の値となります。詳細は、「4.1 ボードの設定」および「6.5 DIPSW1 読み出しポート(3F-F050H [Read Only])」を参照してください。

### 3.14. スイッチ2 [ベースボード](SW2)

SW2 は、ISA バスの I/O アドレス選択のスイッチです。スイッチの番号 1 ~ 8 が ISA バスのアドレス A4 ~ A11 に対応しています (A12 ~ A15 は 0 固定)。したがって、I/O アドレスとして 000xH ~ 0FFxH が選択できます。スイッチは、OFF で 1、ON で 0 の値となります (「4.1 ボードの設定」参照)。

| SW2 番号 | 1  | 2  | 3  | 4  | 5  | 6  | 7   | 8   |

|--------|----|----|----|----|----|----|-----|-----|

| アドレス   | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 |

SW2 アドレス対応

### 3.15. スイッチ3 [ベースボード](SW3)

SW3 は、ベースボードの割り込み要因を CPU へ接続するかどうかを選択するスイッチです。スイッチ番号と CPU の割り込み端子と割り込みの関係を表に示します。スイッチは、OFF で未接続、

ON で接続となります。

また、下表の CPU 端子名と同じ端子名の信号を JPORT2 コネクタ経由で使用する場合は、SW3 の該当するスイッチを OFF にしなければなりません。(13.3参照)

通常は全て OFF に設定します。下表の INT0SEL および INT1SEL については、「9.3マスカブル割り込み(INT0(P22/INTP01),INT1(P24/INTP03))」を参照してください。

| SW3 番号 | CPU 端子名    | J5/J6 ピン番号 | 割り込み要因                                                |

|--------|------------|------------|-------------------------------------------------------|

| 1      | P21/INTP00 | J5-22Pin   | ベースボード上の TL16C552A の UART2(SCC2)の割り込み要求。High で割り込み発生。 |

| 2      | P22/INTP01 | J5-21Pin   | INT0SEL で選択されたベースボード上の割り込み要求。High で割り込み発生。            |

| 3      | P23/INTP02 | J6-26Pin   | JEXT パスの割り込み要求信号(INT-) の反転信号。High で割り込み発生。            |

| 4      | P24/INTP03 | J6-25Pin   | INT1SEL で選択されたベースボード上の割り込み要求。High で割り込み発生。            |

SW3 割り込み対応

### 3.16. ROM 容量切り替えジャンパ[ ベースボード ](JP1)

JP1 は実装する ROM の容量によって切り替えるジャンパです。128K バイト (64K × 16 ビット) と 256K バイト (128K × 16 ビット) の ROM を実装する場合はオープンにしておきます。512K バイト (256K × 16 ビット) の ROM を実装する場合はショートします。

### 3.17. ISA バス・インターフェース切り替えジャンパ[ ベースボード ](JP2)

JP2 は ISA バスへのインターフェースのモードを切り替えるためのジャンパです。通常はオープン状態で用います。

### 3.18. LED [ ベースボード ]

LED は、各種ステータスを示しています。表に内容を示します。

| 名称     | 内容                                                                                |

|--------|-----------------------------------------------------------------------------------|

| POWER  | ボードに電源が供給されている時に点灯                                                                |

| ROM    | ROM 領域が選択されている時に点灯                                                                |

| SRAM   | SRAM 領域が選択されている時に点灯                                                               |

| DRAM   | DRAM 領域が選択されている時に点灯                                                               |

| TOVER  | タイムオーバー・レディー発生時に点灯、ソフト的にタイムオーバー・レディー割り込みがクリアされるまで点灯し続ける<br>(「12.1タイムオーバー・レディー」参照) |

| WAIT   | 拡張外部バスのサイクルが発生し Wait サイクルが発生すると点灯、明るさは Wait サイクルの頻度に対応                            |

| ISAMEM | ISA のメモリ領域が選択されている時に点灯                                                            |

| ISAIO  | ISA の I/O 領域が選択されている時に点灯                                                          |

LED ステータス

### 3.19. ROM エミュレータ用テストピン[ベースボード](JROMEM)

JROMEM は、ROM インサーキット型のデバッガを接続する際に使用するテストピンです。ROM インサーキット・デバッガからの制御信号が入力できます。下表に信号名と機能を示します。

| 信号名    | 入出力   | 機能                                                                                                       |

|--------|-------|----------------------------------------------------------------------------------------------------------|

| RESET- | 入力    | ROM インサーキット・デバッガからのリセット要求信号を接続。Low レベル入力により、CPU がリセットされます。本ボード内で 1K ブルアップされています。                         |

| NMI-   | 入力    | ROM インサーキット・デバッガからの NMI 要求信号(ブレーク要求)を接続。Low レベル入力により、CPU に NMI が入ります。本ボード内で 1K ブルアップされています。(「9.2NMI-」参照) |

| GND    | - - - | ROM インサーキット・デバッガの GND と接続。GND です。                                                                        |

TP 端子の機能

### 3.20. シリアル・コネクタ[ベースボード](JSIO1,JSIO2)

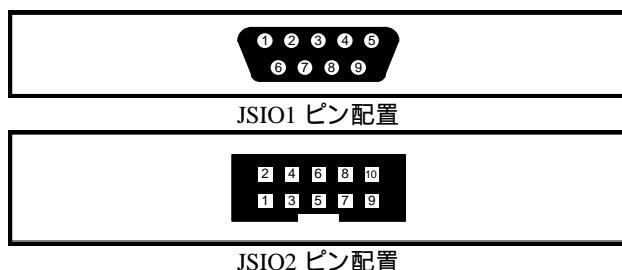

JSIO1,JSIO2 コネクタは、シリアル・コントローラ(TL16C552A)によって制御される RS-232C 用のコネクタです。コネクタの形状は、JSIO1 は PC/AT で用いられる一般的な D-SUB9 ピンの RS-232C コネクタ、JSIO2 は 2.54mm ピッチのピンヘッダ型コネクタです。何れも、全ての信号は RS-232C レベルに変換されています。コネクタのピン番号と内容は図と表の通りです。

表には、ホストと接続する場合の接続信号について、ホスト側が D-SUB9 ピンの場合と D-SUB25 ピンの場合の布線をそれぞれ示してあります(一般的なクロスケーブルの布線です)。

また JSIO2 のピン配置は、リボンケーブルに対して圧接型コネクタを使用した場合、JSIO1 のピン配置と同じになる様になっています。

| JSIO1<br>ピン番号 | JSIO2<br>ピン番号 | 信号名     | 入出力 | ホストの接続ピン番号 |         |

|---------------|---------------|---------|-----|------------|---------|

|               |               |         |     | D-SUB9     | D-SUB25 |

| 1             | 1             | DCD     | 入力  |            |         |

| 2             | 3             | RxD(RD) | 入力  | 3          | 2       |

| 3             | 5             | TxD(SD) | 出力  | 2          | 3       |

| 4             | 7             | DTR(DR) | 出力  | 1, 6       | 6, 8    |

| 5             | 9             | GND     |     | 5          | 7       |

| 6             | 2             | DSR(ER) | 入力  | 4          | 20      |

| 7             | 4             | RTS(RS) | 出力  | 8          | 5       |

| 8             | 6             | CTS(CS) | 入力  | 7          | 4       |

| 9             | 8             | RI      | 入力  |            |         |

| --            | 10            | NC      |     |            |         |

JSIO1,2 コネクタ信号

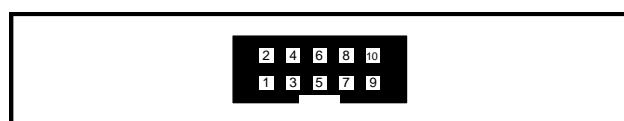

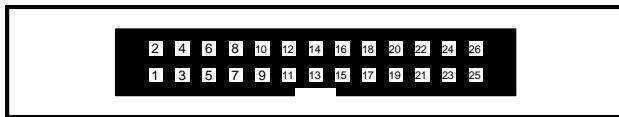

### 3.21. パラレル・コネクタ [ベースボード](JPRT)

JPRT コネクタは、パラレル(プリンタ)・コントローラ(TL16C552A)によって制御されるパラレル用のコネクタです。コネクタの形状は、2.54mm ピッチのピンヘッダ型コネクタです。何れも、全ての信号は 5V レベルです。コネクタのピン番号と内容は図と表の通りです。

また JPRT のピン配置は、リボンケーブルに対して圧接型コネクタを使用した場合、PC/AT で用いられている一般的な D-SUB25 ピンのピン配置と同じになる様になっています。

JPRT ピン配置

| JPRT<br>ピン番号 | 信号名    | JPRT<br>ピン番号 | 信号名        |

|--------------|--------|--------------|------------|

| 1            | STB-   | 2            | AUTO_FD-   |

| 3            | D0     | 4            | ERROR-     |

| 5            | D1     | 6            | INIT-      |

| 7            | D2     | 8            | SELECT_IN- |

| 9            | D3     | 10           | GND        |

| 11           | D4     | 12           | GND        |

| 13           | D5     | 14           | GND        |

| 15           | D6     | 16           | GND        |

| 17           | D7     | 18           | GND        |

| 19           | ACK-   | 20           | GND        |

| 21           | BUSY   | 22           | GND        |

| 23           | PE     | 24           | GND        |

| 25           | SELECT | 26           | NC         |

JPRT コネクタ信号

### 3.22. 拡張バス・コネクタ [ベースボード](JEXT)

JEXT コネクタは、メモリや I/Oなどを拡張できるように用意されたコネクタです。このコネクタには、本ボードの内部のローカル・バスが接続されています。このコネクタの詳細については「8JEXT バス仕様」を参照して下さい。

### 3.23. クロック・ソケット [ベースボード](OSC1)

OSC1 ソケットには、CPU に供給するクロックのためにオシレータを実装します。出荷時の設定では、システム・クロックの生成に PLL を使用しており、OSC1 ソケットに実装するオシレータの周波数の 5 倍が CPU のクロックになります。

CPU への供給クロックは、ソケットボード上の JP1 によって、JP1 上に実装したクリスタルを使用する事も出来ます(「3.10クリスタル・ソケット [ソケットボード](JP1)」参照)。

OSC1 ソケットには、DIP8 ピンタイプ(ハーフタイプ)のオシレータを実装してください。

**【注意】** OSC1 を使用する場合、ソケットボードの JP1 は、**[1-2]** ショートに設定して下さい。

### 3.24. DRAM-SIMM ソケット

DRAM-SIMM ソケットには、標準で 4M バイト SIMM 実装されています。このソケットには 4M, 8M バイトの 72 ピン SIMM ( DOS/V 機用 ) が実装できます。また、通常タイプの DRAM-SIMM に加え、EDO タイプの DRAM-SIMM を使用する事が可能です。「7.3DRAM」を参照し、タイミング上満足するアクセスタイムのものをご使用ください。また、実装されている SIMM の容量は PIO ポートから読み出すことができます（「6.6Status 読み出しポート(3F-F060H [Read Only])」参照）。

### 3.25. ROM ソケット

ROM ソケットには、標準で 128K バイト (  $64K \times 16$  ビット ) の 40 ピン ROM が実装されています。もし、変更する場合で Multi を使用する場合は、アクセス・タイムが 150ns 以下のものをご使用ください。異なる容量の ROM を実装する場合は、ベースボード上の JP1 の切り替えが必要な場合があります（「3.16ROM 容量切り替えジャンパ [ ベースボード ] (JP1)」参照）。

#### 4. インストールと使用方法

ボードのインストールは、PC/AT 互換機（以下 PC）の ISA バス・スロットに組み込んで使用することを想定していますが、外部電源を用意して単体で使用することもできます。また、動作確認のテストや Multi デバッガを使用する場合には、PC に通信用のソフトウェア（RTE for Windows）をインストールする必要があります。ソフトウェアのインストールとテストについては、「RTE for Windows インストール・マニュアル」を参照してください。

##### 4.1. ボードの設定

ボードには、いくつかの設定用ディップ・スイッチが設けられています。スイッチの箇所を図に示します。

ボードのスイッチ

ベースボード上の SW1 は、汎用の入力ポートのスイッチです。実装されている ROM の Multi 用モニタでは、RS-232C のボーレートとプロファイラのタイマ周期の設定に使用しています。

| SW1 番号 | 1   | 2   | ボーレート              |

|--------|-----|-----|--------------------|

| 設定     | ON  | ON  | 未使用                |

|        | OFF | ON  | 38400 baud         |

|        | ON  | OFF | 19200 baud         |

|        | OFF | OFF | 9600 baud (出荷時の設定) |

ボーレートの設定

| SW1 番号 | 3   | 4   | プロファイラ周期               |

|--------|-----|-----|------------------------|

| 設定     | ON  | ON  | タイマを使用しない <sup>1</sup> |

|        | OFF | ON  | 200 Hz 5ms             |

|        | ON  | OFF | 100 Hz 10ms            |

|        | OFF | OFF | 60 Hz 16.67ms (出荷時の設定) |

<sup>1</sup>:Multi を使用する場合は設定しないでください(「10.5タイマ割り込み」参照)

#### プロファイラ周期の設定

ベースボード上の SW1 の 5~8 は、Multi モニタでは使用していません(出荷時 OFF)。

ベースボード上の SW2 は、ISA バスの I/O アドレス選択のスイッチです。スイッチの番号 1~8 が ISA バスのアドレス A4~A11 に対応しています(A12~A15 は 0 固定)。したがって、I/O アドレスとして 000xH~0FFxH が選択できます。なおスイッチは、OFF で "1"、ON で "0" の値となります。一般的には、20xH~3FxH の間で設定します。

| SW2 番号     | 1  | 2  | 3  | 4  | 5  | 6  | 7   | 8   |                   |

|------------|----|----|----|----|----|----|-----|-----|-------------------|

| アドレス       | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | I/O アドレス          |

| ON/<br>OFF | 0  | 0  | 0  | 0  | 0  | 1  | 0   | 0   | 020xH<br>(出荷時の設定) |

#### I/O アドレスの対応

ベースボード上の SW3 は、ベースボード上の割り込み要求線を CPU の端子に接続する場合に ON にします。通常は 1~4 全て OFF に設定します(「3.15スイッチ 3 [ベースボード](SW3)」参照)。

ベースボード上の JP1 および JP2 は、どちらもオープン状態で使用します。出荷時と異なる容量の ROM を実装する場合は JP1 の切り替えが必用になる場合があります(「3.16ROM 容量切り替えジャンパ [ベースボード](JP1)」および「3.17ISA バス・インターフェース切り替えジャンパ [ベースボード](JP2)」参照)。

ソケットボード上の SW1 は CPU のモードの選択と、CPU の Port2 の接続を選択するスイッチです(「3.8スイッチ 1 [ソケットボード](SW1)」参照)。デフォルトの設定を下記に示します。

| SW1-1 | 設定内容                                               |

|-------|----------------------------------------------------|

| ON    | V852 の動作モードを ROM レスに設定します。<br>(内蔵 ROM 無効、外部拡張バス有効) |

| SW1-2 | 設定内容                                               |

| ON    | ( CKSEL = Low )                                    |

| SW1-3 | 設定内容                                               |

| OFF   | ( PLLSEL = High )                                  |

| SW1-4 | 設定内容                                               |

| OFF   | ( P34,P36,P37 を JPORT2 へ接続します )                    |

ソケットボード上の SW2 は、Port0 へ与える信号レベルを選択します。ユーザが自由に使用できます。出荷時の設定は全て OFF です（「3.9スイッチ 2 [ ソケットボード ]( SW2 )」参照）。

ソケットボード上の JP1 は、CPU に与えるクロックを決めます。6.6MHz のクリスタルを JP1 へ実装します。クロックを切り替えたい場合は、「3.10クリスタル・ソケット [ ソケットボード ] ( JP1 )」を参照してください。

#### 4.2. ISA バスに実装する場合

ボードを PC の ISA バス・スロットに実装すると、ISA バスからボードへ電源 (+5V) が供給されます。また、デバッガとの通信に ISA バス経由が使用できるため、プログラムの高速なダウンロードが実現できます。

##### ISA バス・スロットへの実装は、以下の手順となります。

ボード上のディップ・スイッチにより、PC の I/O アドレスを設定します。I/O アドレスは他の I/O と重ならないように注意してください。スイッチの設定については「4.1ボードの設定」を参照ください。

PC の電源を切って筐体をあけ、ボードを実装する ISA バス・スロットを確認します。実装するスロットにリアパネルが付いている場合は、そのリアパネルを外します。

ボードを ISA バス・スロットに差し込み、ボードが隣接の他のボードなどと接触していないかを確認し、ボードに付いているリアパネルを PC の筐体にネジで固定します。

PC の電源を入れ、ボードの POWER-LED が点灯することを確認します。LED が点灯しない場合は、すぐに PC の電源を切り接続を確認してください。システムが正常に立ち上がらない（デバイス・ドライバの組み込みでエラーが発生するなど）場合は、設定した I/O アドレスが他の I/O と重なっている可能性があります。PC のマニュアルや他に実装されているボードのマニュアルなどを参照して、ボードの I/O アドレスを再確認してください。

システムが正常と判断できたら、再度 PC の電源を切ってから筐体を元に戻します。

#### 4.3. ボード単体で使用する場合

PC に組み込みず、ボード単体で使用する場合は、外部からの電源供給が必要となります。また、デバッガとの通信も RS-232C 経由のみとなります。PC/AT 互換機以外のホスト・デバッガを使用する場合や、ハードウェアの確認や拡張を目的とする場合に便利です。

##### ボードを単体で使用する場合の手順は以下の通りです。

ホストと接続するための RS-232C ケーブルと、電源供給のための外部電源 (+5V 2A) を用意してください。特に電源については、電圧とコネクタの極性に注意してください。また、ボードの 4 隅にスペーサを取り付けるなど、設置場所にも問題がないようにしてください。RS-232C ケーブルの結線は「3.20シリアル・コネクタ [ ベースボード ]( JSIO1,JSIO2 )」、電源コネクタについては、「3.4電源コネクタ [ ソケットボード / ベースボード ]( JPOWER )」を参照してください。

ボード上のディップ・スイッチで、RS-232C のボーレートを設定します。スイッチの設定については「4.1ボードの設定」を参照ください。

ホストと RS-232C ケーブルで接続して、JPOWER コネクタに電源を接続し、ボードの POWER-LED が点灯することを確認します。LED が点灯しない場合は、すぐに電源を切り接続を確認してください。

## 5. ハードウェア・リファレンス

ここでは、RTE-V852-PC ボードのハードウェアについて記述します。

### 5.1. メモリ・マップ

ボードのメモリ割り付けは、以下の通りです。

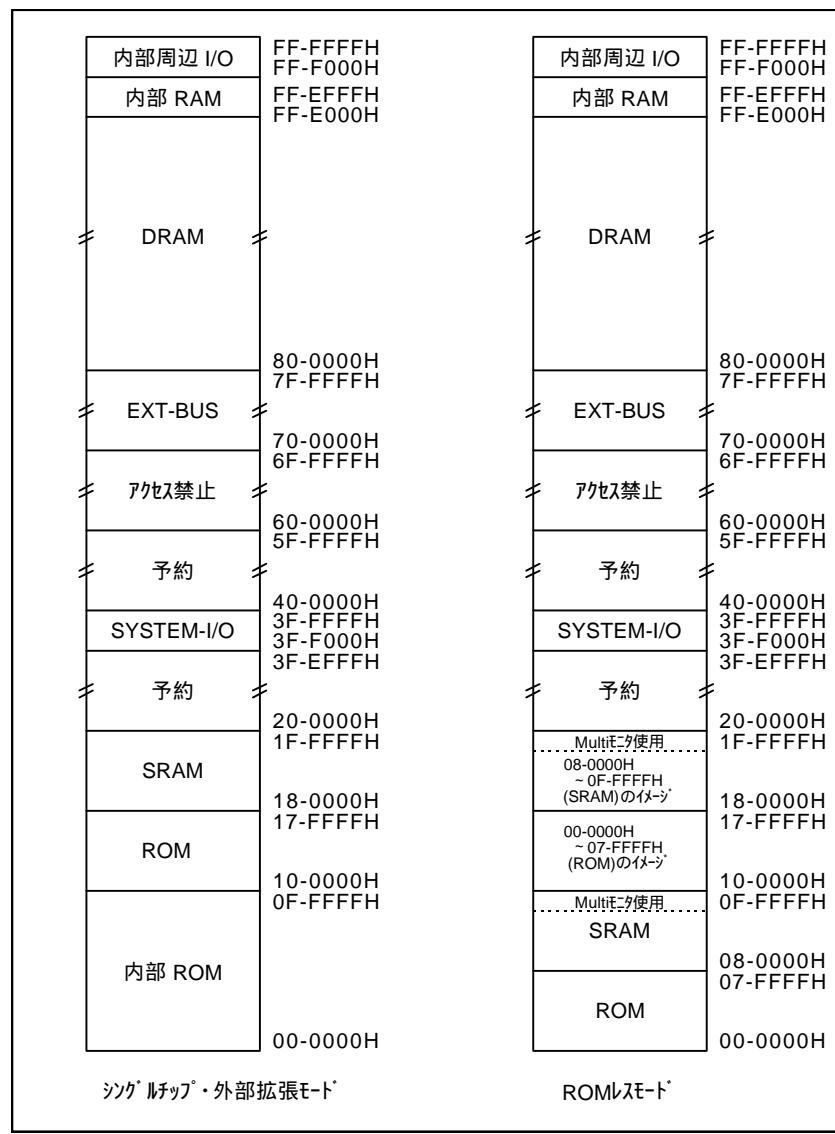

V852 は CPU に内蔵した内部資源があるため、内部資源がある領域では外部資源ではなく内部資源が見えます。具体的には下図に示す様に、00-0000H ~ 0F-FFFFH には内部 ROM (CPU がシングルチップ・モードの時のみ) が、FF-E000H ~ FF-EFFFH には内部 RAM が、FF-F000H ~ FF-FFFFH には内部周辺 I/O が見えます。

メモリ・マップ

#### ROM 空間 (00-0000H ~ 07-FFFFH, 10-0000H ~ 17-FFFFH)

ベースボード上に実装された ROM で 512K バイトの空間があります。標準では 256K バイト、アクセス・タイム 150ns 以下の ROM が実装されています。ROM は ready 信号制御によりアクセス

ス・サイクルにウェイトを挿入する事が可能で、ウェイト数は SYSMTEM-I/O で設定する事が出来ます（「6.7BIC ( Bus-Interface-Control ) (3F-F080H ~ 3F-F0F0H)」参照）。必用ウェイト数は「7.2SRAM/ROM」を参照して下さい。

実装されている ROM には、標準で Multi 用のモニタが組み込まれています。

#### SRAM 空間 (08-0000H ~0F-FFFFH,18-0000H ~1F-FFFFH)

ボード上に実装された SRAM で 512K バイトの空間があります。ウェイトの設定が可能で、ウェイト数は SYSMTEM-I/O で設定する事が出来ます（「6.7BIC ( Bus-Interface-Control ) (3F-F080H ~ 3F-F0F0H)」参照）。必用ウェイト数は「7.2SRAM/ROM」を参照して下さい。

#### 予約及びアクセス禁止空間

この空間へのアクセスは行なわないでください。

#### SYSTEM-I/O 空間 (3F-F000H ~3F-FFFFH)

ベースボード上の各機能を制御するための I/O デバイスが割り付けられている空間です。これらは、メモリ・マップド I/O となっています。詳細については「6.SYSTEM-IO」を参照してください。

#### EXT-BUS 空間 (70-0000 ~7F-FFFFH)

ボード上の JEXT コネクタに接続するハードウェア拡張ボードのための空間です。EXT-BUSについての詳細は「8.JEXT」を参照してください。

#### DRAM 空間 (80-0000H ~FF-FFFFH)

ベースボードに実装する 72 ピンの SIMM の空間です。4M,8M または 16M バイトの SIMM メモリを実装でき、EDO-DRAM の SIMM も実装する事が可能です。RAS,CAS,プリチャージ幅の設定が可能です（「6.7BIC ( Bus-Interface-Control ) (3F-F080H ~ 3F-F0F0H)」参照）。実装されている SIMM の種類は Status ポートの PD[1..4]により知る事が出来ます（「6.6Status 読み出しポート(3F-F060H [Read Only])」参照）。

## 6. SYSTEM-IO

SYSTEM-IO は、メモリ空間にマップされた I/O デバイスで UART/PRINTER, TIC, PIO, ISA バス・インターフェースなどがあります (ISA バス・インターフェースについては、説明を省略します)。

### 6.1. SYSTEM-IO 一覧

SYSTEM-IO の一覧を下記の表に示します。

| アドレス                | 機能                             | 備考         |

|---------------------|--------------------------------|------------|

| 3F-F000H ~ 3F-F00EH | UART-CH#1(TL16C552A)設定 / 参照    | リカバリタイムが必用 |

| 3F-F010H ~ 3F-F01EH | UART-CH#2(TL16C552A)設定 / 参照    | リカバリタイムが必用 |

| 3F-F020H ~ 3F-F026H | PRINTER(TL16C552A)設定 / 参照      | リカバリタイムが必用 |

| 3F-F030H ~ 3F-F036H | タイマコントローラ(uPD71054)設定 / 参照     | リカバリタイムが必用 |

| 3F-F040H            | ベースボード 7 セグメント LED 表示データ設定     |            |

| 3F-F050H            | ベースボード DIPSW1 参照               |            |

| 3F-F060H            | ステータス参照(DRAM-PD,Tover-flg,etc) |            |

| 3F-F080H            | SRAM ウェイト設定 / 参照               |            |

| 3F-F0A0H            | DRAM プリチャージ時間設定 / 参照           |            |

| 3F-F0B0H            | DRAM RAS 幅設定 / 参照              |            |

| 3F-F0C0H            | DRAM Read-Cycle CAS 幅設定 / 参照   |            |

| 3F-F0D0H            | DRAM Page-Mode 設定 / 参照         |            |

| 3F-F0E0H            | SYSTEM-IO ウェイト設定 / 参照          |            |

| 3F-F0F0H            | ROM ウェイト設定 / 参照                |            |

| 3F-F100H            | -----                          | 予約         |

| 3F-F110H            | -----                          | 予約         |

| 3F-F140H ~ 3F-F150H | NMI セレクト設定 / 参照                |            |

| 3F-F160H ~ 3F-F170H | NMI ステータス参照                    |            |

| 3F-F180H            | NMI,INT0,INT1 マスク設定 / 参照       |            |

| 3F-F190H            | タイムオーバ・レディー・フラグ・クリア            |            |

| 3F-F1A0H            | uPD71054 TOUT0 割り込み要求クリア       |            |

| 3F-F200H            | INT0 セレクト設定 / 参照               |            |

| 3F-F210H            | INT1 セレクト設定 / 参照               |            |

| 3F-F220H            | INT0 ステータス参照                   |            |

| 3F-F220H            | INT1 ステータス参照                   |            |

## 6.2. UART/PRINTER (TL16C552A) (3F-F000H ~ 3F-F026H)

UART/PRINTER として TEXAS INSTRUMENTS 製の TL16C552A(DUAL ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH FIFO)LSIを使用しています。TL16C552A は、UART を 2 チャンネル、双方向プリンタ・ボードを 1 チャンネル備えており、UART の受信部には 16 キャラクタ分の FIFO バッファを内蔵しているため受信時のオーバーラン・エラーの可能性を最小限に押さえられます。

TL16C552A はの各レジスタは、表のように割り付けられています。各レジスタの機能については、TL16C552A のマニュアルを参照してください。

| アドレス     | 機能        | 読み出し         | 書き込み          |

|----------|-----------|--------------|---------------|

| 3F-F000H | UART-CH#1 | RBR/DLL      | THR/DLL       |

| 3F-F002H |           | IER/DLM      | IER/DLM       |

| 3F-F004H |           | IIR          | FCR           |

| 3F-F006H |           | LCR          | LCR           |

| 3F-F008H |           | MCR          | MCR           |

| 3F-F00AH |           | LSR          | LSR           |

| 3F-F00CH |           | MSR          | MSR           |

| 3F-F00EH |           | SCR          | SCR           |

| 3F-F010H | UART-CH#2 | RBR/DLL      | THR/DLL       |

| 3F-F012H |           | IER/DLM      | IER/DLM       |

| 3F-F014H |           | IIR          | FCR           |

| 3F-F016H |           | LCR          | LCR           |

| 3F-F018H |           | MCR          | MCR           |

| 3F-F01AH |           | LSR          | LSR           |

| 3F-F01CH |           | MSR          | MSR           |

| 3F-F01EH |           | SCR          | SCR           |

| 3F-F020H | PRINTER   | Read-data    | Write-data    |

| 3F-F022H |           | Read-status  | -----         |

| 3F-F024H |           | Read-control | Write-control |

| 3F-F026H |           | -----        | -----         |

TL16C552A レジスタ配置

TL16C552A の CLK 入力には 16MHz のクロックが接続されています。

TL16C552A のアクセスには 80nS の RD-/WR-のパルス幅が必要になります。 したがって、これを満足する様に wait を入れなければなりません。wait の設定値については「7.4SYSTEM-I/O ウェイト」を、設定場所については「6.7BIC ( Bus-Interface-Control ) (3F-F080H ~ 3F-F0F0H)」を参照してください。

また、TL16C552A はコマンド・リカバリ・タイムとして 80ns 必要とします。 リカバリ・タイムについては「7.5SYSTEM-IO コマンド・リカバリ・タイム」を参照してください。

UART-CH#1、UART-CH#2、PRINTER の各割り込みは下表の様に CPU の割り込みに接続することができます。

| 割り込み発生元   | 接続 CPU 割り込み       |

|-----------|-------------------|

| UART-CH#1 | NMI- , P22/INTP01 |

| UART-CH#2 | NMI- , P21/INTP00 |

| PRINTER   | NMI- , P22/INTP01 |

マスカブル割り込みはディップ・スイッチの SW3 を経由しています。NMI-については「9.2NMI-」を、マスカブル割り込みについては「9.3マスカブル割り込み」を参照してください。

UART-CH#1 はベースボードのリアパネルにある JSIO0 コネクタに、UART-CH#2 は JSIO2 コネクタ、PRINTER は JPRT に接続しています。また、UART-CH#1 は Multi をシリアル通信で用いる場合に使用されます。

TL16C552A は、システム・リセットによってリセットされます（「9.1RESET-」参照）。

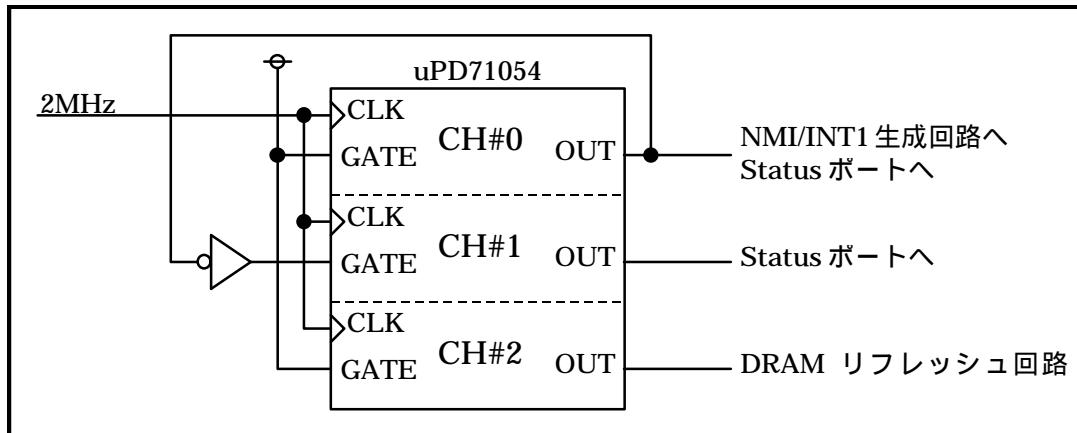

### 6.3. TIC (uPD71054) (3F-F030H ~ 3F-F038H)

TIC は NEC 製の uPD71054 が実装されています。uPD71054 は Intel 製の i8254 と互換であり、3 つのタイマ / カウンタを持っています。これらのタイマ / カウンタにより、DRAM のリフレッシュ・タイミングの生成、モニタのタイマ割り込みの生成を行っています。

TIC の各レジスタは、表の通りに割り当てられています。

| アドレス     | 読み出し      | 書き込み         |

|----------|-----------|--------------|

| 3F-F030H | COUNTER#0 | COUNTER#0    |

| 3F-F032H | COUNTER#1 | COUNTER#1    |

| 3F-F034H | COUNTER#2 | COUNTER#2    |

| 3F-F036H | -----     | Control Word |

TIC のレジスタ配置

TIC の各チャネルは下図の様に接続されています。

チャネル 0 は、NMI 生成回路に接続され、モニタ・プログラムのインターバル・タイマとして使用されます。同時にチャネル 0 はチャネル 1 のプリスケール・カウンタとして機能します。

チャネル 1 は、ユーザのプログラムで自由に使用する事が出来ます。また、チャネル 0 と 1 の出力は、Status ポートからその状態を読み出す事が出来ます（「6.6 Status 読み出しポート (3F-F060H [Read Only])」参照）。

チャネル 2 は、リフレッシュ・タイミングを生成するために使用されます。したがって、チャネル 2 は、モード 2 で分周を 30(1EH)に設定しなければなりません。

uPD71054 のアクセスには 95nS の RD-/WR- のパルス幅が必要になります。 したがって、これを満足する様に wait を入れなければなりません。wait の設定値については「7.4 SYSTEM-I/O ウェイト」を、設定場所については「6.7 BIC (Bus-Interface-Control) (3F-F080H ~ 3F-F0F0H)」を参照してください。

uPD71054 はコマンド・リカバリ・タイムとして 165ns 必要とします。 リカバリ・タイムについては「7.5 SYSTEM-I/O コマンド・リカバリ・タイム」を参照してください。

TIC は、システム・リセットによってリセットされます（「9.1 RESET-」参照）。

#### 6.4. 7セグメントLED表示データ出力ポート(3F-F040H [Write Only])

ベースボード上の7セグメントLEDに表示するデータを設定します。データ・フォーマットを下表に示します。該当するビットに0を設定すると対応するセグメントが点灯します。

| Bit7  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------|------|------|------|------|------|------|------|

| DPseg | Gseg | Fseg | Eseg | Dseg | Cseg | Bseg | Aseg |

#### 6.5. DIPSW1 読み出しポート(3F-F050H [Read Only])

ベースボード上のDIPSW1の状態を読み出すためのポートです。データ・フォーマットを下表に示します。

| Bit7   | Bit6   | Bit5   | Bit4   | Bit3  | Bit2  | Bit1  | Bit0  |

|--------|--------|--------|--------|-------|-------|-------|-------|

| SW1-8  | SW1-7  | SW1-6  | SW1-5  | SW1-4 | SW1-3 | SW1-2 | SW1-1 |

| no use | no use | no use | no use | TIM1  | TIM0  | BPS1  | BPS0  |

**SW1-[8..1]** : ボード上に実装されているSW1の状態を読み出せます。SW1-1がSW1の”1”のスイッチに、SW1-8がSW1の”8”のスイッチに対応しています。また、該当するビットのスイッチがONで0が、OFFで1が読み出されます。

DIPSW1の幾つかのビットはベースボード上に実装されたROM内のモニタにより下表の様に予約されています。しかし、これらの機能はソフトウェア的に定義されているものであり、スイッチの切り替えがハードウェア的に作用して機能が切り替わるものではありません。

| BPS1 | BPS0 | Multiをシリアル回線で用いる場合のボーレイト |

|------|------|--------------------------|

| 0    | 0    | don't use                |

| 0    | 1    | 38400bps                 |

| 1    | 0    | 19200bps                 |

| 1    | 1    | 9600bps                  |

| TIM1 | TIM0 | タイマーレイト       |

|------|------|---------------|

| 0    | 0    | タイマを使用しない     |

| 0    | 1    | 200Hz(5ms)    |

| 1    | 0    | 100Hz(10ms)   |

| 1    | 1    | 60Hz(16.67ms) |

#### 6.6. Status 読み出しポート(3F-F060H [Read Only])

| Bit7       | Bit6  | Bit5  | Bit4       | Bit3 | Bit2 | Bit1 | Bit0 |

|------------|-------|-------|------------|------|------|------|------|

| TOVER_FLG- | TOUT1 | TOUT0 | MEM1M/16M- | PD4  | PD3  | PD2  | PD1  |

**PD[4..1]** : ボードに実装されている DRAM ( 72 ピン SIMM ) の PD[4..1]が読みだせます。PD[2..1]の状態によって、実装されている DRAM のサイズを確認できます。PD[2..1]と DRAM の容量の関係を表に示します。

| PD[2] | PD[1] | DRAM の容量 |

|-------|-------|----------|

| 0     | 0     | 4M バイト   |

| 0     | 1     | 予約       |

| 1     | 0     | 16M バイト  |

| 1     | 1     | 8M バイト   |

PD[2..1]と DRAM の容量

**MEM1M/16M-** : ソケットボードの CPU の持つ外部アドレス空間が 16M バイトの時”0”、1M バイトの時”1”が読み出せます。

**TOUT0,TOUT1** : TIC ( μPD71054 ) のチャンネル 0 とチャンネル 1 の出力端子の状態を読み出す事が出来ます ( 「6.3TIC ( uPD71054 ) (3F-F030H ~ 3F-F038H)」参照 )

**TOVER\_FLG-** : バス・サイクルが 31 サイクル以上となり、タイム・アウト・レディーが発生すると”0”となります。フラグをクリアする ( ”1”にもどす ) には、TOVER\_RDY\_INT\_CLR ( 3F-F190h ) を使用します。

### 6.7. BIC (Bus-Interface-Control) (3F-F080H ~ 3F-F0F0H)

ベースボード上の ROM, SRAM, DRAM, ポートのアクセスに関するパラメータを設定します。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2     | Bit1       | Bit0       |

|----------|------|------|------|------|------|----------|------------|------------|

| 3F-F080H | ---  | ---  | ---  | ---  | ---  | ---      | SRAMWAIT1  | SRAMWAIT0  |

| 3F-F090H | ---  | ---  | ---  | ---  | ---  | ---      | ---        | ---        |

| 3F-F0A0H | ---  | ---  | ---  | ---  | ---  | ---      | PRCWIDE1   | PCRWIDE0   |

| 3F-F0B0H | ---  | ---  | ---  | ---  | ---  | ---      | RASWIDE1   | RASWIDE0   |

| 3F-F0C0H | ---  | ---  | ---  | ---  | ---  | ---      | CASRDWIDE1 | CASRDWIDE0 |

| 3F-F0D0H | ---  | ---  | ---  | ---  | ---  | ---      | ---        | PAGEMODE   |

| 3F-F0E0H | ---  | ---  | ---  | ---  | ---  | ---      | SYSIOWAIT1 | SYSIOWAIT0 |

| 3F-F0F0H | ---  | ---  | ---  | ---  | ---  | ROMWAIT2 | ROMWAIT1   | ROMWAIT0   |

| SRAMWAIT1 | SRAMWAIT0 | 機能                    |

|-----------|-----------|-----------------------|

| 0         | 0         | SRAM アクセスのウェイトを 0 に設定 |

| 0         | 1         | SRAM アクセスのウェイトを 1 に設定 |

| 1         | 0         | SRAM アクセスのウェイトを 2 に設定 |

| 1         | 1         | SRAM アクセスのウェイトを 3 に設定 |

システム・リセットにより[1,1]に初期化されます。

| PRCWIDE1 | PRCWIDE0 | 機能                              |

|----------|----------|---------------------------------|

| 0        | 0        | DRAM アクセスの RAS プリチャージを 1clk に設定 |

| 0        | 1        | DRAM アクセスの RAS プリチャージを 2clk に設定 |

| 1        | 0        | DRAM アクセスの RAS プリチャージを 3clk に設定 |

| 1        | 1        | DRAM アクセスの RAS プリチャージを 4clk に設定 |

システム・リセットにより[1,1]に初期化されます。

| RASWIDE1 | RASWIDE0 | 機能                               |

|----------|----------|----------------------------------|

| 0        | 0        | DRAM アクセスの RAS の Low 幅を 1clk に設定 |

| 0        | 1        | DRAM アクセスの RAS の Low 幅を 2clk に設定 |

| 1        | 0        | DRAM アクセスの RAS の Low 幅を 3clk に設定 |

| 1        | 1        | DRAM アクセスの RAS の Low 幅を 4clk に設定 |

システム・リセットにより[1,1]に初期化されます。

| CASRDWIDE1 | CASRDWIDE0 | 機能                                  |

|------------|------------|-------------------------------------|

| 0          | 0          | DRAM リードアクセスの CAS の Low 幅を 1clk に設定 |

| 0          | 1          | DRAM リードアクセスの CAS の Low 幅を 2clk に設定 |

| 1          | 0          | DRAM リードアクセスの CAS の Low 幅を 3clk に設定 |

| 1          | 1          | DRAM リードアクセスの CAS の Low 幅を 4clk に設定 |

システム・リセットにより[1,1]に初期化されます。

| PAGEMODE | 機能                |

|----------|-------------------|

| 0        | DRAM をページモードで用いない |

| 1        | DRAM をページモードで用いる  |

システム・リセットにより[0]に初期化されます。

| SYSIOWAIT1 | SYSIOWAIT0 | 機能                            |

|------------|------------|-------------------------------|

| 0          | 0          | (SYSTEM-I/O アクセスのウェイトを 8 に設定) |

| 0          | 1          | SYSTEM-I/O アクセスのウェイトを 1 に設定   |

| 1          | 0          | SYSTEM-I/O アクセスのウェイトを 2 に設定   |

| 1          | 1          | SYSTEM-I/O アクセスのウェイトを 3 に設定   |

システム・リセットにより[1,1]に初期化されます。

| ROMWAIT2 | ROMWAIT1 | ROMWAIT0 | 機能                   |

|----------|----------|----------|----------------------|

| 0        | 0        | 0        | ROM アクセスのウェイトを 8 に設定 |

| 0        | 0        | 1        | ROM アクセスのウェイトを 1 に設定 |

| 0        | 1        | 0        | ROM アクセスのウェイトを 2 に設定 |

| 0        | 1        | 1        | ROM アクセスのウェイトを 3 に設定 |

| 1        | 0        | 0        | ROM アクセスのウェイトを 4 に設定 |

| 1        | 0        | 1        | ROM アクセスのウェイトを 5 に設定 |

| 1        | 1        | 0        | ROM アクセスのウェイトを 6 に設定 |

| 1        | 1        | 1        | ROM アクセスのウェイトを 7 に設定 |

システム・リセットにより[1,1,1]に初期化されます。

ウェイトおよび DRAM 関連の推奨設定値については、「7推奨設定」を参照してください。

DRAM 関連の設定値の意味については「12.2DRAM インターフェース」を参照してください。

### 6.8. NMI セレクト・ポート(3F-F140H ~ 3F-F150H)

NMI 信号の生成を制御するポートです。NMI 信号の生成ロジックについては、「9.2NMI-」を参照してください。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3         | Bit2        | Bit1        | Bit0         |

|----------|------|------|------|------|--------------|-------------|-------------|--------------|

| 3F-F140H | ---  | ---  | ---  | ---  | ISACOM_NMIEN | PRT_NMIEN   | UART2_NMIEN | UART1_NMIEN  |

| 3F-F150H | ---  | ---  | ---  | ---  | 予約(0)        | TIMER_NMIEN | TOVER_NMIEN | EXTBUS_NMIEN |

各ビットは該当割り込み要求により NMI を発生される時"1"に、発生させない時に"0"に設定します。

**UART1\_NMIEN** : TL16C552A の UART-CH#1 の割り込み要求

**UART2\_NMIEN** : TL16C552A の UART-CH#2 の割り込み要求

**PRT\_NMIEN** : TL16C552A の PRINTER の割り込み要求

**ISACOM\_NMIEN** : ISA バスとの通信による割り込み要求

**EXTBUS\_NMIEN** : EXTBUS からの割り込み要求

**TOVER\_NMIEN** : タイムオーバ・レディーの発生による割り込み要求

**TIMER\_NMIEN** : uPD71054 の TOUT0 による割り込み要求

**予約(0)** : このビットは予約されています。“0”に設定して下さい。

### 6.9. NMI ステータス・ポート(3F-F160H ~ 3F-F170H [Read only])

NMI 要求の要求元を特定するためのポートです。NMI 信号の生成ロジックについては、「9.2NMI-」を参照してください。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3       | Bit2      | Bit1      | Bit0       |

|----------|------|------|------|------|------------|-----------|-----------|------------|

| 3F-F160H | ---  | ---  | ---  | ---  | ISACOM_NMI | PRT_NMI   | UART2_NMI | UART1_NMI  |

| 3F-F170H | ---  | ---  | ---  | ---  | ---        | TIMER_NMI | TOVER_NMI | EXTBUS_NMI |

各ビットは該当割り込み要求により NMI が発生している時"1"が、発生していない時"0"が読み出せます。各ビットは、各割り込み要求元の割り込み要求状態を示し、NMI イネーブル・ポートの設定の影響を受けません。従って、NMI ステータス・ポートの内容と NMI セレクト・ポートの内容を AND したものが、NMI 発生の原因となっている割り込み要因です。

**UART1\_NMI** : TL16C552A の UART-CH#1 の割り込み要求

**UART2\_NMI** : TL16C552A の UART-CH#2 の割り込み要求

**PRT\_NMI** : TL16C552A の PRINTER の割り込み要求

**ISACOM\_NMI** : ISA バスとの通信による割り込み要求

**EXTBUS\_NMI** : JEXT バスからの割り込み要求

**TOVER\_NMI** : タイムオーバ・レディーの発生による割り込み要求

**TIMER\_NMI** : uPD71054 の TOUT0 による割り込み要求

### 6.10. NMI/INT0/INT1 マスク・ポート(3F-F180H)

NMI,INT0,INT1 の最終的なマスクを制御するポートです。NMI 信号の生成ロジックについては「9.2NMI-」を、マスカブル割り込みの生成ロジックについては「9.3マスカブル割り込み」を参照してください。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2      | Bit1      | Bit0     |

|----------|------|------|------|------|------|-----------|-----------|----------|

| 3F-F180H | ---  | ---  | ---  | ---  | ---  | INT1_MASK | INT0_MASK | NMI_MASK |

**NMI\_MASK** : CPU への NMI-信号をマスクする時"1"、マスクしない時"0"を設定

**INT0\_MASK** : CPU への INT0(P22/INTP01)信号をマスクする時"1"、マスクしない時"0"を設定

**INT1\_MASK** : CPU への INT1(P24/INTP03)信号をマスクする時"1"、マスクしない時"0"を設定

### 6.11. NMI/INT1 要求クリア・ポート(3F-F190H,3F-F1A0H [Write Only])

NMI/INT1 要求要因のうち、割り込みの発生がラッチされているものについて、そのラッチされた要求をクリアするポートです。データは無視されます。

| アドレス     | 書き込み                                                         |

|----------|--------------------------------------------------------------|

| 3F-F190H | タイムオーバ・レディーの発生による NMI/INT1 要求をクリアする<br>(「12.1タイムオーバ・レディー」参照) |

| 3F-F1A0H | uPD71054 の TOUT0 による NMI/INT1 要求をクリアする                       |

### 6.12. INT0(P22/INTP01)セレクト・ポート(3F-F200H)

INT0(P22/INTP01)信号の生成を制御するポートです。INT0 信号の生成ロジックについては、「9.3マスカブル割り込み」を参照してください。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2       | Bit1          | Bit0         |

|----------|------|------|------|------|------|------------|---------------|--------------|

| 3F-F200H | ---  | ---  | ---  | ---  | ---  | PRT_INT0EN | ISACON_INT0EN | UART1_INT0EN |

各ビットは該当割り込み要求により INT0(P22/INTP01)を発生される時"1"に、発生させない時に"0"に設定します。

**UART1\_INT0EN** : TL16C552A の UART-CH#1 の割り込み要求

**ISACON\_INT0EN** : ISA バスとの通信による割り込み要求

**PRT\_INT0EN** : TL16C552A の PRINTER の割り込み要求

### 6.13. INT1(P24/INTP03)セレクト・ポート(3F-F210H)

INT1(P24/INTP03)信号の生成を制御するポートです。INT1 信号の生成ロジックについては、「9.3 マスカブル割り込み」を参照してください。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2  | Bit1         | Bit0         |

|----------|------|------|------|------|------|-------|--------------|--------------|

| 3F-F210H | ---- | ---- | ---- | ---- | ---- | 予約(0) | TOVER_INT1EN | TIMER_INT1EN |

各ビットは該当割り込み要求により INT1(P24/INTP03)を発生される時"1"に、発生させない時に"0"に設定します。

**TIMER\_INT1EN** : uPD71054 の TOUT0 による割り込み要求

**TOVER\_INT1EN** : タイムオーバ・レディーの発生による割り込み要求

**予約(0)** : このビットは予約されています。“0”に設定して下さい。

### 6.14. INT0(P22/INTP01)ステータス・ポート(3F-F220H [Read only])

INT0(P22/INTP01)要求の要求元を特定するためのポートです。INT0 信号の生成ロジックについては、「9.3 マスカブル割り込み」を参照してください。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2     | Bit1        | Bit0       |

|----------|------|------|------|------|------|----------|-------------|------------|

| 3F-F220H | ---- | ---- | ---- | ---- | ---- | PRT_INT0 | ISACON_INT0 | UART1_INT0 |

各ビットは該当割り込み要求により INT0 が発生している時"1"が、発生していない時"0"が読み出せます。各ビットは、各割り込み要求元の割り込み要求状態を示し、INT0 イネーブル・ポートの設定の影響を受けません。従って、INT0 ステータス・ポートの内容と INT0 セレクト・ポートの内容を AND したものが、INT0 発生の原因となっている割り込み要因です。

**UART1\_INT0** : TL16C552A の UART-CH#1 の割り込み要求

**ISACOM\_INT0** : ISA バスとの通信による割り込み要求

**PRT\_INT0** : TL16C552A の PRINTER の割り込み要求

### 6.15. INT1(P24/INTP03)ステータス・ポート(3F-F230H [Read only])

INT1(P24/INTP03)要求の要求元を特定するためのポートです。INT1 信号の生成ロジックについては、「9.3 マスカブル割り込み」を参照してください。

| アドレス     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1       | Bit0       |

|----------|------|------|------|------|------|------|------------|------------|

| 3F-F230H | ---- | ---- | ---- | ---- | ---- | ---- | TOVER_INT1 | TIMER_INT1 |

各ビットは該当割り込み要求により INT1 が発生している時"1"が、発生していない時"0"が読み出せます。各ビットは、各割り込み要求元の割り込み要求状態を示し、INT1 イネーブル・ポートの設定の影響を受けません。従って、INT1 ステータス・ポートの内容と INT1 セレクト・ポートの内容を AND したものが、INT1 発生の原因となっている割り込み要因です。

**TIMER\_INT1** : uPD71054 の TOUT0 による割り込み要求

**TOVER\_INT1** : タイムオーバ・レディーの発生による割り込み要求

## 7. 推奨設定

ここでは、メモリ資源のアクセスに関するパラメータについての推奨値を示します。

### 7.1. CPU 設定

CPU 内蔵のバス制御機能の設定値に対して一切の制限事項はありません。したがって、バス・パフォーマンスを最大にするには、SFR の DWC(0xffff-f060)を 0x0000 に、BCC(0xffff-f062)を 0x0000 に設定します。

### 7.2. SRAM/ROM

下表に SRAM と、アクセスタイム 120ns/150nS の ROM を用いた場合の Wait の推奨値を示します。

| CPU   | SRAM-Wait 数 | ROM(120ns) Wait 数 | ROM(150nS) Wait 数 |

|-------|-------------|-------------------|-------------------|

| 25MHz | 0Wait       | 3Wait             | 3Wait             |

### 7.3. DRAM

下表にアクセスタイム 60nS の DRAM を用いた場合の設定推奨値を示します。

| アクセスタイム | CPU   | RAS プリチャージ | RAS 幅 | Read サイクル CAS 幅 |

|---------|-------|------------|-------|-----------------|

| 60nS    | 25MHz | 1CLK       | 2CLK  | 2CLK            |

| 70nS    | 25MHz | 2CLK       | 2CLK  | 2CLK            |

### 7.4. SYSTEM-I/O ウェイト

下表に SYSTEM-I/O の Wait の推奨値を示します。SYSTEM-I/O のウェイと数は、SYSTEM-I/O 空間で最も遅い uPD71054 のアクセスによって決まります。

|       | SYSTEM-I/O-Wait 数 |

|-------|-------------------|

| 25MHz | 2Wait             |

### 7.5. SYSTEM-I/O コマンド・リカバリ・タイム

TL16C552A および uPD71054 のアクセスについては、コマンド・リカバリ・タイムの制限を満たす必用があります。したがって、TL16C552A および uPD71054 へ連続的にアクセスする場合は、1 回目のアクセスの後一定時間以上経ってから 2 回目のアクセスを行う必用があります。

また、TL16C552A と uPD71054 はコマンド信号(RD-/WR-)を共有しているため、リカバリ・タイムの大きい uPD71054 によってリカバリ・タイムが決まります。

リカバリ・タイムは、TL16C552A および uPD71054 以外のメモリ資源をリード・アクセスすることで発生させます。リカバリ・タイムを生成するためにリード・アクセスする推奨メモリ資源は、DIPSW1 読み出しポート(3F-F050H)です。

したがって、TL16C552A および uPD71054 へのアクセスの直後に、DIPSW1 読み出しポートのリード・サイクルを下表で示す回数発生させてください。

|                          | DIPSW1 読み出しポートのリード・サイクル |

|--------------------------|-------------------------|

| SYSTEM-I/O コマンド・リカバリ・タイム | 2 回 (CPU 動作周波数に依存せず)    |

注意事項として、TL16C552A および uPD71054 へのアクセスの後リカバリ・タイムを満足しないうちに、いかなるライト・サイクルも V852 の拡張外部バスに発生させてはなりません。したがって、リカバリ・タイム発生処理はサブルーチンにせず、サブルーチン化したい場合はマクロを使って下さい。サブルーチンにすると、リカバリ・タイム発生用リード・サイクルの前にスタック・ライトが発生し、スタックの位置によっては拡張外部バスにライト・サイクルが現われてしまうためです。

## 8. JEXT パス仕様

JEXT は、メモリや I/O などを拡張できるように用意されたコネクタです。このコネクタには、本ボードの内部のローカル・バスが接続されています。

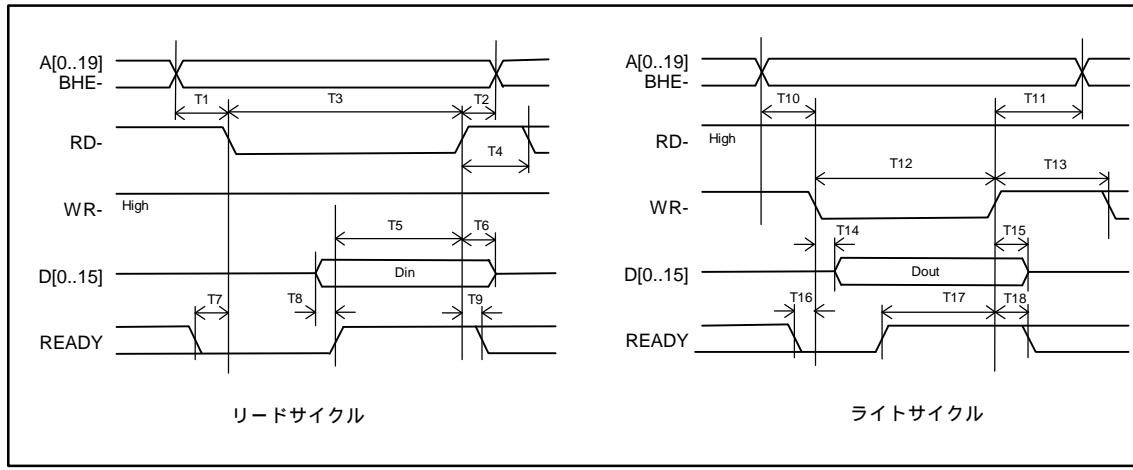

以下に JEXT コネクタのピン配置、信号およびタイミングを示します。

| 番号 | 信号名 | 番号 | 信号名 | 番号 | 信号名    | 番号 | 信号名    |

|----|-----|----|-----|----|--------|----|--------|

| 1  | +5V | 2  | +5V | 31 | GND    | 32 | GND    |

| 3  | D0  | 4  | D1  | 33 | A8     | 34 | A9     |

| 5  | D2  | 6  | D3  | 35 | A10    | 36 | A11    |

| 7  | D4  | 8  | D5  | 37 | A12    | 38 | A13    |

| 9  | D6  | 10 | D7  | 39 | A14    | 40 | A15    |

| 11 | GND | 12 | GND | 41 | +5V    | 42 | +5V    |

| 13 | D8  | 14 | D9  | 43 | A16    | 44 | A17    |

| 15 | D10 | 16 | D11 | 45 | A18    | 46 | A19    |

| 17 | D12 | 18 | D13 | 47 | BHE-   | 48 | GND    |

| 19 | D14 | 20 | D15 | 49 | GND    | 50 | RD-    |

| 21 | +5V | 22 | +5V | 51 | WR-    | 52 | RESET- |

| 23 | A0  | 24 | A1  | 53 | GND    | 54 | GND    |

| 25 | A2  | 26 | A3  | 55 | READY  | 56 | INT-   |

| 27 | A4  | 28 | A5  | 57 | GND    | 58 | GND    |

| 29 | A6  | 30 | A7  | 59 | CPUCLK | 60 | GND    |

JEXT コネクタピン配置

| 信号名      | 入出力 | 機能                                                                                                                                 |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| A[0..19] | 出力  | アドレス・バス信号。CPU のアドレス信号をバッファして接続。                                                                                                    |

| BHE-     | 出力  | バイトハイ・イネーブル信号。CPU のUBE-信号をバッファして接続。                                                                                                |

| D[0..15] | 入出力 | データ・バス信号。CPU のデータ・バス信号をバッファして接続。<br>また、ボード上で 10K ブルアップ。                                                                            |

| RD-      | 出力  | リード・サイクルのタイミング信号。JEXT 空間のアクセス時のみ、<br>アクティブになる。                                                                                     |

| WR-      | 出力  | ライト・サイクルのタイミング信号。JEXT 空間のアクセス時のみ、<br>アクティブになる。                                                                                     |

| READY    | 入力  | サイクルの終了を CPU に通知する信号。JEXT 空間のみで有効。<br>確実に CPU に READY を認識させるためには、RD-もしくは WR-がインアクティブになるまで READY をアクティブに保つことが必要。また、ボード上で 10K ブルアップ。 |

| INT-     | 入力  | Low アクティブの割り込み要求信号。バッファ後、SW3-3 を経由して、CPU の P23/INTP02 端子、及びマスク回路を経由して CPU の NMI 端子に接続されている。また、ボード上で 10K ブルアップ。<br>(3.15参照、9.2参照)   |

| RESET-   | 出力  | Low アクティブのシステム・リセット信号。                                                                                                             |

| CLK      | 出力  | クロック信号。V852 の CLKOUT 端子がバッファ後、接続されている。                                                                                             |

JEXT コネクタ信号

JEXT バス・サイクル

| 記号  | 内容                     | MIN(ns) | MAX(ns) |

|-----|------------------------|---------|---------|

| T1  | RD アドレス セットアップ時間       | 0       |         |

| T2  | RD アドレス ホールド時間         | 0       |         |

| T3  | RD サイクル時間              | 50      |         |

| T4  | RD サイクル間隔              | 20      |         |

| T5  | RD データ セットアップ時間        | 15      |         |

| T6  | RD データ ホールド時間          | 0       |         |

| T7  | RD READY WAIT セットアップ時間 | 0       |         |

| T8  | RD READY セットアップ時間      | 0       |         |

| T9  | RD READY ホールド時間        | 0       |         |

| T10 | WR アドレス セットアップ時間       | 0       |         |

| T11 | WR アドレス ホールド時間         | 20      |         |

| T12 | WR サイクル時間              | 50      |         |

| T13 | WR サイクル間隔              | 20      |         |

| T14 | WR データ 遅延時間            |         | 20      |

| T15 | WR データ ホールド時間          | 20      |         |

| T16 | WR READY WAIT セットアップ時間 | 0       |         |

| T17 | WR READY セットアップ時間      | 0       |         |

| T18 | WR READY ホールド時間        | 0       |         |

JEXT バス AC スペック

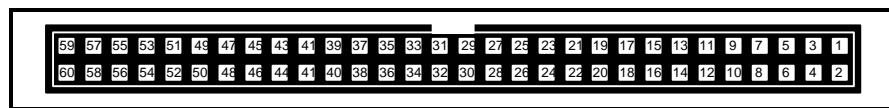

JEXT のピン配置

## 9. その他のCPU資源

### 9.1. RESET-

CPUへのリセットは下記に示した要因で発生します。このリセットは、CPUのリセットと共に、ボード制御回路のシステム・リセットとなります。

- **パワーオン・リセット**: ボードの電源ON時に発生するリセットです。

- **JROMEMからのリセット要求**: ベースボードのJROMEMコネクタのRESET-端子からの入力によるリセットです。詳細は『3.19ROMエミュレータ用テストピン[ベースボード](JROMEM)』を参照して下さい。

- **SWRESETによるリセット**: ベースボードのリアパネル部分に用意されているリセット・スイッチ(SWRESET)が押されるとリセットが発生します。

- **RESET\_SWによるリセット**: ソケットボード上のリセット・スイッチ(RESET\_SW)が押されるとリセットが発生します。

- **ホストからのリセット要求**: ISAバス経由でリセットを発生させることができます。

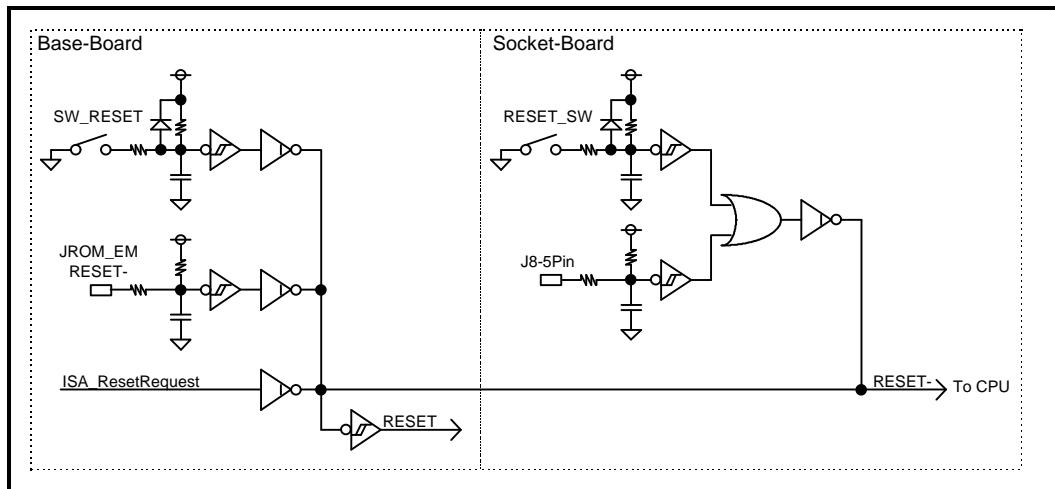

RESETの生成ロジックの概要を下図に示します。

### 9.2. NMI-

CPUへのNMIは下記に示した要因で発生します。

- **ベースボード上のコントローラからの要求**: ベースボード上のUART/PRINT用コントローラ(TL16C522A)からの割り込み要求によってNMIを発生させることができます(「6.2UART/PRINTER(TL16C552A)(3F-F000H~3F-F026H)」を参照)。

- また、ベースボード上のタイマー(uPD71054)からの割り込み要求によってNMIを発生させることができます(「6.3TIC(uPD71054)(3F-F030H~3F-F038H)」を参照)。この割り込みはMultiのプロファイラ等の機能で使用しています(「6.11NMI/INT1要求クリア・ポート(3F-F190H,3F-F1A0H[Write Only])」を参照)。

- これらのどの割り込み要求をNMIに接続するかをプログラマブルに制御出来ます(「6.8NMIセレクト・ポート(3F-F140H~3F-F150H)」を参照)。

- **Readyのタイムオーバによる要求**: バスサイクルがある一定時間以内に終了しなかった場合、タイムアウトReadyが発生しますが、このタイムアウトReadyの発生によりNMI要求を発生させること

が可能です（「6.8NMI セレクト・ポート(3F-F140H ~ 3F-F150H)」を参照）。

- **JEXT バスからの要求**：JEXT バスの INT 信号がアクティブになった時に NMI を発生させる様にすることは可能です（「6.8NMI セレクト・ポート(3F-F140H ~ 3F-F150H)」を参照）。

- **JROMEM からの NMI 要求**：ベースボード上の JROMEM コネクタの NMI-端子からの入力によって NMI が発生します。詳細は「3.19ROM エミュレータ用テストピン [ベースボード] (JROMEM)」を参照してください。

- **ISA バスからの要求**：ISA バス経由の通信制御のために NMI を使用する事が出来ます。Multi を ISA バス経由で接続した場合は、この NMI が使用されます。

- **NMI\_SW による要求**：ソケットボード上の NMI スイッチ(NMI\_SW)が押されると NMI が発生します。

また、NMI はハード的にマスクすることができます。マスク方法については、「6.8NMI セレクト・ポート(3F-F140H ~ 3F-F150H)」および「6.10NMI/INT0/INT1 マスク・ポート(3F-F180H)」を参照してください。

NMI が発生した場合は、下記の手順で処理します。

- NMI マスクポートの NMIMASK に”1”を設定して、NMI をハード的にマスクする。

- NMI の要求元を検査する。NMI ステータスポートにより調べられる（「6.9NMI ステータス・ポート(3F-F160H ~ 3F-F170H [Read only])」を参照）。

- 要求元のための NMI 処理を行ない、要求をクリアする。

- NMI マスクポートの NMIMASK に”0”を設定して、マスクを解除する。

- NMI 処理から復帰する。

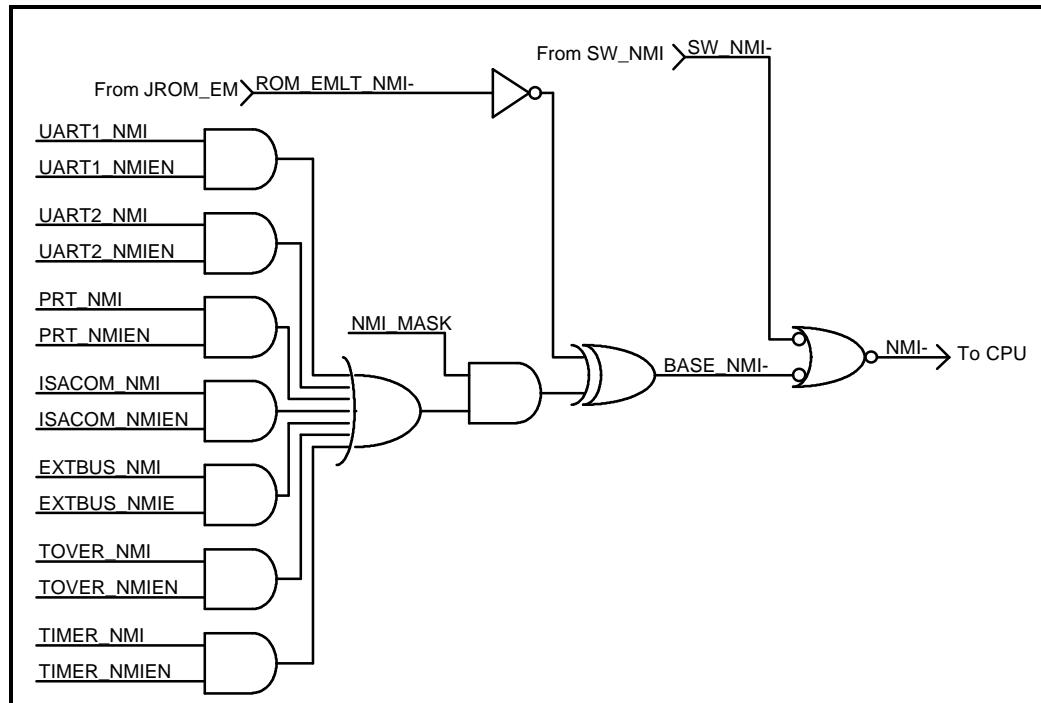

NMI の生成ロジックの概要を下図に示します。

### 9.3. マスカブル割り込み(INT0(P22/INTP01),INT1(P24/INTP03))

INT0(P22/INTP01) は下記に示した要因で発生します。割り込みの選択については「6.12INT0(P22/INTP01)セレクト・ポート(3F-F200H)」を参照してください。

- ベースボード上のコントローラからの要求:** ベースボード上の UART/PRINT 用コントローラ (TL16C522A)からの UART-CH#1 と PRINTER の割り込み要求によって INT0(P22/INTP01)を発生させることができます (「6.2UART/PRINTER ( TL16C552A ) (3F-F000H ~ 3F-F026H)」を参照)

- ISA バスからの要求:** ISA バス経由の通信制御のために INT0(P22/INTP01)を使用する事ができます。

INT1(P24/INTP03) は下記に示した要因で発生します。割り込みの選択については「6.13INT1(P24/INTP03)セレクト・ポート(3F-F210H)」を参照してください。

- ベースボード上のコントローラからの要求:** ベースボード上のタイマー (uPD71054) からの割り込み要求によって INT1(P24/INTP03)を発生させることができます (「6.3TIC ( uPD71054 ) (3F-F030H ~ 3F-F038H)」、 「6.11NMI/INT1 要求クリア・ポート(3F-F190H,3F-F1A0H [Write Only])」を参照)

- Ready のタイムオーバによる要求:** バスサイクルがある一定時間以内に終了しなかった場合、タイムアウト Ready が発生しますが、このタイムアウト Ready の発生により INT1(P24/INTP03)要求を発生させることができます (「6.11NMI/INT1 要求クリア・ポート(3F-F190H,3F-F1A0H [Write Only])」参照)

また、INT0/INT1 はハード的にマスクすることができます。マスク方法については、「6.10NMI/INT0/INT1 マスク・ポート(3F-F180H)」を参照してください。

INT0/INT1 が発生した場合は、下記の手順で処理します。

NMI/INT0/INT1 マスクポートの INT0MASK もしくは INT1MASK に”1”を設定して、INT0/INT1 をハード的にマスクする。

INT0/INT1 の要求元を検査する。INT0 ステータスポートおよび INT1 ステータスポートにより調べられる (「6.14INT0(P22/INTP01)ステータス・ポート(3F-F220H [Read only])」、および「6.15INT1(P24/INTP03)ステータス・ポート(3F-F230H [Read only])」を参照)

要求元のための割り込み処理を行ない、要求をクリアする。

NMI/INT0/INT1 マスクポートの INT0MASK もしくは INT1MASK に”0”を設定して、マスクを解除する。

割り込み処理から復帰する。

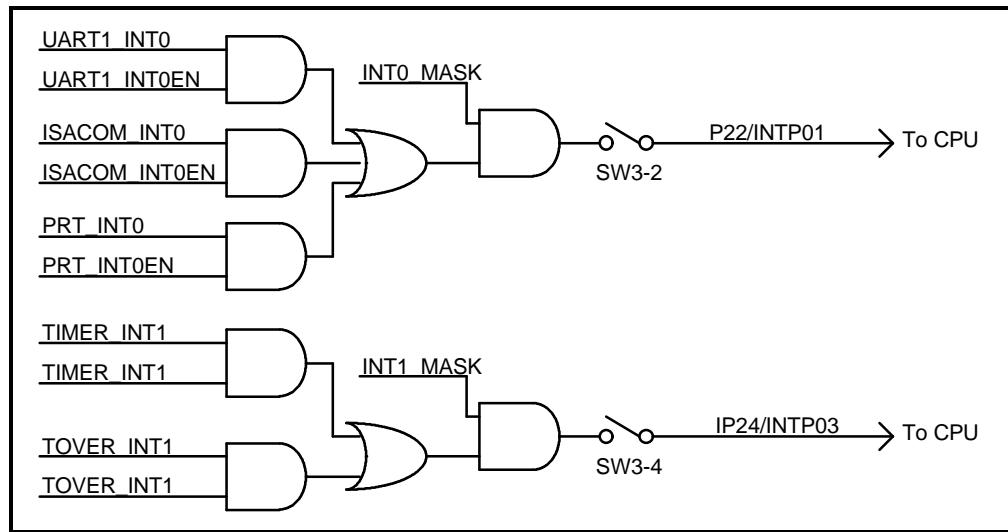

INT0/INT1 の生成ロジックの概要を下図に示します。

#### 9.4. ポート

CPU のポート機能は、拡張外部バスに関する P4[0..7], P5[0..7], P6[0..3], P9[0..6] はベースボードとの接続のために使用しています。

これ以外の、P0[0..7], P1[0..7], P2[1..7], P3[0..7], P10[0..3] はソケット・ボード上のコネクタに接続されており、ユーザに開放されています。コネクタのピン配置については『3.5 プロセッサ・ピンコネクタ [ ソケットボード ] (JPORT0, JPORT1, JPORT2, JPORT3, JPORT10)』を、ボード内部の接続状態については『13CPU ポート接続』を参照してください。

## 10. Multi モニタ

ボードに実装されている ROM には、Multi 用のモニタが組み込まれています。ホストの Multi サーバと接続して使用する場合の注意点について説明します。

### 10.1. モニタ・ワーク RAM

モニタでは、SRAM の上位の 32KB (1F-8000H ~ 1F-FFFFH) をワーク用の RAM として使用しています。したがって、xF-8000H ~ xF-FFFFH (x は 0 ~ 1) はユーザ・プログラムでは使用できません（「5.1メモリ・マップ」参照）。

### 10.2. 割り込み

現在 Multi モニタを使用して、ユーザ・プログラムで割り込み処理はできません。

### 10.3. \_INIT\_SP の設定

モニタで \_INIT\_SP ( スタック・ポインタの初期値 ) は、1F-7FFCH ( モニタ・ワーク RAM の直前 ) に設定されています ( Multi の環境で \_INIT\_SP を変更することもできます )。

### 10.4. リモート接続

Multi のサーバとの接続は、シリアル接続と ISA バス接続が選択できますが、一度接続した方から他方に切り替える場合には、モニタをリセット（リアパネルのリセット・スイッチを押す）してから RTE for Windows のユーティリティ Check RTE で接続を変更してください。

### 10.5. タイマ割り込み

タイマ割り込みを禁止しますと、Multi のプロファイラ機能が使用できません（タイマ割り込みの設定については「4.1ボードの設定」を参照）。

また、V852 では CPU の性格上ブレーク・ポイント機能のためにタイマ割り込みを使用しています。したがって、タイマ割り込みを禁止しますと Multi が使用できなくなります。

## 11. RTE コマンド

サーバ(rteserv)と接続すると TARGET ウィンドウが開かれ、ここで RTE コマンドを発行することができます。表に RTE コマンドの一覧を示します。

| コマンド名   | 内容                |

|---------|-------------------|

| HELP, ? | ヘルプ表示             |

| INIT    | イニシャライズ           |

| VER     | バージョン表示           |

| SFR     | 内蔵レジスタ(SFR)の変更、表示 |

RTE コマンド一覧

各コマンドには、パラメータを必要とするものがあります。アドレスやデータなど、数値のパラメータは、全て 16 進数とみなされます。以下の数値指定は誤りです。

0x1234 1234H \$1234

### 11.1. HELP(?)

<書式> HELP [コマンド名]

HELP は、RTE コマンドの一覧や書式を表示します。また、"HELP"と入力するかわりに"?"としても同様です。コマンド名を省略すると、使用できるコマンド一覧を表示します。

<例> HELP SFR

SFR コマンドのヘルプを表示します。

### 11.2. INIT

<書式> INIT

INIT は、RTE 環境の初期化を行ないます。通常、このコマンドを使用しないでください。

### 11.3. VER

<書式> VER

VER は、RTE 環境のバージョンを表示します。

### 11.4. SFR

<書式> SFR [レジスタ名 [データ]]

SFR は CPU 内蔵レジスタ(SFR)の内容の表示と、書き込みを行います。

パラメータを省略した場合、SFR コマンドで指定できるレジスタ名の一覧が表示されます。

パラメータとしてレジスタ名だけを指定した場合は、該当するレジスタの内容を読み出して表示します。

パラメータとしてレジスタ名とデータを指定した場合は、データを指定されたレジスタに書き込みます。

ただし、読み込み不可レジスタに対して表示を、書き込み不可レジスタに書き込みを指定した場合はエラーになります。また、読み出し / 書き込みの際のアクセスサイズは自動的にレジスタのサイズで行われます。

## 12. バス・サイクル

### 12.1. タイムオーバ・レディー

ベース・ボードは、CPU が外部バス・サイクルを発生させ、そのサイクルがある一定時間以内に終了しなかった場合は、タイムオーバ・レディーを発生させ、強制的にサイクルを終了させています。タイムオーバ・レディーが発生するまでの時間は、バス・サイクルが 1024 クロック (33MHz 動作で約 30.7 μS) 以上継続した場合です。

タイムオーバ・レディーが発生すると、ベースボード上の TOVER-LED が点灯し、NMI および INT1(P24/INTP03)の割り込み要因が発生します。NMI/INT1 要求クリア・ポートへ書き込むと、TOVER-LED が消灯し、NMI および INT1(P24/INTP03)の割り込み要因がクリアされます。

「3.18LED[ ベースボード ]」、「6.8NMI セレクト・ポート(3F-F140H ~ 3F-F150H)」、「6.11NMI/INT1 要求クリア・ポート(3F-F190H,3F-F1A0H [Write Only])」、「6.13INT1(P24/INTP03)セレクト・ポート(3F-F210H)」を参照してください。

## 12.2. DRAM インターフェース

### 12.2.1. 概要

DRAM のアクセスでは、ノーマル・モードとページ・モードをサポートしています。

ページ・モードでは、同じ Row アドレスへのアクセスが続く限り DRAM への RAS 信号をアクティブに保ち続け、CAS 信号のみ操作してアクセスを行います。これにより、同じ Row アドレスに対して連続的にアクセスする場合のアクセス・タイムの短縮が行えます。ただし、異なる Row アドレスへのアクセスが発生した場合は、サイクルが開始してから RAS 信号をインアクティブにし、RAS プリチャージ時間を取ってからアクセスを開始するため、連続アクセスが崩れた場合は逆にアクセスが遅くなります。

したがって、DRAM に対してどの程度連続アクセスが発生するかで、ノーマル・モードとページ・モードのどちらの方がパフォーマンスが上がるかが決まります。

ノーマル・モードかページ・モードなのかは、プログラマブルに設定する事が出来ます(「6.7BIC (Bus-Interface-Control) (3F-F080H ~ 3F-F0F0H)」参照)。

### 12.2.2. 信号の説明

本章で説明する波形に用いられる信号名を下記に説明する。

|        |                                                                               |

|--------|-------------------------------------------------------------------------------|

| CLKOUT | : CPU が出力するシステム・クロック。                                                         |

| ASTB   | : CPU が出力する外部アドレス・ストローブ信号。                                                    |

| DSTB-  | : CPU が出力する外部データ・ストローブ信号。                                                     |

| WAIT-  | : CPU に入力されるウェイト信号。                                                           |

| HIT    | : DRAM をページモードで使用するために、Row アドレスが前のサイクルと一致しているかどうかを示す信号。DRAM のコントロール回路が生成している。 |

| RAS-   | : DRAM に入力される RAS 信号。                                                         |

| CASn-  | : DRAM に入力される CAS 信号。実際には各バイト単位に 1 本づつ存在する(CAS0 ~ CAS3-)。                     |

| WE-    | : DRAM に入力される WE 信号。                                                          |

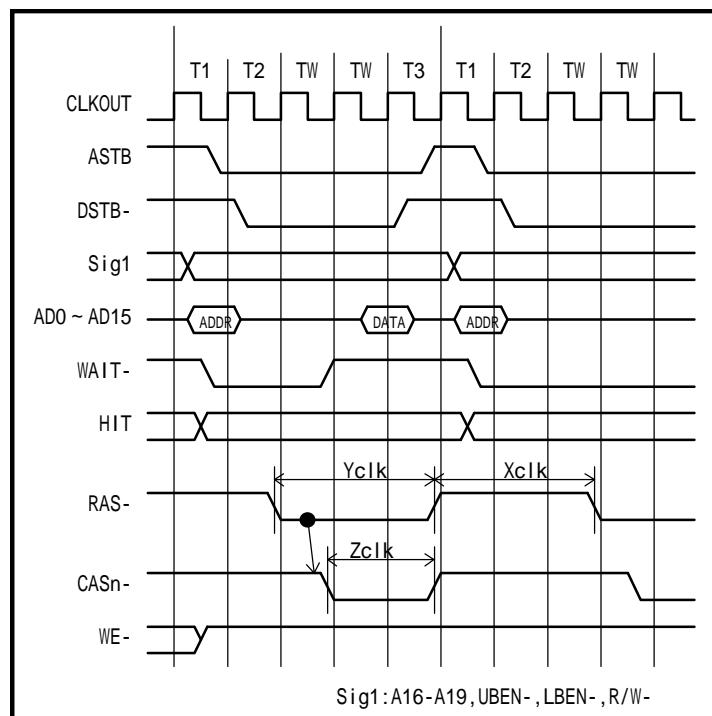

### 12.2.3. シングル・リード(ノーマル・モード)

ノーマル・モードのリード・サイクルは常にシングル・リード・サイクルで行われます。この様子を図に示します。

- 図では、前のサイクルの RAS プリチャージが終了している状態でリード・サイクルが 2 つ連続で発生し、2 サイクル目は RAS プリチャージの間待たされています。

- Xclk,Yclk,Zclk で示されているのは、それぞれプログラムで設定された「RAS プリチャージ」、「RAS の Low 幅」、「リード・アクセスの CAS の Low 幅」のクロック数です(「6.7BIC ( Bus-Interface-Control ) (3F-F080H ~ 3F-F0F0H)」参照)。

- 「RAS の最低 Low 幅」の設定が「リード・アクセスの CAS の Low 幅」より 2 以上大きい場合、Zclk は(Yclk - 1)になります。

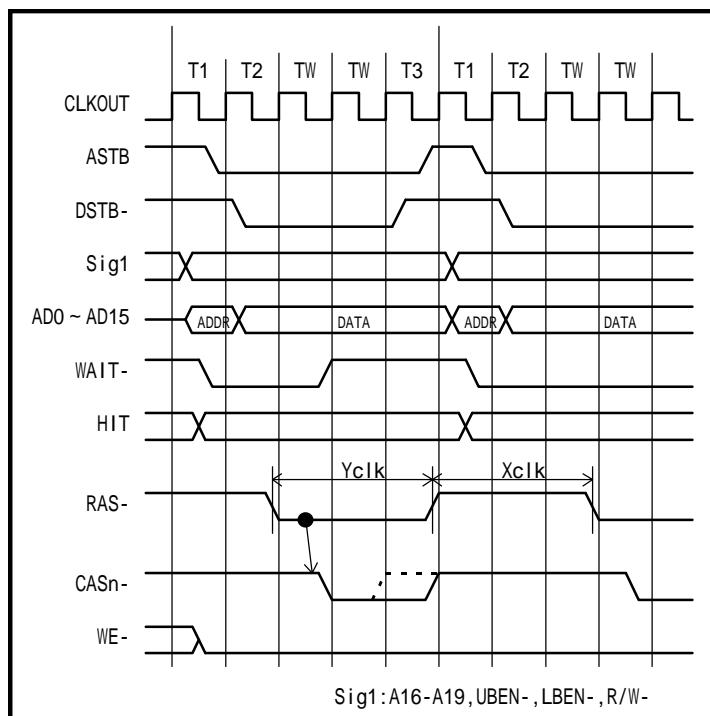

#### 12.2.4. シングル・ライト(ノーマル・モード)

ノーマル・モードのライト・サイクルは常にシングル・ライト・サイクルで行われます。この様子を図に示します。

- 図では、前のサイクルの RAS プリチャージが終了している状態でライト・サイクルが 2 つ連続で発生し、2 サイクル目は RAS プリチャージの間待たされています。

- Xclk,Yclk で示されているのは、それぞれプログラムで設定された「RAS プリチャージ」、「RAS の Low 幅」のクロック数です(「6.7BIC ( Bus-Interface-Control )(3F-F080H ~ 3F-F0F0H )」参照)、「ライト・アクセスの CAS の Low 幅」は常に 1clk です。

- 「RAS の最低 Low 幅」の設定が 2clk より大きい場合、「ライト・アクセスの CAS の Low 幅」は(Yclk - 1)になります。

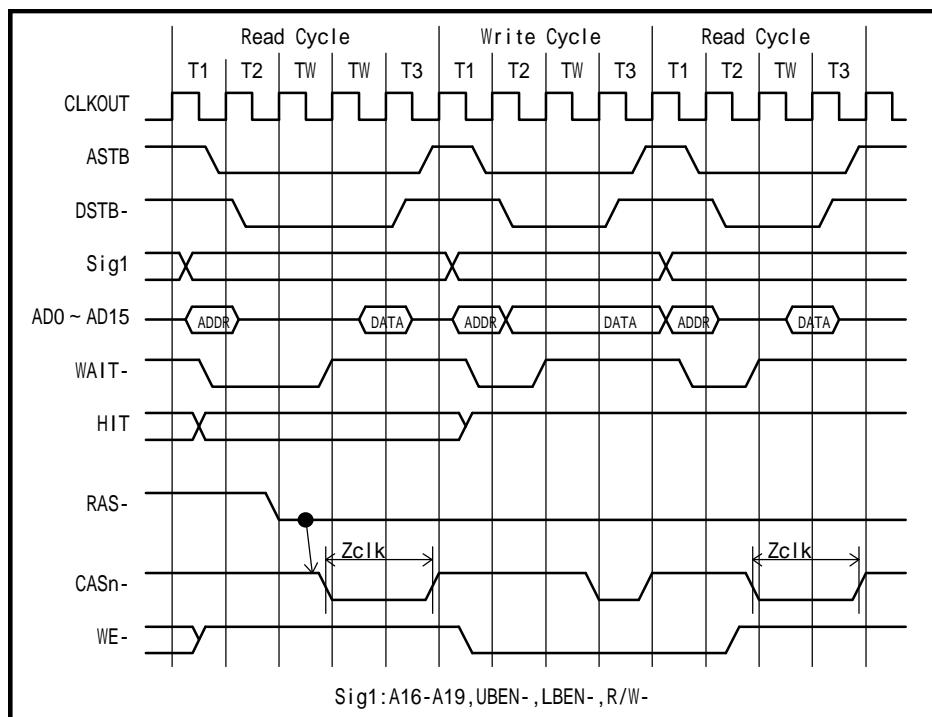

### 12.2.5. ページ・アクセス(ページ・モード、同一Row アドレス)

ページ・モードのサイクルでは、同一 Row アドレスへの連続アクセスであれば、RAS 信号をアクティブにしたままで CAS 信号だけを操作してアクセスします。この様子を図に示します。

- 図では、前のサイクルの RAS プリチャージが終了している状態で、同一 Row アドレスへサイクルが、リード / ライト / リードの順で発生しています。

- Zclk で示されているのは、「リード・アクセスの CAS の Low 幅」のクロック数です(「6.7BIC (Bus-Interface-Control)(3F-F080H ~ 3F-F0F0H)」参照)、「ライト・アクセスの CAS の Low 幅」は常に 1clk です。

- 「RAS の最低 Low 幅」(Yclk)の設定が「リード・アクセスの CAS の Low 幅」より 2 以上大きい場合、同一 Row アドレス・アクセスの最初のサイクルの Zclk は(Yclk - 1)になります。

- ページ・モードで同一 Row アドレスへのアクセスの場合、ページ・モードを用いなかった場合に比較し、最低でも 1Wait 分高速にアクセスできます。「RAS プリチャージ」のクロック数が 2CLK より大きい場合は、更に高速にアクセスできます。

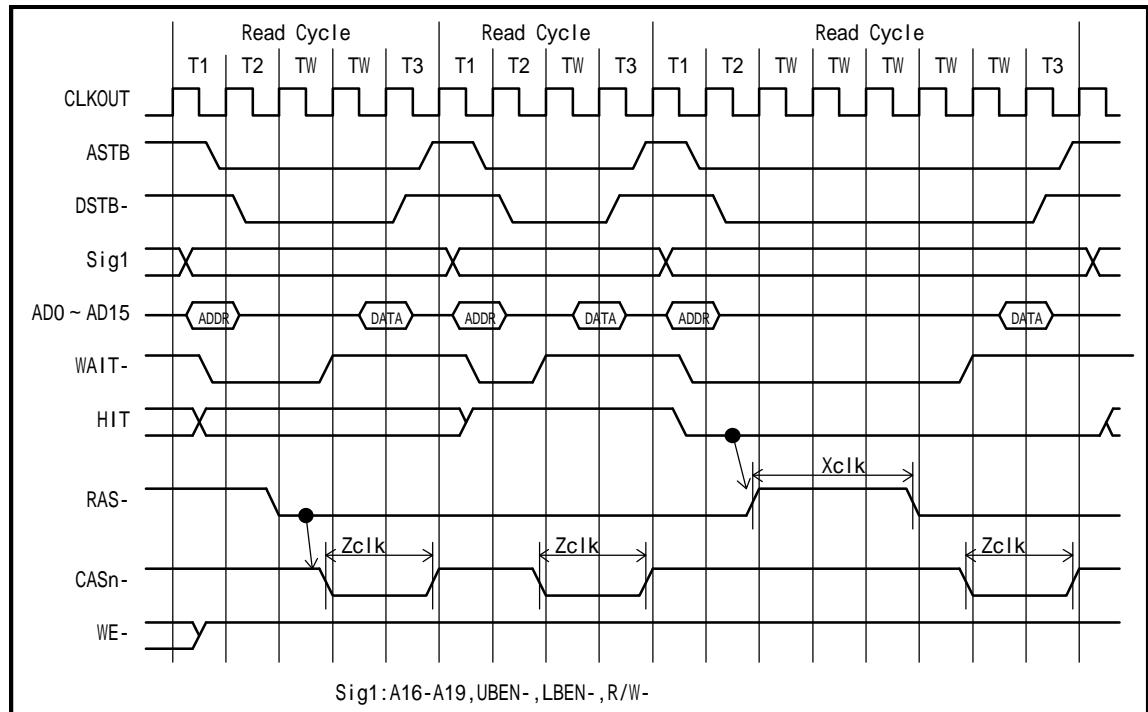

### 12.2.6. ページ・アクセス(ページ・モード、異なるRow アドレス)

ページ・モードで、前のサイクルと異なる Row アドレスへのアクセスでは、サイクル開始から RAS 信号をインアクティブにし、その後 RAS 信号のプリチャージ時間を持ってから再び RAS 信号をアクティブにします。この様子を図に示します。

- 図では、前のサイクルの RAS プリチャージが終了している状態で、同一 Row アドレスヘリード・サイクルが 2 回連続で発生した後、異なる Row アドレスへのリード・サイクルが発生しています。

- Xclk,Zclk で示されているのは、それぞれプログラムで設定された「RAS プリチャージ」、「リード・アクセスの CAS の Low 幅」のクロック数です(「6.7BIC( Bus-Interface-Control )(3F-F080H ~ 3F-F0F0H)」参照)。

- 「RAS の最低 Low 幅」(Yclk)の設定が「リード・アクセスの CAS の Low 幅」より 2 以上大きい場合、同一 Row アドレス・アクセスの最初のサイクルの Zclk は(Yclk - 1)になります。

### 13. CPU ポート接続

本章では、ソケット・ボード上のコネクタに出力されている CPU ポートの接続状態を示します。

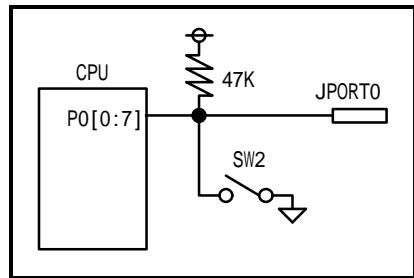

#### 13.1. P00~P07

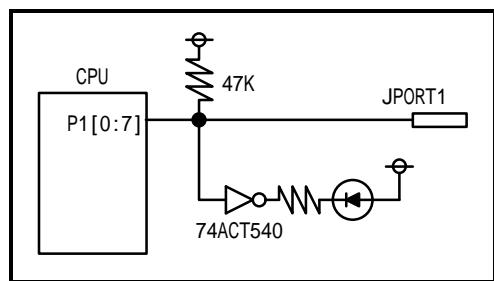

#### 13.2. P10~P17

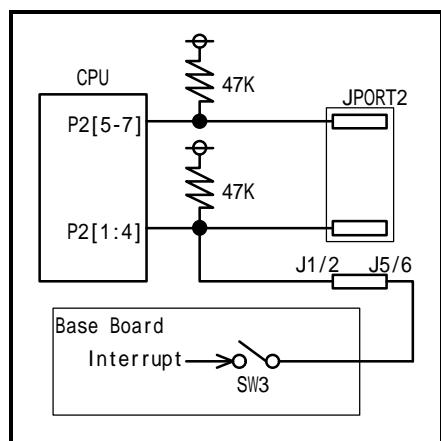

#### 13.3. P20~P27

## 13.4. P30 ~ P37

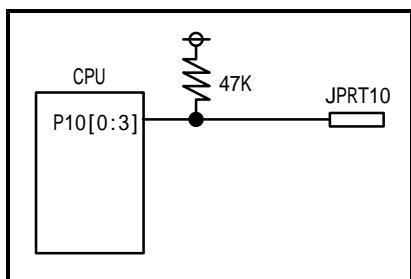

## 13.5. P100 ~ P103

## 14. マスカブル割り込みを使用したアプリケーションの開発

RTE-V852/3-PC 上でマスカブル割り込みを使用したアプリケーションの開発を行う場合の方法と制限事項について説明します。

### 14.1. 割り込みベクタ

V852/3 の割り込みベクタ領域である 0000H ~ 07FFH 番地は、ROM により固定されていて書き換えることが出来ません。そこで Multi 用モニタ ROM では、SRAM 上に代替えのベクタ領域を用意し、0000H ~ 07FFH 番地のベクタには、その代替えベクタ領域への分岐命令が置かれています。

例えば、例外コードが 0080H の割り込みが発生すると、CPU の割り込み機能により 0080H 番地に分岐します。そこには代替えベクタ領域のオフセット 0080H 番地への分岐命令があります。したがって、ユーザ・プログラムでは、この代替えベクタ領域を本来のベクタ領域と同じように書き換えれば、割り込み発生時にユーザ・プログラムの割り込み処理ルーチンに分岐するように出来ます。通常の V852/3 のプログラムと異なるのは、通常はベクタ領域は ROM 化の時点で固定されており、プログラムで設定（書き換える）必用はありません。しかし、RTE-V852/3-PC 上で Multi を使用したプログラムの場合、プログラムでベクタを書き換えてから、割り込みを許可する必用があります。

代替えベクタ領域は、SRAM 上の 1F-8000H ~ 1F-87FFH にあります（実際には SRAM のイメージが出ますので、他のアドレスからでも参照 / 変更可能ですが、CPU が最初に参照する割り込みベクタが分岐するのは 1F-8000H ~ 1F-87FFH です）。したがって、前述の例外コード 0080H の割り込みの場合、目的の割り込み処理に分岐する命令を 1F-8080H 番地に書き込みます。

代替えベクタを書き換えるためのプログラム例を下記に示します（割り込み処理ルーチンから代替えベクタ領域への相対アドレスが 22Bit 以内の場合）

```

void SetAJump(int addr, int jmpdest) /* ベクタ設定ルーチン */

{

/* int addr;                                address where we're restoring the 'jr' */

/* int jmpdest;      address where the 'jr' jumps to */

{

int offset;

unsigned inst;

unsigned int *p;

offset = jmpdest - addr;

inst = 0x07800000 /* 'jr' opcode */ | (offset & 0x003ffff);

*((UINT16 *) (addr)) = (inst >> 16) & 0xffff;

*((UINT16 *) (addr + 2)) = (inst) & 0xffff;

}

.....

}

void __interrupt IntEntry() /* 割り込み処理ルーチン */

{

.....

}

main()

{

.....

SetAJump((int)(0x080 + 0x1f8000), (int)IntEntry);

/* 以下の実装は、この例では不要 */

}

```

#### 14.2. 一般的な制限事項 / 注意事項

マスカブル割り込みを使用したアプリケーションをデバッグするまでの制限事項と注意事項を下記に示します。

- 1 ) 代替えベクタの設定の設定前に割り込みが発生した場合や、代替えベクタを正しく設定しないで割り込みが発生した場合には、割り込みの発生時点でのプログラム位置でブレークします。これは、代替えベクタの初期値がモニタ ROM のブレーク処理ルーチンへの分岐命令になっているためです。

- 2 ) 代替えベクタ領域から割り込み処理ルーチンまでの相対アドレスが 22Bit を超える場合、割り込み処理ルーチンへの分岐のために、少なくとも 1 つ以上のレジスタの値を壊すか、分岐の中継点を作る必用があります。

- 3 ) 代替えベクタ領域は、ROM モニタの管理領域として保護されているため、プログラムのダウンロードで書き換えることは出来ません。したがって、ソース・プログラム上ベクタ領域を独立したセクションとして定義し、リンク時のパラメータによりそのセクションを代替えベクタ領域に割り付ける方法も考えられますが、この方法はダウンロードに失敗してしまうため使用できません。

- 4 ) 割り込み関係を含む全てのペリフェラルは、ボード上のリセット・スイッチによってのみ初期化されます。したがって、一端プログラムを実行した後に、プログラムを再ロードして動作させる場合、前のプログラム実行による影響がペリフェラル上に残ってしまいます。したがって、ペリフェラルを使用するプログラムの場合、一端プログラムを動作させ、再度プログラムを始めから動作させる場合は、rteserv をディスコネクトし、RTE-V852/3-PC のリセット・ボタンを押し、rteserv を再コネクトする、という手順を踏んで下さい。

- 5 ) プログラムの先頭で一端 DI ( 割り込み禁止 ) 状態にしてから、ペリフェラルやベクタの設定をした後、EI ( 割り込み許可 ) 状態にするようにして下さい。

#### 14.3. ブレーク・ポイント使用に関する制限事項 / 注意事項

ブレーク・ポイントを割り込み処理ルーチン内に設定しブレークさせることも出来ますし、その後割り込み処理ルーチン内をシングル・ステップすることも可能です。しかしその場合、下記に示す制限事項 / 注意事項がありますのでご注意下さい。

- 1 ) ブレーク中は全てのマスカブル割り込みは受け付けません。

- 2 ) シングル・ステップ機能は、次の命令にテンポラリ・ブレーク・ポイントを設定する方式を取っています。したがって、EI ( 割り込み許可 ) 状態のユーザ・プログラムをシングル・ステップする場合、シングル・ステップ中にも割り込みを受け付けます。したがって、シングル・ステップでも、ブレーク・ポイントに関する注意事項に気をつけなければなりません。

- 3 ) シングルステップによって割り込み処理ルーチンから抜けることは出来ません ( 具体的には、割り込みルーチンの最後の "}" でのシングルステップが出来ません )。 同様に、iret 命令のシングルステップも出来ません。

- 4 ) デバッガの "Return" 機能で、割り込み処理ルーチンから元のルーチンへ戻ることは出来ません。

5 ) RTE-V852/3-PC では、プログラムの実行がブレーク・ポイントに達してから、実際にブレークするまでに時間がかかります（追補マニュアル No.2 参照）。このため、EI（割り込み許可）状態の位置に設定されたブレーク・ポイントにプログラムの実行が達した場合、実際にブレークする前に割り込みを受け付けてしまうことがあります。

この受け付けた割り込み処理ルーチン内にもブレーク・ポイントが設定されていた場合、こちらのブレーク・ポイントでブレークします。同様に、このブレーク・ポイント位置が EI 状態の場合、より優先順位の高い割り込みを受け付けることもあります。

## 15. ブレーク・ポイント

### 15.1. ブレーク・ポイントの実現方法

一般的な CPU には、ブレーク・ポイントに使用できる、最小命令長と同じ命令長を持つ命令があります。この様な命令は、ブレーク・ポイント命令とか Trap 命令と呼ばれる事が多い様です。

しかし残念ながら、V850 系の CPU にはブレーク・ポイントに使用できる命令がありません。Trap 命令はありますが、命令長が 4 バイトのため、最小命令長の 2 バイトより長くなってしまっています。

この様に最小命令長より長い命令をブレーク・ポイント用の命令として使用した場合、不具合が発生する可能性があります。不具合については詳しくは説明しませんが、例えばブレーク・ポイントを設定する番地に 2 バイト命令があり、その番地の次の命令に JMP してくる可能性がある場合などが考えられます。

RTE-V852/3-PC では、より安全なブレーク・ポイントを実現するために、次の様な手法でブレーク・ポイントを実現しています。

- 1 ) ブレーク・ポイント用の命令として、Branch-myself 命令（バイナリで 0x8505 の相対で ±0 番地への分岐命令）を使用する。

- 2 ) Multi 用 ROM モニタで使用しているインターバル・タイマ割り込みが発生した時の戻り番地の命令が 0x8505 であり、その番地がブレーク・ポイント・リストにある場合、ブレークしたものとして扱う。

インターバル・タイマの割り込みは、プロファイラ周期を決定するために用いられているものであり、その割り込み間隔はベースボード上の SW1 で設定できます。デフォルトでは、60Hz になっています。

### 15.2. 制限事項

前節で説明した様なブレーク・ポイント方式を採用しているため、次の様な制限事項があります。

- 1 ) インターバル・タイマ割り込みを停止（禁止）できません。

- 2 ) プログラムがブレーク・ポイントに達してから、実際にブレークするまでに時間がかかります。この間の時間は最大でインターバル・タイマの割り込み周期になります。通常この時間は問題になりませんが、マスカブル割り込みを使用したアプリケーションの場合に 3 ) のような問題が発生する事が考えられます。

- 3 ) ブレーク・ポイントに達してから、実際にブレークするまでの間に、受け付け可能なマスカブル割り込みが発生すると、その割り込みを受け付けてしまいます。

また、その割り込みの処理ルーチン内にもブレーク・ポイントが設定されている場合、このブレーク・ポイントでブレークします。更にこのブレーク・ポイントでブレークを待っている間に、より高い優先順位の割り込みが入る場合もあります。

- Memo -

RTE-V852-PC ユーザーズ・マニュアル

M662MNL02

*Midas lab*