***KIT-VR5400-TP***

**ユーザーズ・マニュアル**

***RealTimeEvaluator***

## ■ ソフトウェアのバージョンアップ

- 最新のRTE for Win32 (Rte4win32)は、以下のサイトよりダウンロードできます。

[http://www.midas.co.jp/products/download/program/rte4win\\_32.htm](http://www.midas.co.jp/products/download/program/rte4win_32.htm)

## ■ ご注意

- KIT-VR5400-TP(プログラム及びマニュアル)に関する著作権は株式会社マイダス・ラボが所有します。

- 本プログラム及びマニュアルは著作権法で保護されており、弊社の文書による許可が無い限り複製、転載、改変等できません。

- お客様に設定される使用権は、1ライセンスにつき、1台のシステムにおいてのみ使用できるものです。1ライセンスで同時に2台以上のシステムでのご利用はできません。

- 本製品は、万全の注意を持って作製されていますが、ご利用になった結果については、販売会社、及び、株式会社マイダス・ラボは一切の責任を負いかねますのでご了承ください。

- 本プログラム及びマニュアルに記載されている事柄は、予告なく変更されることがあります。

## ■ 商標について

- MS-Windows、Windows、MS、MS-DOSは米国マイクロソフト・コーポレーションの商標です。

- そのほか本書で取り上げるプログラム名、システム名、CPU名などは、一般に各メーカーの商標です。

## 改訂履歴

|          |            |                                                                |

|----------|------------|----------------------------------------------------------------|

| Rev.0.80 | 1999-7-19  | 暫定初版                                                           |

| Rev.0.81 | 1999-7-26  | 修正                                                             |

| Rev.0.82 | 1999-8-11  | 修正：端子マスクについて                                                   |

| Rev.1.00 | 1999-9-24  | 正式初版：<br>* ENVコマンドへのパラメータ追加<br>* cacheinit, cacheflush コマンドの追加 |

| Rev.2.00 | 2000-3-4   | 2版：RTE-1000-TP本体への対応に伴う、改版                                     |

| Rev.2.10 | 2000-3-23  | NSPB/NSBPD, NROM/NROMDコマンドの追加                                  |

| Rev.2.11 | 2000-10-20 | 6章 機能上に注意に追記                                                   |

| Rev.2.12 | 2001-5-20  | download site 情報の変更                                            |

## 目次

|                            |    |

|----------------------------|----|

| 1 . はじめに.....              | 4  |

| 2 . ハードウェア仕様.....          | 5  |

| エミュレーション部.....             | 5  |

| 3 . RTE FOR WIN32 の設定..... | 6  |

| CHKRTE2.EXEの起動.....        | 6  |

| 4 . 初期設定コマンド.....          | 8  |

| MULTIを使用する場合.....          | 8  |

| PARTNERを使用する場合.....        | 8  |

| 5 . インターフェース仕様.....        | 9  |

| ピン配置表.....                 | 9  |

| コネクタの型番.....               | 9  |

| 配線長.....                   | 9  |

| 基板レイアウト図.....              | 10 |

| 6 . 注意事項.....              | 11 |

| 操作上の注意.....                | 11 |

| 機能上の注意.....                | 11 |

## 1. はじめに

KIT-VR5400-TPは、RTE-100-TP、またはRTE-1000-TPを使用して、NEC製のRISCプロセッサ、VR5432を搭載したシステムをインサーキット・エミュレーション・デバッグするためのソフトウェアです。

本マニュアルは、当KITのご使用方法について記述したものです。ご使用にあたりましては、本体となります RTE-100-TP、RTE-1000-TPのマニュアルと合わせてお読みください。

本製品には下記のものが付属します。最初に付属品の確認を行なってください。

- RTE for Win32 (Rte4win32) Set Up CD

- ユーザーズマニュアル（本書）

- ライセンス設定シート

## 2. ハードウェア仕様

### エミュレーション部

|                             |                                           |

|-----------------------------|-------------------------------------------|

| 対象デバイス                      | VR5432                                    |

| 使用するRTE-TPの形式               | RTE-1000-TP                               |

| エミュレーション機能                  |                                           |

| 動作周波数                       | 167MHz                                    |

| インターフェース                    | JTAG/N-Wire                               |

| *7 JTAG CLK                 | 100KHz - 25MHz                            |

| ブレーク機能                      |                                           |

| 実行アドレஸイベントによるブレーク(*1)       | 1                                         |

| アクセスイベントによるブレーク設定(*2)       | 1                                         |

| S/Wブレークポイント                 | 100                                       |

| ステップブレーク                    | 可                                         |

| マニュアルブレーク                   | 可                                         |

| トレース機能(*3)                  |                                           |

| トレースデータバス                   | 4bit                                      |

| トレースメモリ                     | 4bit × 128Kword                           |

| 実行アドレஸイベントによるトリガ設定(*1)      | 1                                         |

| アクセスイベントによるトリガ設定(*2)        | 1                                         |

| 外部入力信号によるトリガ設定              | 1                                         |

| トレースディレイ                    | 0 - 1FFFFh                                |

| *7 トレースクロック                 | 77MHz(max)                                |

| *7 タイムタグ                    | 100nS - 30h                               |

| 逆アセンブルトレース表示機能              | 有                                         |

| ROMエミュレーション機能               |                                           |

| *7 メモリ容量                    | 8M - 32Mバイト                               |

| *7 アクセスタイム                  | 40nS(バースタイクル:35nS) (*4)                   |

| *7 動作電圧                     | 1.8V - 5V (*5)                            |

| *7 電気的条件                    | LV-TTL, 5Vトロント (*6)                       |

| エミュレーション可能なROM数             |                                           |

| DIP-32pin-ROM(8bit-ROM)     | 4 (max)                                   |

| DIP-40/42pin-ROM(16bit-ROM) | 2 (max)                                   |

| *7 拡張16BIT-標準ROMコネクタ        | 2 (max)                                   |

| エミュレーション可能なROMの容量(bit)      |                                           |

| DIP-32-ROM(8-bit bus)       | 1M, 2M, 4M, 8M(27C010/020/040/080)        |

| DIP-40-ROM(16bit-bus)       | 1M, 2M, 4M(27C1024/2048/4096)             |

| DIP-42-ROM(16bit-bus)       | 8M, 16M(27C8000/16000)                    |

| *7 拡張16bit-標準ROM(16bit-bus) | 1M, 2M, 4M, 8M, 16M, 32M, 64M, 128M, 256M |

| バス幅指定(bit)                  | 8/16/32                                   |

| 端子マスク機能                     | NMI, INT                                  |

\*1. ブレークとトリガ用の実行アドレஸイベントは兼用です。

\*2. ブレークとトリガ用のアクセスイベントは兼用です。

\*3. トレース中は、実行速度が低下します。

\*4,5,6. 拡張16bit標準 ROMケーブル:CBL-STD16-32M + DIP40/42アダプタを使用した場合の値です。

\*7. RTE-1000-TPを使用した場合の仕様です。RTE-200-TPの仕様はこれと異なります。

RTE-200-TPをご使用の場合は、RTE-200-TPのマニュアルを参照ください。

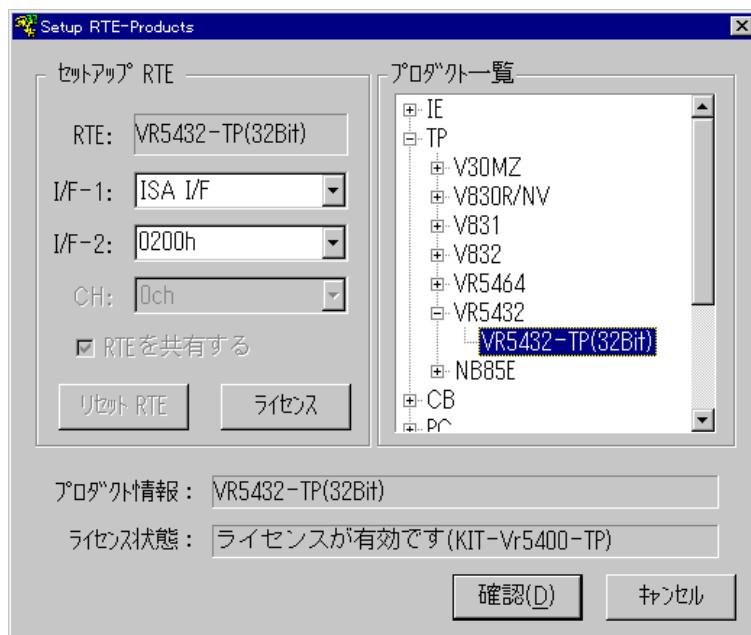

### 3. RTE for WIN32の設定

『RTE for WIN32』の設定について説明します。

#### ChkRTE2.exeの起動

ユーザシステムとの接続を完了し、全ての機器の電源が投入された状態で ChkRTE2.exe を起動し、『RTE for WIN32』の環境設定を実施してください。『RTE for WIN32』の環境設定は、新規にハードウェアを設置した時に必ず1回は実施してください。

#### < RTEの設定 >

#### < RTEの選択 >

プロダクト一覧より、TPの下層にあるVR5432-TPを指定してください。

#### < I/F-1, I/F-2の選択 >

使用するホストインターフェースに合ったものをプルダウンメニューから選んで指定してください。（画面は、RTE-PCATを200hに割り付けた場合です）

#### < ライセンス >

ボタンをクリックして、KITに添付のライセンス設定シートを見て、ライセンスの設定を行ってください。詳細は、『RTE for WIN32』のマニュアルを参照してください。

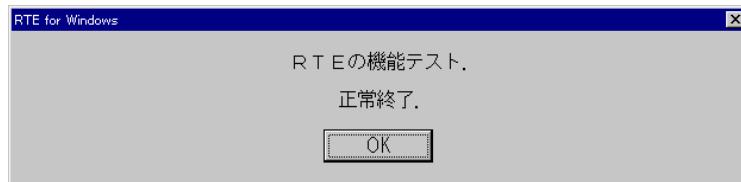

## &lt;機能テスト&gt;

機能テストは、ユーザシステムとの接続が正しく行われ、デバッグ可能な状態になっていることが必要です。RTEの設定後、画面の指示に従い機能テストを実施すると、正常終了時に下記のダイアログが表示されます。この状態になれば、デバッガからの制御が可能です。

途中でエラーになる場合は、ユーザシステムに障害があるか、JTAG/N-Wireケーブルが正しく接続できていない可能性がありますので、それらの確認を行ってください。

**CHKRTE2.EXE の機能テストは、RTE-200-TP、またはRTE-1000-TP とユーザシステムが接続され、両方に電源が入っている状態で行ってください。**

## 4. 初期設定コマンド

デバッグを開始する前に、ユーザシステムのハードウェアに依存した初期設定が必要です。初期設定の為のコマンドとして以下が用意されていますので、必ず、正しく設定してからご使用ください。

### Multiを使用する場合

ターゲットウインドウ内で以下の内部コマンドを使用します。

#### ENVコマンド

- ・端子マスクの指定

- ・JTAGクロックの指定

- ・キャッシュ処理の為のワーク領域の指定

- ・高速ダウンロード・モードの指定

- ・その他

#### ROMコマンド

- ・ROMのエミュレーション条件の指定

#### NC/NCDコマンド

- ・デバッガ内でのデータキャッシュ処理領域の指定

#### NSPB/NSPBDコマンド

- ・ソフトブレーク禁止領域の指定

#### NROM/NROMDコマンド

- ・強制ユーザ領域の指定

### PARTNERを使用する場合

設定用のダイアログを使用します。

#### CPU環境設定ダイアログ

- ・端子マスクの指定

- ・JTAGクロックの指定

- ・キャッシュ処理の為のワーク領域の指定

- ・高速ダウンロード・モードの指定

- ・その他

#### エミュレーションROM設定ダイアログ

- ・ROMのエミュレーション条件の指定

#### NC/NCDコマンド

- ・デバッガ内でのデータキャッシュ処理領域の指定

#### NSPB/NSPBDコマンド

- ・ソフトブレーク禁止領域の指定

#### NROM/NROMDコマンド

- ・強制ユーザ領域の指定

## 5. インターフェース仕様

JTAG/N-Wireインターフェースのコネクタの仕様を以下に説明します。

ピン配置表

| Pin番号 | 信号名                | 入出力 (User Side) | 処理(User Side)                                       |

|-------|--------------------|-----------------|-----------------------------------------------------|

| A1    | TRCCLK             | Output          | 22-33 シリーズ抵抗(推奨)                                    |

| A2    | TRCDATA0           | Output          | 22-33 シリーズ抵抗(推奨)                                    |

| A3    | TRCDATA1           | Output          | 22-33 シリーズ抵抗(推奨)                                    |

| A4    | TRCDATA2           | Output          | 22-33 シリーズ抵抗(推奨)                                    |

| A5    | TRCDATA3           | Output          | 22-33 シリーズ抵抗(推奨)                                    |

| A6    | TRCEND             | Output          | 22-33 シリーズ抵抗(推奨)                                    |

| A7    | DDI                | Input           | 4.7K-10K プルアップ                                      |

| A8    | DCK                | Input           | 4.7K-10K プルアップ                                      |

| A9    | DMS                | Input           | 4.7K-10K プルアップ                                      |

| A10   | DDO                | Output          | 22-33 シリーズ抵抗(推奨)                                    |

| A11   | DRST-              | Input           | オープンまたは、外部回路を通し、ColdReset*へ接続(TPから負論理のリセット信号を出力します) |

| A12   | Rmode*/<br>BkTG10* | Input/Output    | 4.7K-10K プルアップ                                      |

| A13   | NC.                | -----           | オープン                                                |

| Pin番号  | 信号名   | 入出力 (User Side) | 処理(User Side) |

|--------|-------|-----------------|---------------|

| B1-B10 | GND   | -----           | GNDに接続        |

| B11    | NC.   | -----           | オープン          |

| B12    | NC.   | -----           | オープン          |

| B13    | +3.3V | -----           | +3.3Vに接続      |

コネクタの型番

メーカー : KEL

型番 : 8830E-026-170S (ストレート)

8830E-026-170L (ライト・アングル)

8831E-026-170L (ライト・アングル、固定金具付き)

配線

1. CPUからコネクタまでの配線は極力短くなるようにしてください。

(100mm以下を推奨します)

2. CPUからの出力信号は、CPUのI/Oと同一電源を供給した高速CMOSバッファを介し、コネクタへ接続すること推奨します。

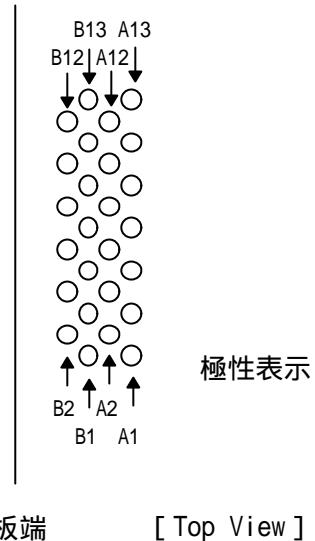

基板レイアウト図

基板上のコネクタの物理的なレイアウトを以下に示します。

基板端

[ Top View ]

## 6. 注意事項

KIT-VR5400-TPを使用する上での注意事項を以下にまとめます。

### 操作上の注意

- 1) 本機の電源が切れている状態で、ユーザシステムの電源を入れないでください。故障の原因となります。

- 2) 本機は、CPU内部のデバッグ制御回路を外部から制御するものです。そのため以下の条件が満たされない場合、正しく動作しません。

- \* ユーザシステムとN-Wireケーブルが接続されていること。

- \* ユーザシステムの電源が投入され、CPUが正しく動作できる状態にあること。

### 機能上の注意

- 1) リアルタイムトレースに関して

- \* リアルタイムトレースの逆アセンブル表示は、CPUからの分岐情報をもとに、トレース表示のコマンドを発行した時点でメモリの内容を読み出して行っています。その結果、ユーザシステムのRAM上に配置されたプログラムの逆アセンブル表示は、実行後にRAMの内容が変更（暴走等による誤った書き込みを含む）された場合、正しい実行履歴を表示することができません。また、分岐情報に誤りがあった場合も、正しく解析表示することはできません。

- \* ブレークポイントから実行した場合、実行開始アドレスの1命令分の実行がトレースに入りません。

- \* トレース中、トリガが成立した場合とディレイモードの状態でブレークした場合は、ブレークした時点でトレースは終了します。

- 2) ハードウェアブレークポイント（EVEコマンドとROM領域のブレークポイント）は、8バイトのバウンダリで機能します。

>> 通常、指定した命令の次の命令でもブレークします。

- 3) キャッシュをLOCKした状態でのデバッグは行えません。LOCKした場合、その領域でのブレークやステップ実行、メモリの書き換えが異常になる可能性があります。

- 4) その他、KITのリリースノートを必ず参照してください。